基于FPGA的可配置FFT_IFFT处理器的设计与实现*

梁赫西 ,陈佑红 ,郑朝霞

(1.湖北师范学院 教育信息与技术学院,湖北 黄石435002;2.华中科技大学 电子科学与技术系,湖北 武汉430074)

基于FPGA的可配置FFT_IFFT处理器的设计与实现*

梁赫西1,陈佑红2,郑朝霞2

(1.湖北师范学院 教育信息与技术学院,湖北 黄石435002;2.华中科技大学 电子科学与技术系,湖北 武汉430074)

设计实现了一种用于P2P移动无线通信手持终端产品。该设计采用优化的单碟形4路并行结构,兼容802.11g协议,可配置完成64点、256点、1 024点的FFT-IFFT处理器,设计以Xilinx公司的Virtex-2系列的XC22V500芯片为硬件平台。通过大量实际信号与数据的联合调试,表明了设计的正确性及实用性。

可配置;FFT-IFFT;P2P;无冲突地址

目前,正交频分复用OFDM(Orthogonal Frequency Division Multiplexing)技术已经成为未来宽带无线接入系统的基本实现技术之一,其抗多径衰落和高频带利用率的优点被广泛应用于无线通信系统中,是解决高速数据在无线信道中传输的首选方案[1]。

FFT_IFFT处理器是OFDM系统中数据处理的核心单元,是OFDM系统中数据正交调制和解调的关键。本文设计实现了一种用于P2P移动无线通信手持终端产品,采用单碟形4路并行结构,兼容802.11g协议,可配置FFT_IFFT处理器,在处理速度、实现面积、功耗方面均满足802.11g系统及手持移动无线通信终端的要求。

1 基4-FFT算法的数学模型

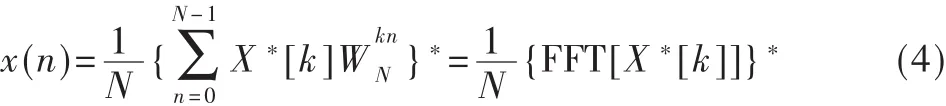

对于N点有限长序列的FFT可表示为[2]:

对式(1)按基4时域抽取可得:

式(2)经等价的变量代换,并利用旋转因子的性质可表示为:

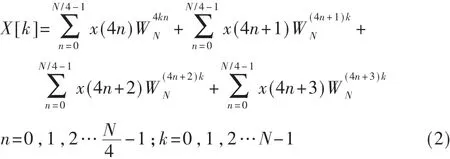

式(4)表明首先对 X[k]取共轭,然后对其进行 FFT变换,对其结果再取一次共轭,乘因子1/N,这样就实现了IFFT与FFT处理模块的复用。

N点有限长序列的IFFT可表示为:

2 可配置FFT/IFFT处理器设计

2.1 FFT/IFFT处理器整体结构

可配置FFT/IFFT处理器整体结构如图1所示。图中,基4蝶形单元主要完成输入的4路并行计算。OFDM数字基带数据流需要高速连续处理[3],故FFT处理系统在输入、输出均采用了乒乓处理,共需要4组存储单元,一组存储单元需要4块RAM;RAM地址产生单元主要生成存储单元写入及读出数据的地址,数据选择模块主要完成了乒乓操作RAM的数据选择;ROM及其地址产生单元主要在控制单元的控制下将旋转因子送入蝶形单元,配置单元控制不同点数的数据流操作及其相应地址配置。

2.2 FFT/IFFT可配置方案

由基4算法分析可知,要分别完成 1 024、256、64点的 FFT计算,需要的迭代级数分别为 5、4、3级。由于1 024点的FFT运算可分解为4个256点的FFT运算,而256点的FFT运算又可分为4个64点的FFT运算,64点的FFT运算经过3级迭代就可求出。可以通过简单的模式控制实现多点数的配置,如图2所示。其中5级蝶形计算单元,每级蝶形单元结构一致,采用顺序蝶形计算,当选择模式0时,数据直接送入第一级,进行1 024点的5级运算;选择模式1时,数据通过选择器跳过第1级,数据送入第2级,从而完成256点的4级迭代运算;选择模式2时,数据通过选择器跳过第1级和第2级,数据送入第3级,从而完成64点的三级迭代运算。这样就可以正确简单地实现系统要求的配置要求。

2.3 基本蝶形运算单元设计

蝶形运算单元的设计是整个FFT/IFFT处理器设计的关键。完成蝶形运算的一次复数乘法包含4次实数乘法和2次实数加、减法,如果将乘数扩大1位,可将计算化简为3次实数乘和5次实数加/减法。为了提高处理速度,本设计采用四级流水线处理方式,有效地减小了关键路径时延。蝶形单元的数据从RAM输入及输出到RAM需要2个时钟周期,这里引入2级流水;对输入数据的实部和虚部分开并行计算,一次复数乘法只需3个乘法累加器即可完成,用4个加法器及4个减法器即可完成基4蝶形单元后续数据处理,再次引入二级流水。整个蝶形单元处理时间为4个周期,采用四级流水线结构后,以较小的资源代价有效提高了处理器的时钟频率。

2.4 乒乓RAM设计

为了满足无线移动通信要求,实现对连续数据流和突发数据流的处理,本文设计的FFT/IFFT处理器采用了输入、输出双乒乓结构,保证了系统高吞吐率的要求。

设计共使用 4组 RAM(RAM0~RAM3),每组 RAM划分为4块存储器。输入数据写入RAM0组中的4块存储器,写完后开始写入RAM1,与此同时,从RAM0组中读出数据送入蝶形单元进行计算,其结果按照同址计算规则写回相应的地址,直到M级蝶形运算完成后,最终的计算结果写入RAM2。RAM2写满后,即可从RAM2读出计算结果,同时RAM1组中的数据将被读出送入蝶形单元进行运算,其运算结果按照同址运算规律送回RAM1存储,M级蝶形运算完成后,最终结果写入RAM3组,RAM3写满后即可从中读出运算结果。

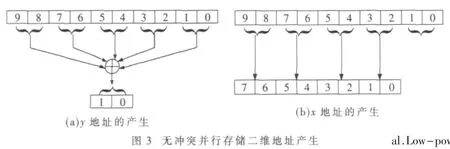

2.5 无冲突并行地址设计[4]

4路并行数据处理结构需要保证每次读取的一组数据分别存储在不同的RAM中,否则在数据读取时会产生地址冲突[5]。本设计中RAM地址采用二维地址,其中地址x表示每块RAM中数据地址,y表示数据来自RAM块的标号。

设处理器数据输入序号用N表示,则N可用四进制表示为:

3 FPGA实现及测试分析

本文FFT/IFFT处理器采用Verilg硬件语言描述,在Mentor公司的Modelsim仿真平台上进行了RTL功能仿真及时序仿真,其结果与Matlab仿真结果进行比较显示正确。处理器采用了Xilinx公司Virtex-Ⅱ xc22v500芯片进行了验证,在SMIC COMS 0.18 μm工艺下对设计的处理器进行了综合仿真。结果显示:完成64点16 bit符号数复数FFT运算只需要50个时钟周期,完成256点FFT运算需要256个时钟周期,最大时钟频率可以达到167 MHz,处理器的单元核心面积为1.4 mm2。设计完全满足了无线移动手持终端设备高速小面积的设计要求。

[1]BECCHETI L.Enhancing IP service provision over heterogeneous wireless networks[J].A Path toward 4G.IEEE Communication Magazine,2001,39(8):74~81.

[2]程佩青.数字信号处理教程[M].北京:清华大学出版社.2004:138-150.

[3]JOHNSON L G.Conflict free memory addressing for dedicated FFT hareware[J].IEEE Transactions On Circuits and System,Analog And Digital Signal Processing,1992,39(5):99-105.

[4]TROY A,MAHARATNA K,KRSTIC M,et al.Low-power VLSI implementation of the inner receiver for OFDM-based WLAN system[J].IEEE Transactions on circuits and systems,2008,55(2):672-686.

[5]FOSTER M,TURNER A,SHARPING J,et al.Broad-band optical parameric gain on a silicon photonic chip[J].Nature Photon,2006,441:960-963.

Design and implementation of FFT_IFFT processor based on FPGA

Liang Hexi1,Chen Youhong2,Zheng Zhaoxia2

(1.College of Educational Information and Technology,Hubei Normal University,Huangshi 435002,China;2.Department of Electronic Science and Technology,Huazhong University of Science and Technology,Wuhan 430074,China)

In this paper,a configurable FFT-IFFT processor adopting optimized single butterfly 4 parallel structure is proposed to implement 64/256/1024 points operation.This processor is designed for a P2P wireless terminal compatible with 802.11g protocol.The hardware developing platform is Virtex-II series FPGA XC22V500 of Xilinx.The design is verificated to be correct and practical via joint debugging with large amounts of real signals and data.

configurable;FFT-IFFT;P2P;non-conflicting address

TN92

A

0258-7998(2012)03-0057-03

*基金支持:湖北省自然科学基金项目(2010CDB02705)

2011-10-31)

梁赫西,男,1982年生,讲师,硕士,主要研究方向:数字集成电路设计。

陈佑红,女,1986年生,硕士,主要研究方向:数字集成电路设计。

郑朝霞,女,1975年生,讲师,博士,主要研究方向:数字集成电路设计。