基于FPGA的扩频信号发生器的研究与设计*

王茂林 杨合圣

(92823部队 三亚 572021)

1 引言

近些年,随着CMOS集成电路制作工艺的不断成熟与发展,FPGA器件集成度越来越高,价格不断下降,并以其性能高、可靠性好、以及现场修改、现场验证、现场实现的数字系统单片化的应用趋势而日益成为电子设计自动化(EDA)领域的热门技术。特别是FPGA高速、并行的处理能力,使其能够快速复杂地处理通信信号。

2 基本原理

扩频信号发生器[1~3]将要发送的信息用伪随机序列扩展到一个很宽的频带上去,在接受端与发射端用相同的伪随机序列对接受到的扩频信号进行解扩处理,恢复出原始信息。

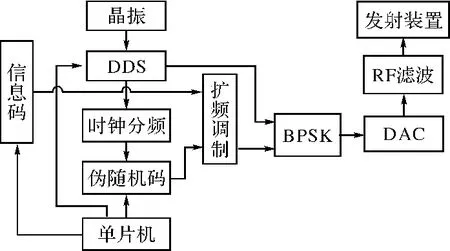

3 总体设计方案

根据扩频信号发生器的基本工作原理,我们给出了一套总体设计方案,如图1所示。信号发生器主要由单片机控制系统、载波发生器、扩频伪随机码发生器、扩频伪码编码器和BPSK扩频信号调制器组成。单片机通过逻辑接口对频率合成器、信息码、伪码发生器进行控制。伪随机码[4]由载波频率分频得到,信息码与伪随机码进行扩频调制。频率合成器产生的正弦波与扩频伪随机码进行二进制移相键控调制,调制后的数字信号转化为模拟信号后通过滤波器输出给发射机。

图1 扩频发射系统总体设计

其中,DDS由相位累加器、查询表ROM和数模转换器DAC所组成。相位累加器由A位加法器与A位寄存器组成。DDS查询表ROM所存储的数据是每一个相位所对应的二进制数字正弦幅值,在每个时钟周期内,相位累加器输出A位对其寻址,最后输出为该相位对应的二进制正弦幅值列表序列。数模转换器DAC作用是将数字信号转换成所需的模拟量信号。

4 DDS的原理图及其各波形特点

在参考时钟的控制下,相位累加器对对频率控制K进行相位累加,得到的相位序列φ(n)对波形存储器寻址,使之输出相对应的幅度码,经过数模转换器得到对应的梯形波,最后经过低通滤波器得到连续变化的所需频率波形。

相位序列的实现实际上是一个相位累加的过程,可以用相位累加器来实现此过程。相位累加器结构如图2所示。

图2 相位累加器结构图

相位累加器具体的工作过程为:一个时钟脉冲到来时,数字全加器将上一个时钟周期内寄存器所寄存的值与输入参数K相加,其和存入寄存器当作相位累加器的当前相位值输出,K为一个时钟周期内相位的增量。

DDS[5~7]是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。DDS芯片中主要包括频率控制寄存器、高速相位累加器和正弦计算器三个部分。频率控制寄存器可以串行或并行的方式装载并寄存用户的频率控制码;相位累加器根据频率控制码在每个时钟周期内进行相位累加,得到一个相位值;正弦计算器则对相位值计算数字化正弦波幅度。DDS芯片输出的一般是数字化正弦波,因此还需要经过高速D/A转换器和低通滤波器才能得到一个可用的模拟频率信号,DDS原理如图3所示。

图3 波形输出DDS原理框图

5 BPSK 调制[8~10]

二进制移相键控(BPSK)方式是受键控的载波相位按基带脉冲而改变的一种数字调制方式。这种以载波的不同相位直接去表示相位数字信息的相位键控,通常被称为绝对移相方式。

在数学上它可以用载波与一个取值为0,1的伪随机码C(t)的函数的乘积来表示。载波相位随调制信号1或0而改变,通常0°与180°。

对载波调制进行二进制相移键控有两种方法:直接调相法和相位选择法。直接调相法是用伪随机序列与载波直接相成。由于直接调相精度不高,因此本信号发生器采用相位选择法对载波进行调制。即用伪随机码去控制电路,选择不同相位的载波输出,载波调制原理如图4。

图4 载波调制示意图

由载波调制示意图可知当调制码为1时,载波正常输出,当调制码为0时,载波翻转。

6 扩频调制模块设计

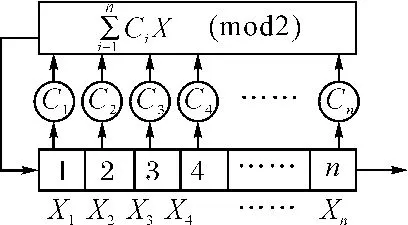

m码[12]的实现:m码生成器由移位寄存器,模二加法器与反馈线路组成图5是一个m码生成器的原理图,假设有n个移位寄存器它的状态Xi经Ci相乘后模二相加。

图5 m码生成器原理图

该电路如图6所示,由4个D触发器,1个或门,1个异或门,1个脉冲输入,1个m码输出。4个触发器实现移位功能,当有1个cp脉冲来临时前一个D触发器Q端值被送入下一个触发器D端实现了移位。若初始为0000则输出为001111010110。用maxpulsII对电路进行波形仿真得图7。

图6 扩频码实现电路图

图7 扩频码实现电路的仿真波形

由仿真波形可以看出与理论值相符,此电路可以实现m码。由于本电路周期不长,要增加其随机性可增加移位寄存器个数。

7 结语

扩频通信是现代通信系统重要技术,可以显著提高通信系统抗干扰的能力,特别是抗干扰的能力。第三代移动通信的三个国际标准都采用扩频技术。

由于FPGA实现是一个完整的硬件构架,其中的电路由门电路实现,比传统的扩频信号发生器处理速度快1.5~2倍,同时采用流水线技术,提高了系统并行处理的能力。并且系统可以通过程序来修改和升级,具有很大的灵活性。由于所有模块都集成在一个芯片中,提高了系统的稳定性和可靠性。

[1]刘小伟,霍静.扩频通信技术及其在无线局域网中的应用[J].计算机与现代化,2007(6):58-61.

[2]申彦春,吴铮,赵庆利.基于扩频通信系统接收同步技术的研究[J].仪器仪表与分析监测,2012(2):12-15.

[3]薛敦伟,周旭平.扩频通信系统中自适应陷波滤波器的性能仿真研究[C].宇航学报,2012,33(4):500-506.

[4]陈海龙,李宏.基于MATLAB的伪随机序列的产生和分析[J].计算机仿真,2005(5):98-100.

[5]邓腾,吴校生,周晓玲.基于DSP和DDS技术相位及频率严格可调的多路同步信号发生器[J].电子器件,2012,35(2):163-167.

[6]陈迪,刘旺锁,姚直象.基于DDS的声呐信号发生器设计与实现[J].国外电子测量技术,2012,31(5):74-76.

[7]赵丽娜,郭宝增.基于FPGA的DDS基本信号发生器的设计[C].电子设计工程,2012,20(12):190-192.

[8]孙登高,施展.基于FPGA的QPSK与BPSK调制系统仿真[J].光学仪器,2011,33(5):70-74.

[9]高磊,陈志强,吴黎慧,等.基于FPGA的BPSK调制与解调器设计[J].电子测试,2011(6):66-67.

[10]佟景泉,刘悦,邢东峰.基于FPGA的DDS设计与实现[J].铁路计算机应用,2012,21(3):39-41.

[11]张海超,陈丹.一种基于栈分配的软件水印算法[J].计算机与数字工程,2012(8).

[12]杨梅,张志刚,曲仁秀,等.基于m序列的直接序列扩频CDMA通信系统的仿真研究[C]//长江大学学报自然科学版:理工卷,2012,9(5):154-156.