AVS环路滤波器的FPGA优化及实现

刘 博,王永霞,张 刚

(太原理工大学通信与嵌入式系统实验室,山西太原 030024)

AVS环路滤波器的FPGA优化及实现

刘 博,王永霞,张 刚

(太原理工大学通信与嵌入式系统实验室,山西太原 030024)

针对AVS环路滤波的算法原理,用VHDL语言完成了在FPGA硬件平台上的设计和仿真实现。环路滤波器对滤波数据的存储结构进行了合理的安排,用连续地址和跳变地址相结合的方式读取数据,并实现了读取数据的同时并行进行计算操作,减少了环路滤波所占用的时钟周期,提高了计算效率。该设计基于Xilinx公司的Virtex-4平台实现,最高时钟频率可达到140 MHz,满足AVS实时编码要求。

AVS;环路滤波器;FPGA

AVS是我国自主提出的数字电视、IPTV等音视频编解码标准,其技术简洁,实现的复杂度较低,并且未使用国际标准中诸多专利而在成本上极具优势,受到人们越来越多的重视和关注[1]。FPGA可以方便地设计出硬件逻辑,满足系统开发的灵活性、便利性、实时性以及系统设计的可编程性要求。

AVS编码以宏块为单位,会在块的边界处产生数据的不连续,即“方块效应”[2]。为去除“伪边界”所导致的方块效应,需要加入环路滤波器。环路滤波明显地提高重构图像质量,同时环路滤波后作为参考帧使用[3]能提高预测效果,进而提高编码效率。

1 AVS环路滤波原理

AVS标准规定滤波操作大致分为三个步骤:第一,推导块边界阈值α、β;第二,判别边界滤波强度Bs;第三,根据不同的Bs进行相应的滤波操作。

根据滤波边界两个块的qp平均值qp,以及Alphacoffset和Betaoffset由式(1)和式(2)计算得到索引值IndexA和IndexB,再查表得到对应的α、β的取值。根据式(3)判别是否进行对该边界滤波计算。滤波强度主要由编码中残差的大小决定[4]。由于帧内预测涉及的参考像素较少,产生的残差会较大,因此对残差变换量化后的误差就大,块的边缘就可能存在较强的虚假边界。所以采用强滤波模式(Strong Filter),即Bs=2。相对于帧内预测,帧间预测则较准确,变换产生的残差较小,故边缘强度也较小,所以采用标准滤波模式(Normal Filter),即Bs=1。具体滤波强度判别采用如下方式:当边界两边的两个8×8块至少有一个属于帧内预测宏块时,则判断Bs为2;若当前帧为P或B帧图像,边界两边块的参考图像相同,并且两个块的运动矢量中有一个分量的差值大于或等于一个整像素,则判别Bs为1,否则Bs为0。

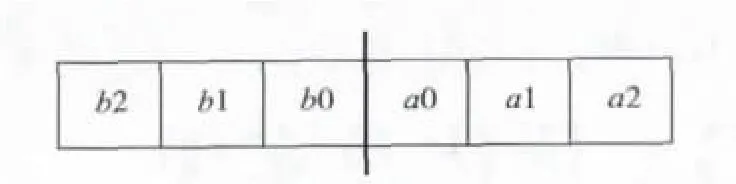

AVS根据边界强度Bs进行不同的滤波处理,如图1所示,其中粗线为两个块的边界。Bs=0时不滤波;Bs=1时用到边界两侧各三个像素点b2、b1、b0、a0、a1、a2;Bs=2 时用到边界两侧各两个像素点b1、b0、a0、a1[5]。

图1 水平或垂直滤波边界样本值

2 设计AVS环路滤波器

2.1 滤波器硬件设计方案

AVS标准规定除条带边界及图像边界之外,宏块的所有边界都需进行滤波。这里的宏块边界是指宏块内部所有8×8块的边界、当前宏块与其相邻宏块的上边界以及左边界。以宏块为单位进行环路滤波,按照光栅扫描顺序对各个8×8块依次处理。

对色度块和亮度块分别进行环路滤波,图2、图3所示是4∶2∶0格式的亮度块和色度块的滤波边界。按照从左到右顺序先滤波垂直边界,再按照从上到下的顺序滤波水平边界。

图2 亮度块滤波边界

图3 色度块滤波边界

当前宏块的边界样本值可能在之前的滤波过程中已经被修改,故当前宏块的滤波输入值应为这些被滤波修改的边界样本值,并且当前宏块滤波输出值可能会再次修改这些边界的样本值。

本文将环路滤波以8×8的子宏块为单位,在一个16×16的宏块中依次循环4次执行。在块数据存储时采用3块RAM存储器,如图4所示。其中RAM 1和RAM2分别用于存储当前块左边界三列和上边界三行各24个数据,RAM3用于存储当前块的64个数据。滤波垂直边界时,采用3个时钟周期同时读取RAM1和RAM3中滤波边界左右各3个点的数据,对其进行相应的判断和计算,最后得出滤波后的数据值,按照原地址再依次写回RAM1和RAM3中,作为后续块滤波边界的输入值,对于水平边界做同样的处理。与只用一块RAM相比较,这样的存储方式可以大大减少存取数据时所占用的时钟周期,提高了处理速度。

图4 数据存储的RAM结构

在本设计中,水平边界滤波和垂直边界滤波使用同一个计算单元,由于垂直边界滤波后的数据可能会作为水平滤波的输入样本值,如图3中宏块的左上角3×3个数据。因此只有在垂直边界滤波完成后才能滤波水平边界,决定了滤波边界的顺序性。在向RAM中存入数据时,由于按照水平方向RAM依次地址加1,故对垂直边界滤波时,可依次读出边界两侧连续地址的3个样本值。但当对水平边界滤波时,若仍采用读出边界两侧连续地址的3个数据值作为样本值的方法,则需要对当前块的数据块进行行列转置[6]。这里采用地址跳转的方式对样本数据值进行读取来代替数据块的转置,有效地缩减了数据行列转置过程中占用的时钟周期。如图5所示,在计算第n组滤波边界样本值的同时从RAM中读取第n+1组边界样本值;在输出第n组滤波计算值的同时开始第n+1组的滤波计算;使读数和计算能并行处理,提高了滤波的计算效率。

图5 环路滤波读数和计算的并行实现

2.2 滤波过程

如图6所示,状态机在开始时处于Stidle状态,表示状态空闲。当数据使能信号en=1时,表示有数据到来,此时状态机就进入Streceive状态,开始接收数据。接收的数据包括3部分,当前块数据、左边界三列数据以及上边界三行数据。数据接收完毕,计算块边界阈值α、β,判别滤波强度Bs值,选择滤波模式。Stver_read表示读取垂直边界两边的数据;在St_cal状态计算垂直边界滤波。当ver_cnt=8,即一个垂直边界的8组数据计算结束,通过Sthor_read状态读取水平边界两边的数据并在St_cal状态计算。由于对同一种滤波强度,其水平和垂直边界的计算过程是相同的,所以St_cal可以被反复调用。当前块所有边界滤波结束后在Sttransmit状态将滤波后得到的计算数据输出。

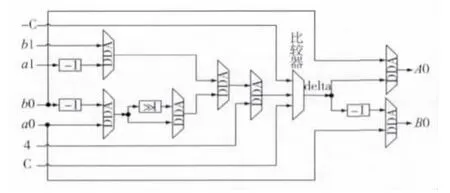

图7是Bs=1时色度滤波的具体硬件实现过程。计算时先对a0、b0两个点滤波,首先读取滤波边界各2个样本值a0、a1、b0、b1作为样本输入值,最后得到滤波计算输出值A0、B0。

图6 环路滤波器状态转移图

图7 Bs=1时滤波的硬件实现过程

若当前为亮度边界滤波,则还需对a1、b1两个点进行滤波,其计算过程与图6类似。滤波a1点时,只需将图6中输入数据的a1和a0,对应换成其经滤波运算后的输出值A0和B0;以及与b1和b0对应的输入换成b2和b1即可获得滤波输出A1。滤波b1点时,只需将图6中输入数据的a1和a0,对应换成a2和a1;以及与b1和b0对应的输入换成其经滤波运算后的输出值B0和A0即可获得滤波输出B1。

图8是Bs=2时色度滤波的具体硬件实现过程,数据输入方式与Bs=1时相同。进行亮度滤波a1点时,只需将输入值a1和a0互换即可得到滤波输出值A1;滤波b1点时,只需将输入值b1和b0互换即可得到滤波输出值B1。

图8 Bs=2时滤波的硬件实现过程

3 实验结果

本文在ISE 10.1环境下,使用VHDL语言设计并优化了AVS环路滤波器。硬件平台是Xilinx公司的Virtex-4系列的FPGA xc4vsx25。以8×8的色度块为例,在Bs=1、qp=36的情况下,图9是从AVS标准编码软件中截取的滤波结果,与图10中ModelSim仿真软件中得到的仿真结果一致。

图9 AVS标准编码滤波内存数据(截图)

图10 滤波仿真结果数据(截图)

资源利用情况如表1所示,整个滤波过程共占用434个时钟周期,其中输入滤波样本值和输出滤波计算结果各占112个周期,计算过程占210个时钟周期,最高频率能达140 MHz,能满足AVS实时编码要求。

表1 硬件资源利用

图11是对AVS的一个标准码流滤波前后的图像对比,从图像中可以直观地看到环路滤波的去块效应效果显著,经滤波后的图像质量有了明显的提高。

图11 滤波前后图像对比

4 结论

本文设计的AVS环路滤波器,以8×8块为单位进行滤波,采用3块片内RAM存储滤波数据,通过地址跳变完成滤波数据块的转置。采用数据读取与计算并行处理流水结构,节省了时钟周期,提高了计算效率和处理速度,能满足AVS实时编码高分辨率序列的要求。

:

[1]GB/T 20090.2—2006,先进音视频编码 第二部分:视频[S].2006.

[2]毕厚杰.新一代视频压缩编码标准:H.264/AVC[M].北京:人民邮电出版社,2005.

[3]黄友文,刘钧彬.AVS去块效应滤波器的一种硬件优化设计[J].江西理工大学学报,2011,32(2):70-72.

[4]林衡芝,张文军,高志勇,等.一种支持H.264与AVS的高效环路滤波器设计[J].电视技术,2011,35(11):31-35.

[5]张耀坤.基于FPGA的AVS编码器中帧内预测和环路滤波模块的设计与实现[D].济南:山东大学,2011.

[6]黄中华,支琤.基于FPGA的AVS环滤波器设计与实现[J].计算机工程,2007,33(6),222-224.

张 刚(1953— ),博士生导师,主研语音编码、视频编码、嵌入式系统等。

Optimization and Implementation of AVS Loop Filter on FPGA

LIU Bo,WANG Yongxia,ZHANG Gang

(Laboratory of Communication and Embedded System,Taiyuan University of Technology,Taiyuan 030024,China)

In this paper,design and simulation implementation of AVS loop filter are accomplished on FPGA hardware platform with VHDL language corresponding to relevant algorithm principles.For the loop filter designed,the storage structure of filter data is arranged reasonably,the data is read by means of combining contiguous address and jumps address together and computation operation is performed in parallel while reading data,reducing the clock cycles consumed by loop filtering and improving computation efficiency.This design is executed on Xilinx Virtex-4 with the maximum frequency up to 140 MHz,which satisfies the real- time encoding demand of AVS.

AVS;loop filter;FPGA

TN919.8

A

【本文献信息】刘博,王永霞,张刚.AVS环路滤波器的FPGA优化及实现[J].电视技术,2014,38(1).

国家自然科学基金项目(60772101)

刘 博(1988— ),女,硕士生,主研视频编解码算法及其硬件实现;

王永霞(1988— ),女,硕士生,主研视频编解码算法;

责任编辑:魏雨博

2013-05-12