光纤通信中8B/10B编码器的设计与实现

秦 蒙,王 辉,秋云海,郭海涛

光纤通信中8B/10B编码器的设计与实现

秦 蒙1,2,王 辉2,秋云海2,郭海涛3

为了满足光纤通信系统中对线路编码的特殊要求,在深入分析现有8B/10B编码原理的基础上,提出了一种新的将同步块分组法与查找表法相结合的8B/10B编码方案。此方案的优势在于能在同一时钟下同步完成3B/4B编码和5B/6B编码,进而通过Disparity和Running Disparity这两个参数来控制编码后的4 bit数据和6 bit数据,使之结合为10 bit并行数据,最后通过串化器转化为高速的串行数据进行输出。整体设计方案用VHDL硬件语言实现了算法的描述,并在QuartusⅡ软件平台上实现了整个编码器的电路综合和波形仿真,结果表明该方案具有占用资源少、编码速度快、实时性好、可靠性高等优点,并且充分满足光纤通信中对高速数据传输的要求。

光纤通信;8B/10B编码器;不均等性;极性偏差

自从1966年高锟首次提出将光纤作为传输介质的概念以来,光纤通信从研究到应用,发展非常迅速,从最初的短波长(0.85 μm)、低速率(34 Mbit/s或 45 Mbit/s)的多模光纤通信系统,到现在的长波长(1.31 μm和1.55 μm)、高速率(2.5 ~10 Gbit/s)的单模光纤通信系统,如今其已发展成为世界上最主要的通信方式之一。同时,随着科学技术的不断提高,高速串行数据传输方式已经成为现代光纤通信系统主要的研究方向之一。为了增加光纤高速网络中信息传输的稳定性和可靠性,现在光纤通信系统中普遍采用8B/10B(8 bit/10 bit)编码机制来完成相关的线路编码[1-2]。

8B/10B编码最初由IBM公司于1983年发明并应用于企业系统连接(Enterprise Systems Connection,ESCON),由 A.X.Widmer和 P.A.Franaszek在 IBM 的刊物《Research and Development》上进行了描述。其基本思想很简单,就是将8 bit的码字经过映射机制转化为10 bit的码字,但是平衡了数据流中“0”和“1”的数量,这就是8B/10B编码的根本目的——直流平衡,因此,其也往往被称为“直流平衡8B/10B编码”[3]。当高速串行数据流中的逻辑“0”或者逻辑“1”的个数有多个位没有产生变化时,信号的转换就会因为电压位阶的关系而造成信号错误,而8B/10B编码的直流平衡特性恰好能克服该问题,这使得该编码方式成为目前许多高速数据传输接口或总线标准常用的编码方式,例如 USB3.0、IEEE 1394b、Serial ATA、PCI Express、InfiniBand、Fiber Channel、Gigabit Etherent等[4-6]。

1 8B/10B编码原理

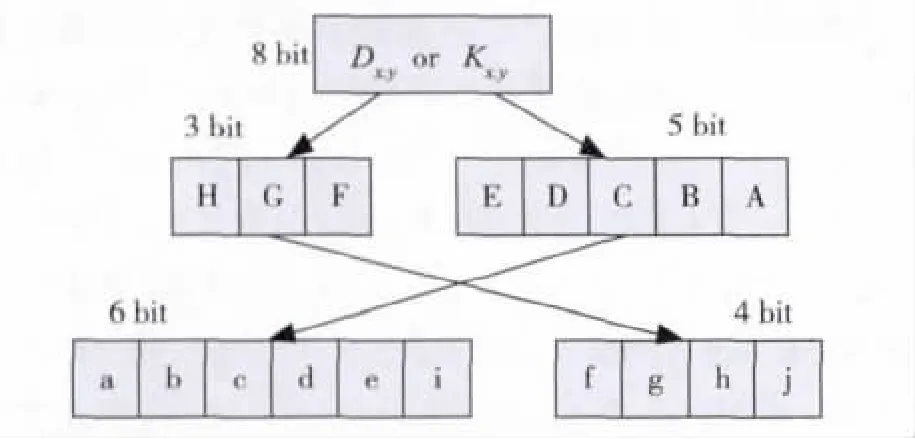

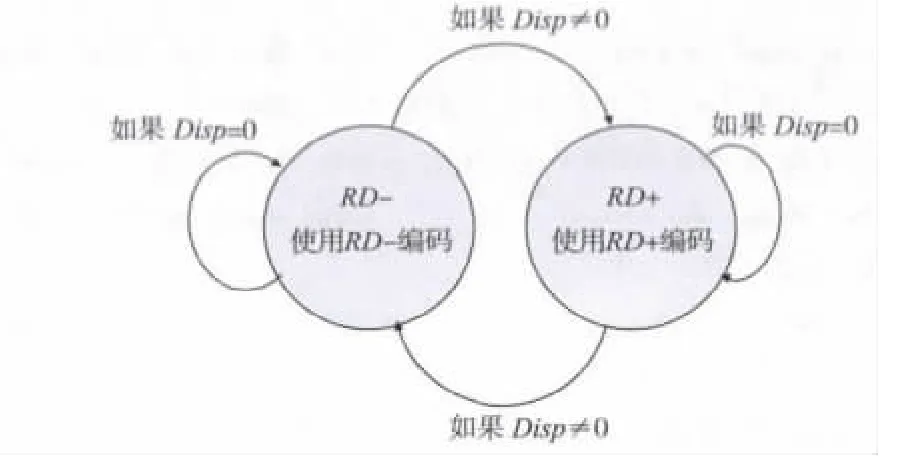

在8B/10B编码机制中,对于输入的任意一组8 bit数据,共有268种可能的有效字符与之对应,其中包括256个普通数据字符和12个特殊字符,分别记为:Dx.y组和Kx.y组(x,y分别为8 bit数据中低5位和高3位所对应的十进制数)。其中,特殊字符Kx.y主要用于建立位同步、链路诊断、标识数据包的开始及结束等。如果假设输入的8 bit连续数据从高位到低位依次为HGFEDCBA,则在编码过程中,其首先被分为3 bit(HGF)和5 bit(EDCBA)两组数据,然后分别经3B/4B编码和5B/6B编码成为4 bit(jhgf)和6 bit(iedcba)码字,并进而组合得到10 bit(abcdeifghj)并行数据,最后经串化器将10 bit并行数据转化为高速串行数据再通过光纤进行传输[7-8]。图1给出了8B/10B 编码器的映射机制[9]。

图1 8B/10B编码器的映射机制

为了保证输出10 bit串行数据流的直流平衡,8B/10B编码机制引入了3个非常重要的参数:游程长度(Run Length,RL)、不均等性(Disparity,Disp)和极性偏差(Running Disparity,RD)。

1)RL是指数据流中连“1”或连“0”的最大位数。在8B/10B编码中,为了满足直流平衡这一特性,要求编码后的10 bit数据流的RL不大于5,也就是说10 bit数据流中的连“1”或连“0”的位数不超过5,即每5个连续的“1”或“0”后必须插入1位“0”或“1”,以此来保证整个链路的直流平衡。

2)Disp是指数据流中“1”和“0”的个数差。在8B/10B编码中,为了尽可能地减小RL的长度,规定编码后10 bit数据中“1”和“0”的位数只可能出现3种情况:4个“1”和6个“0”,5个“1”和5个“0”,6个“1”和4个“0”。显而易见,这3种情况所对应的Disp分别为:-2,0,+2。

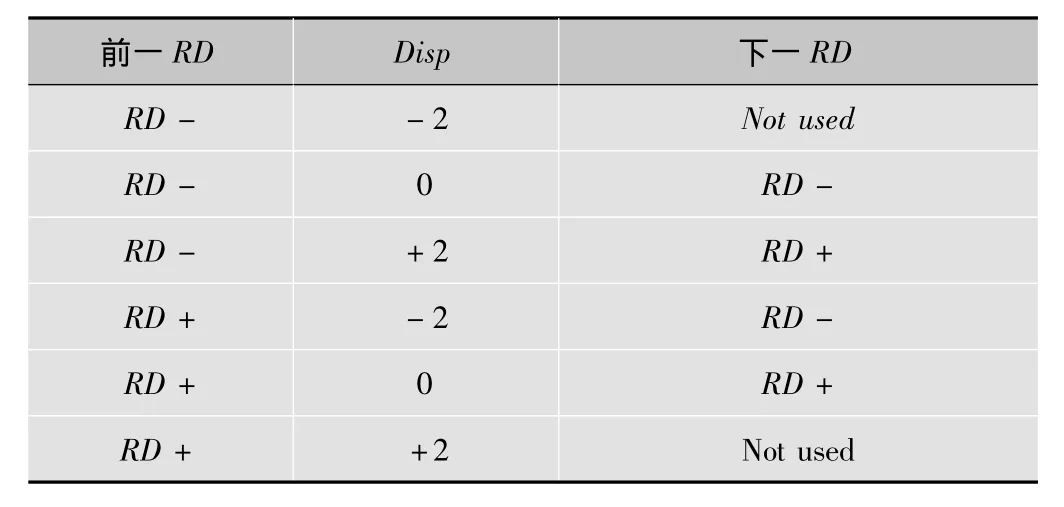

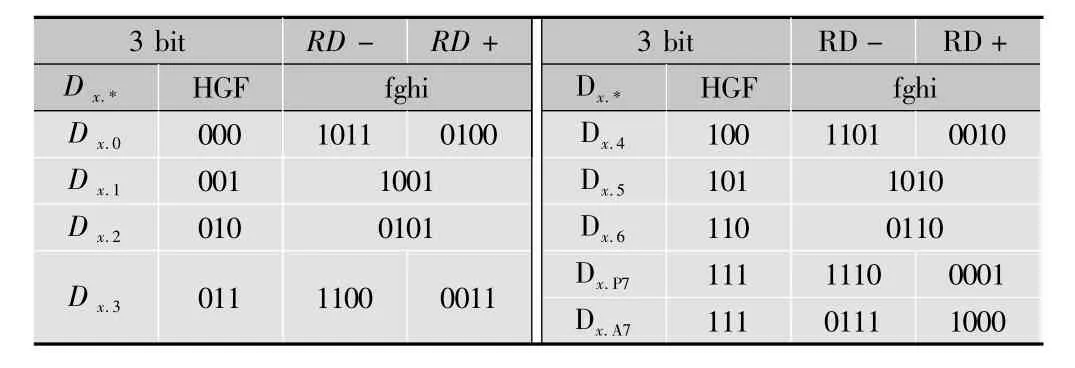

3)相对于上面2个参数,RD的极性转换则显得相对复杂,而这也正是整个8B/10B编码机制中的精髓所在。RD极性转换的目的是控制串行数据流中的直流平衡,其在整个编码方式中起着纽带的作用,将5B/6B编码和3B/4B编码有选择地连接起来。RD只有正负两种状态:RD+和RD-,分别表示数据流中“0”的个数不小于“1”的个数和“1”的个数不小于“0”的个数,在编码的VHDL实现中,RD-和RD+分别用“0”和“1”表示。在系统上电或者复位时,系统会自动给RD赋值为负,即RD的系统默认值为负。确定下一次RD值的规则如下:如果当前编码后的10 bit数据流中“0”与“1”的个数相等(即Disp=0),则次态RD的值保持不变;如果当前编码后的10 bit数据流中“0”与“1”的个数不相等(即Disp≠0),则次态RD的值为当前值的反转。无论是特殊数据字符,还是普通数据字符都符合上述编码规则。表1给出了RD具体转换规则。

表1 极性偏差的转换规则

2 改进8B/10B编码方案

目前8B/10B编码最常用的方法就是查找表法,其又分为直接查表法和块分组法。直接查找表法是最简单最直接的编码方法,如果完全采用直接查找表法,则需要建立一个268个单元的码表用于存放256个普通数据字符和12个特殊字符,每个存储单元有20位,其中10位用于存放RD-所对应的码字,另外10位存放RD+所对应的码字,这种编码方法虽然实现起来方便,但是其在编码过程中占用的资源是非常巨大的,对于普通的CPLD或者FPGA器件来说可能是无法承受的,这在很大程度上限制了该方法的使用。在此基础上,出现了块分组法,首先它将输入的8 bit的数据分为3 bit和5 bit两组,然后分别进行相应的编码,最后再整合形成最终的10 bit码字,此方法在一定程度上简化了码表,节省了芯片资源,但是由于其首先是完成5B/6B编码,然后再按照其输出的RD值进行相应的3B/4B编码,这样就使得两种编码不能同步完成,而且3B/4B编码要比5B/6B编码最少要滞后一个时钟周期的时间,实时性差[9-10]。另一种方法则是采用逻辑电路直接实现,但是这种方法的难点在于电路的逻辑关系复杂,同时由于延时、竞争和冒险现象的存在,会使最终输出的数据出现严重的抖动,限制芯片的最高工作速度[11-12]。因此寻找一种高效的8B/10B 的编码方法,是现在高速串行数据传输中亟待解决的问题。

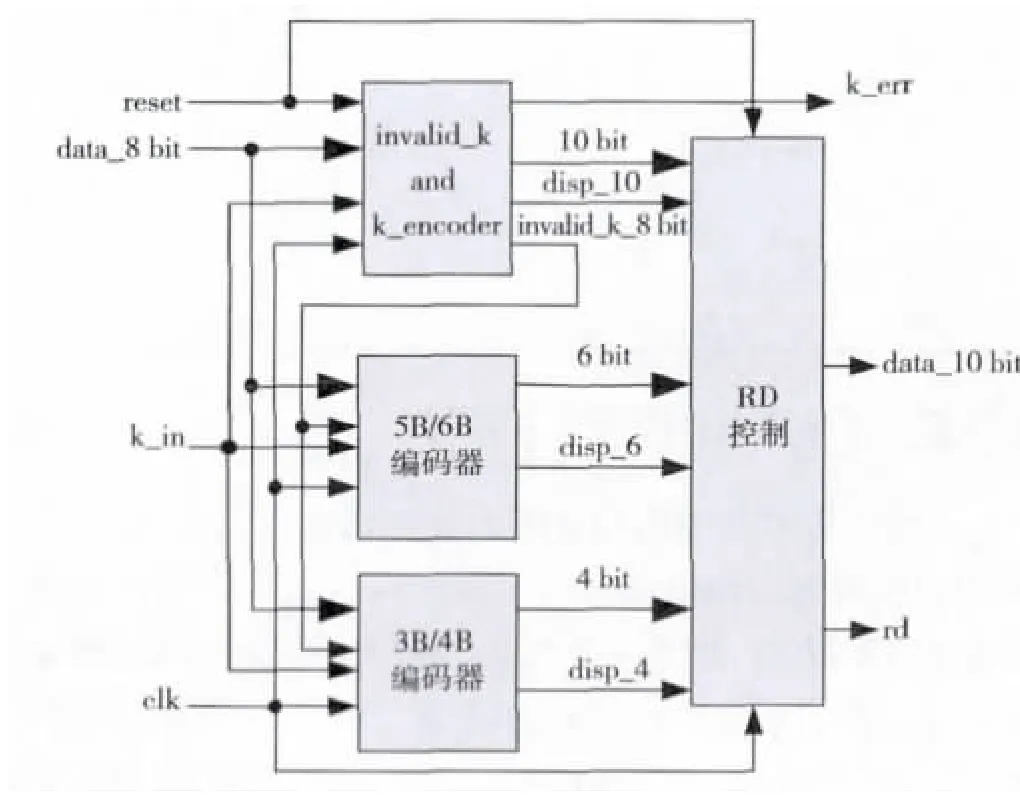

鉴于此,本文采用了一种新的编码方法,即:直接查找表法与同步块分组法相结合的方法。其基本思路为:首先判断输入的8 bit数据是否为特殊字符Kx.y,如果是Kx.y,则用直接查找表法直接输出对应的10 bit码字;如果输入的8 bit数据是普通的数据字符Dx.y,则首先按照块分组的思想将8 bit的Dx.y拆分为3 bit和5 bit两组,然后在RD的控制下以同步并行的方式完成相应的3B/4B编码和5B/6B编码,最后再通过整合输出相应的10 bit码字。这种方法不仅可以简化码表,降低功耗,而且相对于传统的块分组的方法,增强了编码的实时性,提高了编码的工作效率。如图2所示,8B/10B编码器总共可以细分为 4 个模块:invalid_k and k_encoder,5B/6B encoder,3B/4B encoder,RD control。

图2 8B/10B编码器框图

2.1 invalid_k and k_encoder模块

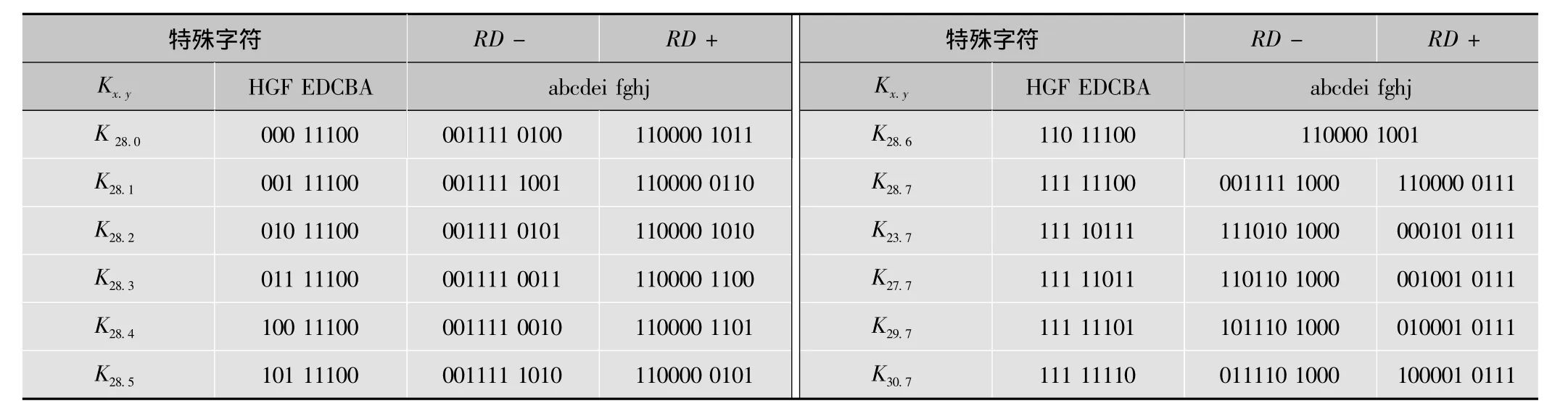

该模块主要用来完成特殊字符Kx.y的检错和编码工作。由表2可知[3],8B/10B编码机制中只有12组特殊字符,所以可以通过直接查找表法直接完成相应的编码。同时,也正是由于只有这12组码字是有效的,其他码组均为无效码组,因此为了降低误码率(Bit Error Ratio,BER),需要添加一个错误检测环节以验证特殊字符的有效性。整个模块的具体运作步骤如下:当输入的是特殊字符时(k_in为1),首先要判断其是否是有效字符,即判断其是否包含在这12种码字中,如果包含在其中,则通过直接查找表法输出对应的10 bit码字;如果没有包含在其中,则将检错信号k_err置高,同时将无效特殊字符invalid_k_8 bit按照普通数据字符Dx.y的编码规则对其进行编码,这样就可以继续保持整个数据流中的直流平衡。

2.2 5B/6B encoder和3B/4B encoder模块

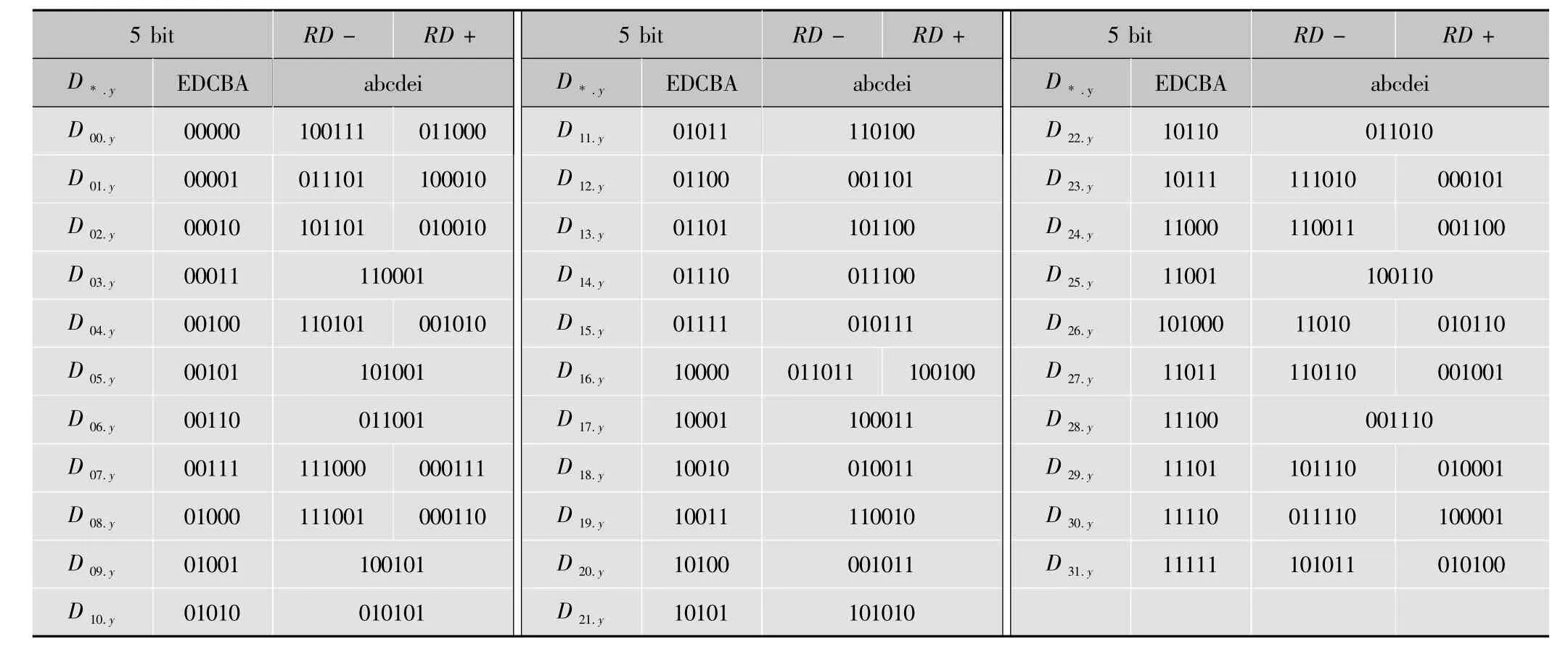

该模块主要来完成普通数据字符和无效特殊字数的相关编码。相对于传统的按顺序进行的块分组编码方式,本文提出了一种新的并行的同步块分组编码方式,具体步骤如下:系统上电后会自动初始RD值为RD-(RD=0)。首先,在时钟上升沿时按RD-完成首个8 bit数据低5位的5B/6B编码,同时在同一时钟上升沿处按照RD-完成高3 bit的3B/4B编码。其次,通过奇偶校验的方法计算出6 bit数据的disp_6值,然后再根据disp_6的值确定当前RD值是否需要改变(若disp_6=0,则RD值不变;若disp_6≠0,则RD值取反)。随后,根据6 bit数据确定的RD来决定3B/4B编码的输出:若RD为RD-,则直接输出4 bit数据;若RD为RD+,则还需判断3 bit数据是否包含在001,010,101,110中,若在其中,则仍直接输出4 bit数据,否则将编码后的4 bit数据按位取反后输出。最后,根据最终输出的4 bit值,用同样的方法计算出该4 bit数据RD值,此时的RD值即为本组10 bit编码结果的极性,并以此为依据指导下一组8 bit数据的编码工作。表3为5B/6B 编码表[3],表4 为3B/4B 编码表[3]。

表2 特殊字符编码

2.3 RD control模块

该模块除了在时钟clk的上升沿将编码后的10 bit数据进行选择输出外,还要根据前3个模块输送来的disp_6、disp_4及disp_10来更新当前的RD值,并反馈到下一轮的RD输入,并通过不同的RD来选择相应的编码,避免串行数据流中的RL超过5,以此保证整个链路上的直流平衡。该模块用VHDL语言中最常见的状态机实现,具体转换规则如图3所示。

表3 5B/6B编码

表4 3B/4B编码

图3 RD的状态转换图

3 仿真结果与分析

根据本文提出的这种新的8B/10B编码方式,在Altera公司的QuartusⅡ软件平台上用VHDL语言进行了相关程序代码编写,并选用其MAXⅡ系列的CPLD器件EPM570T100C5N实现了编码器的功能验证、电路综合和波形仿真[13-14]。

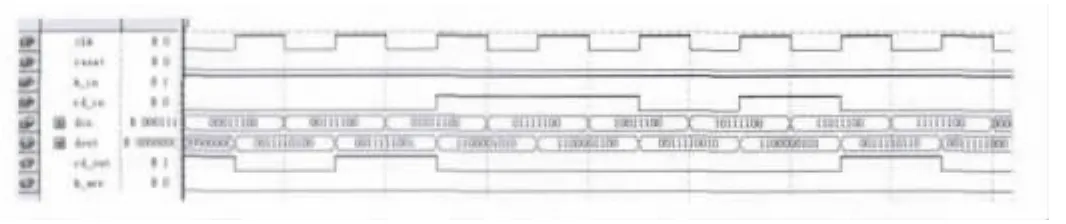

图4为特殊字符的波形仿真图。其中rd_in为当前编码的RD值,din为输入的8 bit特殊字符,dout为编码后的10 bit数据,rd_out为下次编码的RD参考值。由仿真图可以看出,在不同rd_in值的控制下,系统会自动选择对应的输出,并会通过rd_out更新当前的RD值,进而指导下次编码,这与表2特殊字符编码表完全对应,验证了整个编码模块的功能的正确性。

图4 特殊字符仿真图(截图)

图5为普通字符的波形仿真图。其中rd_in为当前RD值,din为输入的8 bit普通数据字符,dout为对应输出的10 bit编码数据,rd_out为下次编码的RD参考值。由仿真图可以看出,在不同的rd_in值的控制下,系统会自动根据表3和表4完成相应的编码,并会通过rd_out的值来更新RD,进而指导下次编码。整个编码模块结构简单,功能正确,逻辑清晰直观,且延时小,体现出了该编码方案的优越性。

图5 普通字符仿真图(截图)

4 小结

随着世界科技的不断发展,各种总线传输方式和总线标准的传输速率都在不断的提高。在光纤通信系统中,高速率的传输方式正在指引着整个行业的发展方向,而信道编码作为影响其传输速率的主要原因之一,开始显得格外重要。本文提出的这种将同步块分组法与查找表法相结合的8B/10B编码方法,结构简单,使用较少的逻辑单元(42/570)便能完成8B/10B编码器的设计。同时,整个编码器的最大时钟能达到250 MHz以上,且能保证整个链路的直流平衡,能很好地满足光纤通信系统对高速数据的传输要求。此外,该方法具有很好的可移植性,可以作为IP核植入到需要8B/10B编码的光纤电路设计中,特别适合FPGA/CPLD的设计,具有广泛的应用前景。

:

[1]HAN S,LEE M S.Burst-mode penalty of AC -coupled optical receivers optimized for 8B/10B line code[J].IEEE Photonics Technology Letters,2004,16(7):1724-1726.

[2]唐兴,唐宁.光纤通道8B/10B编码的ASIC研究与设计[J].电子器件,2011,34(2):210-214.

[3]WIDMER A X ,FRANASZEK P A.A DC-balanced,partitioned-block,8B/10B transmission code[J].IBM Journal of Research and Development,1983,27(5):440-451.

[4]SHAGHAYEGH A,SARA S.A method for implementation of the DC-balanced 8B/10B coding used in superspeed USB[C]//Proc.2010 First International Conference on Integrated Intelligent Computing.Bangalore:IEEE Computer Society,2010:68-72.

[5]林锦棠.8B10B编解码器在PCI Express总线中的实现[J].微计算机信息,2008,24(11):140-142.

[6]WANG Qi,HUA Siliang,WANG Donghui.A 1.1 GHz 8B/10B encoder and decoder design[C]//Proc.2010 Asia Pacific Conference on Postgraduate Research in Microelectronics and Electronics.Shanghai:[s.n.],2010:138-141.

[7]AREF A ,AHMED N A,SALAZAR F R,et al.RTL-level modeling of an 8B/10B encoder-decoder using system[C]//Proc.5 th IFIP International Conference on Wireless and Optical Communication.Surabaya:IEEE Computer Society,2008:1-4.

[8]KIM YW,KANG J K.An 8B/10B encoder with a modified coding table[C]//Proc.IEEE Asia Pacific Conference on Circuits and Systems.Macao:[s.n.],2008:1522-1525.

[9]李宥谋.8B/10B编码器的设计与实现[J].电视技术,2005,29(6):26-32.

[10]孙科达,石旭刚,史故臣.一种新的8B/10B编解码方案设计与实现[J].光通信技术,2009(7):27-30.

[11]赵文虎,王志功,费瑞霞,等.基于逻辑设计的光纤通信8B/10B编解码方法研究[J].电路与系统学报,2003,8(2):48-53.

[12]刘智,宁红英,王普昌.一种新的8B/10B编码电路设计[J].通信技术,2009,42(7):60-84.

[13]Altera Corporation.MAXⅡDevice Handbook[EB/OL].[2013-04-16].http://www.altera.com.cn/literature/hb/max2_mii 5v1.pdf.

[14]雷伏容.VHDL电路设计[M].北京:清华大学出版社,2006.

(1.东北电力大学信息工程学院,吉林吉林 132012;2.中国科学院深圳先进技术研究院神经工程研究中心,广东深圳 518055;3.东北电力大学电气工程学院,吉林吉林132012)

Implementation and Design of 8B/10B Encoder for Fiber Communication

QIN Meng1,2,WANG Hui2,QIU Yunhai2,GUO Haitao3

(1.College of Information Engineering,Northeast Dianli University,Jilin Jilin 132012,China;2.Research Center for Neural Engineering,Shenzhen Institutes of Advanced Technology ,Chinese Academy of Sciences,Guangdong Shenzhen 518055,China;3.Electrical Engineering College,Northeast Dianli University,Jilin Jilin 132012,China)

In order to meet the special requirements of line encoding in optical fiber communication system,a new 8B/10B encoding scheme,based on the existing 8B/10B coding principle,combining synchronization block grouping method with look-up table method is proposed.This encoding scheme has the advantage of completing 3B/4B encoding and 5B/6B encoding synchronously under the same clock,and then controls the encoded 4 bit and 6 bit data united as 10 bit parallel data through the two parameters Disparity and Running Disparity,finally changes the 10 bit parallel data into a high-speed serial data via the serializer.The algorithm of overall design is described with VHDL,and the circuit integrated and waveform simulation of the entire encoder are realized on the QuartusⅡsoftware platform.The results show that this encoding scheme has the advantages of requiring fewer chip resources,high coding speed,excellent real-time ability,and high reliability.It totally meets the requirements of high-speed data transmission in optical fiber communication.

fiber communication;8B/10B encoder;disparity;running disparity

TN929.1

A

【本文献信息】秦蒙,王辉,秋云海,等.光纤通信中8B/10B编码器的设计与实现[J].电视技术,2014,38(1).

深圳市杰出青年资助项目(JC201005270293A)

秦 蒙(1986— ),硕士生,研究方向为光纤通信;

王 辉(1984— ),硕士,工程师,研究方向为生物医学信号处理;

秋云海(1974— ),博士,研究员,研究方向为神经影像学;

郭海涛(1965— ),博士,教授,研究方向为图像处理、信号处理、模式识别等。

责任编辑:魏雨博

2013-05-21