软件无线电实现调制解调器的设计

牛耀利 张太福

(中国人民武装警察部队新疆总队乌鲁木齐市支队,新疆 乌鲁木齐830003)

0 引言

软件无线电是模块化、标准化的硬件单元,以总线方式连接构成基本平台,并通过软件加载实现各种无线通信功能的一种开放式体系结构。其中心思想是构造一个具有开放性、标准化、模块化的通用硬件平台,将各种功能,如工作频段、调制解调类型、数据格式、加密模式、通信协议等,用可升级、可重新配置的软件来完成,并使宽带A/D和D/A转换器尽可能的靠近天线,以研制出具有高度灵活性、开放性的新一代无线通信系统[1]。

1 软件无线电的基本结构

软件无线电强调体系结构的开放性和全面可编程性,通过软件的更新改变硬件的配置结构,实现新的功能。

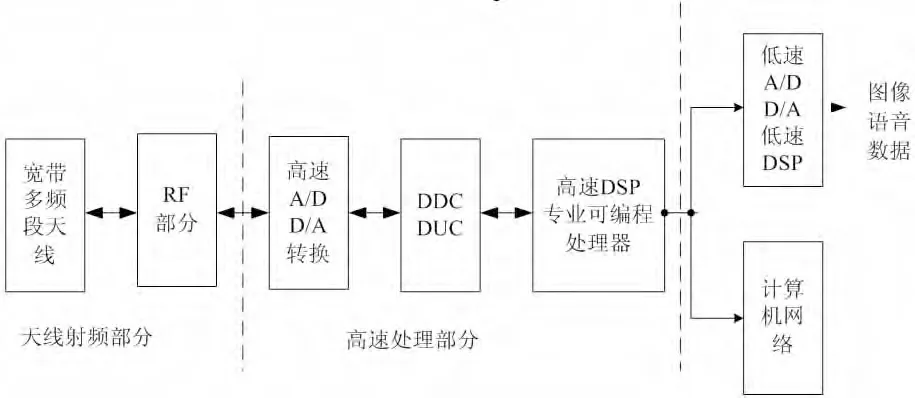

图1 理想的软件无线电系统结构

理想的软件无线电结构如图1所示。软件无线电主要由天线、射频前端、高速A/D/A转换器、通用和专用数字信号处理器、低速A/D/A转换器以及各种接口和软件所组成。在发射时RF部分主要完成滤波、功率放大等任务,接收时实现滤波、放大等功能。理想的软件无线电因实现射频直接带通采样,要求A/D转换器有足够的工作带宽,较高的采样速率,而且要有较高的A/D转换位数,以提高动态范围。模拟信号进行数字化后的处理任务全由DSP和专用的可编程处理器的软件来承担。为了减轻通用DSP的处理压力,通常把A/D转换器传来的数字信号,经过专用数字信号处理器件 (如数字下变频器DDC)处理,降低数据流速率,并把信号变至基带后,再把数据送给通用DSP进行处理。通用DSP主要完成各种数据率相对较低的基带信号的处理,比如信号的调制解调,各种抗干扰、抗衰落、自适应均衡算法的实现等。还要完成经信源编码后的前向纠错(FEC),帧调整、比特填充和链路加密等算法。也有采用多DSP芯片并行处理的方法,以提高其处理的能力。

2 调制解调系统关键模块的FPGA的实现

QPSK调制及解调部分由几个关键模块组成,其中包括,加法器、乘法器、载波发生器、FIR滤波器、PN序列模块和通信中载波同步、位同步、帧同步等部分,下面就其重点部分的具体实现方法做以阐述。

2.1 加法器模块

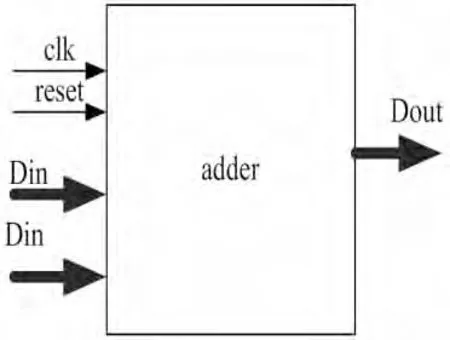

加法模块是QPSK系统中比较重要的组成部分,目前有很多种加法器的设计。图2所示的加法器为本系统所采用的方法,模块和端口定义如下:

Clk——输入信号,工作时钟;

Rest——输入信号,系统复位;

Din1——输入信号,被加数输入;

Din2——输入信号,加数输入;

Dout——输出信号,相加结果输出。

图2 加法器模块

这里采用的加法器属于同步加法器,有时钟的上升沿来临时接数据对其做相加处理。加法器模块的两个输入分别是同相支路和正交支路中信号与载波相乘后的结果,因而是有符号数,采用补码表示。在定点运算中,补码的最高位为符号,正数为0,负数为1,而其它的为它绝对值。这样,正数的补码和它的源码相同,负数的补码为将它的源码逐位求反,然后在最低位上加1。这样,计算两数相减(即一个正数加一个负数)的运算可以通过用它们的补码相加来完成,简化了运算电路[2]。

2.2 乘法器的实现

在软件无线收发信机中,乘法器的作用主要是用于混频,在发信机中,离散的基带I,Q采样值与NCO输出的离散正交载波相乘,完成上变频过程,在收信机中,经过带通采样的离散接收信号与NCO输出的离散正交载波相乘,经过低通滤,得到离散的数字I,Q信号,完成下变频过程。乘法器起到两个信号相乘的作用。

乘法器一般采用并行工作方式,本设计中发信机的离散基带I,Q采样值为8比特有符号数,NCO数字本振的输出也为8比特有符号数,所设计的乘法器的两个输入应该为8比特有符号数,乘积为16比特。所以采用一种由8位加法器构成的以时序逻辑方式设计的8位乘法器。其乘法原理是:乘法通过逐项移位相加原理来实现。从被乘数的最低位开始,若为1,则乘数左移后与上一次的和相加;若为0,左移后以全0相加,直至被乘数的最高位。

2.3 NCO的FPGA实现

载波发生器基于数控振荡器(NCO)产生,数控振荡器结构如图3所示。主要由相位累大器和SIN/COS表构成。相位累加产生的相位作为地址去查找ROM表,查到的SIN/COS值即本地载波的数字频率送至乘法器,完成混频。

图3 数控振荡器结构图

实际的NCO由样位累加器、波形ROM查找表组成,这样的结构很容易用FPGA实现,两个正弦波产生查找表,用Xilinx提供的IP核。本设计中采用了30位的相位累加器,进行相位截断后,用相位累加大路的高10位寻址波形ROM,需要注意的是为了使设计的NCO能用于上变频和下变频操作,波形ROM中所存的内容必须同时提供两路完全正交的正弦波和余弦波。由于是10位寻址ROM,并且指定ROM的字长为8比特有符号数,所以每一块的ROM容量应为210=1K*8,故总共需2K*8的存储量,这在FPGA实现时将耗费大量的内部CLB资源,所以应该重新考虑ROM查找表的设计,尽可能节省存储器资源。对于正弦波和余弦波来说可以得用对称性只存储二分之一周期,甚至四分之一周期,对于前者需要附加一个符号求补器,后者则另需一个相位求补器和符号求补器[4]。

2.4 滤波器的实现

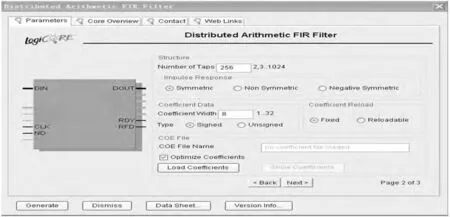

本设计中滤波器为低通滤波器,截止频率是该通道的码元速率,即2.5kHz。滤波器的采样时钟用此时的系统时钟频率(160kHz)。Xilinx的综合软件Core Generation给出了这种滤波器的实现。如图四所示:

图4 FIR模块图

模块端口定义如下:

CLK——输入信号,滤波器工作时钟160kHz;

DIN[N-1.0]——输入信号,滤波器的数据输入,N为位宽,即接收机中乘法器的输出位宽为N=24;

ND——输入信号,高有效,为高时表示一个新的数据输入;

RDY——输出信号,高有效,为高时表示滤波器己处理完当前数据,可以接收新的数据输入;

RFD——输出信号,高有效,为高时表示滤波器输出端口上有一个新的结果数据输出;

DOUT——[M-1,0]-输出信号,滤波器的数据输出,M为输出位宽,与发射机的基带码流相对应,这里取M=8。

3 小结

数字调制解调在FPGA中的实现证明了用FPGA作为软件无线电数字信号处理器件的可行性。使用FPGA的可重构性,可以在系统中实现各种通信模式的算法,充分体现了软件无线电的灵活性。同时,实现了嵌入FPGA的CPU核对芯片的信号处理功能控制。通过嵌入式CPU,可心用软控制芯片的信号处理过程,为以后实现控制信号处理及系统的在线重构打下了基础。

[1]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2]A.Dempster,M.Macleod.Use of Minimum-Adder Multipler Blocks in FIR Digital Filters[J].IEEE Transactions on Circuits and SystemsⅡ,1995.

[3]Xilinx.The Role of Distributed Ariehmetic in FPGA-based Signal Processining[Z]//The programmable Logic Data Book,2000.

[4]董金明,FPGA在软件无线电技术实现中的应用[D].北京:北京航空航天大学,2001:47-48.