摩尔定律的过去、现在和未来

戴锦文,缪小勇(南通富士通微电子股份有限公司,江苏 南通 226006)

摩尔定律的过去、现在和未来

戴锦文,缪小勇

(南通富士通微电子股份有限公司,江苏 南通 226006)

摘 要:分析研究了半导体技术摩尔定律的过去、现在和未来,重点分析了摩尔定律的产生、发展以及在基础物理、光刻、制造成本及功耗等方面的困难和挑战。同时讨论了“超越摩尔定律”的发展方向、适应领域范围,以及摩尔定律在未来的可能实现方式。

关键词:摩尔定律;芯片尺寸极限;超越摩尔定律;beyond CMOS

1 引言

摩尔定律是由英特尔(Intel)创始人之一戈登•摩尔(Gordon Moore)在搜集1959年至1965年集成电路上晶体管数量的数据基础上,于1965年4月提出的[1]。其内容为:当价格不变时,集成电路上可容纳的元器件数目,约每隔18~24个月便会增加一倍,性能也将提升一倍。

最新的研究表明,“摩尔定律”的时代将会退出,因为研究和实验室的成本十分高昂,而有财力投资在创建和维护芯片工厂的企业很少。芯片制程也越来越接近半导体的物理极限,将难以再缩小下去。预计定律将持续到2017—2020年。

本文对摩尔定律的过去、现在进行了阐述,并进一步预测和分析了摩尔定律在未来可能发生的变化。

2 摩尔定律的过去

2.1摩尔定律的产生

1959年,美国著名半导体厂商仙童公司首先推出了平面型晶体管,紧接着于1961年又推出了平面型集成电路。这种平面型制造工艺是在研磨光滑平整的硅片上,采用一种所谓“光刻”的技术来形成半导体电路的元器件,如二极管、三极管、电阻和电容等。

“光刻”的精度不断提高,元器件的密度也会相应提高,因而具有极大的发展潜力。因此平面工艺被认为是“整个半导体的工业键”,也是摩尔定律问世的技术基础。

1961年4月25日,第一个集成电路专利被授予罗伯特•诺伊斯。最初的晶体管对收音机和电话而言已经足够,但是新的电子设备要求规格更小的晶体管,即集成电路。

1965年摩尔定律诞生。当时,戈登•摩尔在《电子杂志》特刊中预测:每个新芯片大体上包含其前任两倍的容量,每个芯片的产生都是在前一个芯片产生后的18~24个月内。

2.2摩尔定律的验证

1975年,在一种新出现的电荷前荷器件存储器芯片中,的确含有将近65000个元件,与1965年摩尔的预言一致。另据Intel公司公布的统计结果,单个芯片上的晶体管数目,从1971年4004处理器上的2300个,增长到1997年Pentium II处理器上的7.5百万个,26年内增加了3200倍。如果按“每两年翻一番”的预测,26年中应包括13个翻番周期,每经过一个周期,芯片上集成的元件数应提高2n倍(0≤n≤12),因此到第13个周期即26年后元件数与实际的增长倍数3200倍可以算是相当接近了。

1994年初,美国LSI公司研制成功集成度达900万个晶体管的逻辑芯片;1997年,Intel推出了包含750万个晶体管的奔腾处理器,这款新产品集成了Intel MMX媒体增强技术,专门为高效处理视频、音频和图形数据而设计。1998年3月,英特尔公司制成包含702亿个晶体管的集成电路芯片,这表明集成度这一微电子技术的重要指标在不到40年内便提高了7000万倍;2003年单位芯片的晶体管数目与1963年相比增加了10亿倍;2004年,Intel推出在新的直径为300 mm的晶圆片(晶圆片尺寸一般十年翻一番)上能够刻出容纳5亿个晶体管的芯片;2005年,芯片所含晶体管数高达几十亿只,频率也高达几千兆;2007 年11月,英特尔共发布了16款Penryn处理器,主要面向服务器和高端PC。这些产品采用了更先进的45 nm生产工艺,其中最复杂的一款拥有8.2亿个晶体管。英特尔上一代产品主要采用65 nm生产工艺,最复杂的一款处理器拥有5.82亿个晶体管; 2010年,三星公司实现了30 nm制程内存芯片量产;Intel于2011年推出了含有10亿个晶体管、每秒可执行1千亿条指令的芯片;2015年,三星公司为苹果公司大规模量产14 nm的A9移动处理器。2015年7月,IBM做出了7 nm芯片,利用的材料是硅锗而不是硅。该项突破性成果,具备了在指甲盖大小的芯片上放置200亿只晶体管的能力。而芯片能够为各种智能设备提供计算能力,小到智能手机,大到宇宙飞船。

2.3摩尔定律的意义

“摩尔定律”归纳了信息技术进步的速度,对集成电路发展趋势的分析预测是准确而难能可贵的。

“摩尔定律”对整个世界意义深远。在回顾四十多年来半导体芯片业的进展并展望其未来时,信息技术专家们认为,在以后一段时间,“摩尔定律”可能还会适用。但随着晶体管电路逐渐接近性能极限,这一定律终将走向极限。四十多年中,半导体芯片的集成化趋势一如摩尔的预测,推动了整个信息技术产业的发展,进而给千家万户的生活带来变化。

3 摩尔定律的现在

3.1摩尔定律面临的挑战

在摩尔的眼里,摩尔定律所揭示的速度是不可能永远持续下去的[2]。一些文章认为摩尔定律将会因为漏电流和高温被终结[3]。

3.1.1 芯片尺寸极限

现有的硅芯片在未来5年内将可能达到物理极限,其单个晶体管的大小将达原子级,这将是一个真正的物理极限。目前,大规模芯片生产已普遍达到40 nm工艺,28 nm工艺规模也逐渐在扩大,三星和英特尔14 nm工艺也已经研发出来,并已成功用于苹果的移动处理器。微电子工业发展每下一步的线宽大约是前一步的0.7倍,因而14 nm的下一步是9.8 nm,我们已经逐步逼近原子极限。如果芯片生产仍然能以3年翻一番的速度发展,那么在几年之后,就必然会面临硅芯片技术的物理极限。

3.1.2 漏电流

当“栅极”的长度小于5 nm 时,将会产生隧道效应,即由于源极和栅极很近,电子会自行穿越通道,从而造成“0”、“1”逻辑错误。Intel的研究结果证明,隧道效应不管晶体管材质的化学特性怎样都会发生,当缩小晶体管尺寸到了一定程度时,必会产生隧道效应。

3.1.3 功耗和散热

毫无疑问,处理器的功耗密度不可能无限地提高。尽管可能通过诸多方式来降低功耗,但都不可能从根本上解决这一问题。

3.1.4 成本

芯片制造设备成本的上升也给摩尔定律的延续带来了压力。IBM研究人员Carl Anderson提出“摩尔定律即将没电”的观点,认为IT行业的指数增长现象都已经走到了尽头。因为越来越多的设计人员发现,日常应用并不需要时下最新的架构设计以及最高端的芯片,而高额的研发费用以及生产线的更新也仅有少数公司可以承受。

3.2超越摩尔定律

基于摩尔定律面临的困境与挑战,业界提出了“More-Than-Moore”(简称MTM,即“超越摩尔定律”),试图通过更多的途径来维护摩尔定律的发展趋势,并且从摩尔定律的“更多更快”,发展到MTM的“更好更全面”。

“超越摩尔定律”可以分为晶圆制造集成(例如SoC、芯片/晶圆堆叠等前、中端工艺)和封装(例如SiP、混合组装等后端工艺)两个分领域。用户定制、多品种、小批量是“超越摩尔定律”面临的主要问题[4]。

摩尔定律在Logic类和Memory类集成电路的发展中提出并得到验证,而MTM则适用于更多类型的集成电路,如Analog、RF、Image Sensor、Embedded DRAM、Embedded FLASH、MEMS、High Voltage等,通过改变基础的晶体管结构(SOI、FIN-FET)、各类型电路兼容工艺、先进封装(晶圆级封装、SiP、3D多芯片封装)等技术,使一个系统级芯片能支持越来越多的功能,同样可以降低芯片的成本、提高电路的等效集成度。2014年,通富微电公司率先在国内实施了305 mm、28 nm先进封装量产全制程,大幅降低芯片封装的成本。

“More-Than-Moore”延续 CMOS的整体思路,在器件结构、沟道材料、连接导线、高介质金属栅、架构系统、制造工艺等方面进行创新研发,沿着摩尔定律一路 scaling(每两年左右晶体管的数目翻倍)。

估算公式为:L=S • L,P=S2• P,г=S • г,where S=0.7 per3/2 years L是特征尺寸(就是 22 nm、14 nm、10 nm 等等),P 是相应的能耗,г是传播延时。

同样,“More-Than-Moore”存在的挑战仍在于无法承受的能耗密度、原子尺度的物理限制、制程、器件的不稳定性和偏差、比例缩小并没有带来实质的性能提升(每次乘 0.7 或0.72,后面得到的值之间的差越来越小)以及高昂的研发和制造成本。

3.3近期取得的突破性研究成果

2012年10月28日,美国IBM研究所科学家宣称,最新研制的碳纳米管[5]芯片符合了“摩尔定律”周期,依据摩尔定律,计算机芯片每18个月集成度翻番,价格减半。传统的晶体管是由硅制成,然而2011年来硅晶体管已接近了原子等级,达到了物理极限,由于这种物质的自然属性,硅晶体管的运行速度和性能难有突破性发展。

IBM公司的研究人员在一个硅芯片上放置了1万多个碳纳米晶体管,碳纳米晶体管的电子比硅质设备运行得更快。它们也是晶体管最理想的结构形式。这些优异的性能将成为替代硅晶体管的原因,同时结合新芯片设计架构,未来将使微型等级芯片实现计算机创新。

4 摩尔定律的未来

现在集成电路正在逐渐逼近尺寸和计算能力的极限,这可能意味着严格定义上的摩尔定律的结束。但是我们还有大量新技术在等待时机接替上来,就像集成电路对分立晶体管、晶体管对真空管做的那样。其中最可能的大概就是以今天的GPU为代表的并行计算了。并行计算不仅能在图形处理上给计算性能带来显著的提升,而且也能为针对多处理器内核的应用程序提供强有力的性能支持。还有就是量子计算,但目前还没有一台有实用价值的机器出现。当然,还有那些各种各样的新物理计算机架构,从光计算到石墨烯等。目前正在研究超越CMOS的新型器件,包括很多可以实现非硅内存器件和逻辑开关的技术,比如自旋电子器件(Spintronic Storage)、纳米管(Carbon Nanotubes)、纳米线(Nanowires)和分子电子器件(Molecular Electronics)等[6]。

4.1隧道场效应晶体管 (TFET)

TFET主要应用量子力学的隧穿原理,直接穿越source和drain间的屏障而不是扩散过去。

优势在于实现低电源电压、低功耗以及更好的次临界摆幅与 CMOS 工艺兼容。挑战在于低饱和电流对提高内部电场的栅极电压控制度有难度以及界面态的问题(在传送和接收端都需要足够高的界面密度来为载子提供能量充足的位置)。

4.2纳米机电开关 (NEMS)

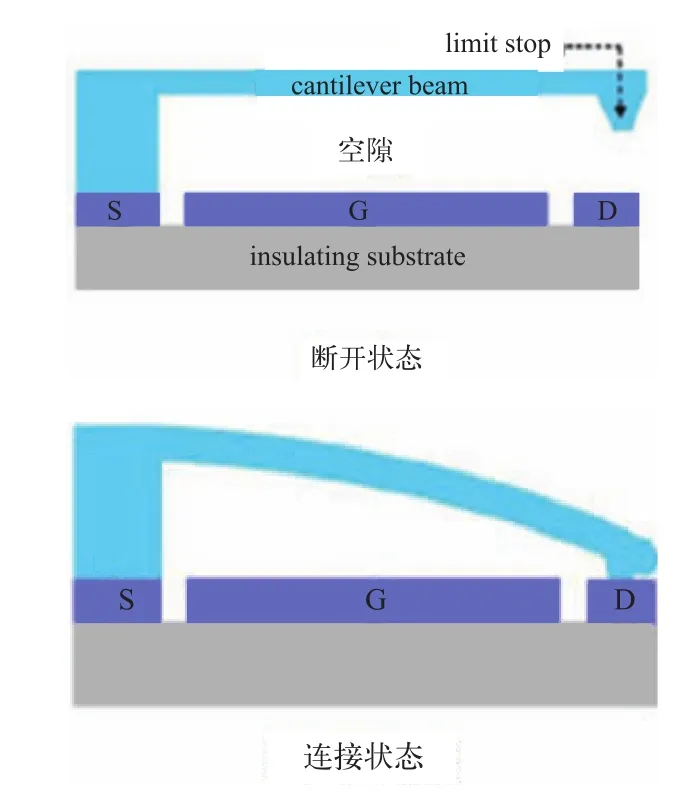

图1 纳米机电开关模型

NEMS是MEMS 的进阶版,用图1所示的悬梁臂作为机械开关。

优势在于理论上可以做到零泄漏电流和亚阈值摆幅,对温度的敏感度低,对电磁冲击免疫,与CMOS工艺兼容;挑战在于由于悬梁臂的机械动作带来较低的开启关闭速度,纳米级接触的可靠性,表面力产生的突刺,受到隧穿效应限制的比例缩放,高吸和电压。

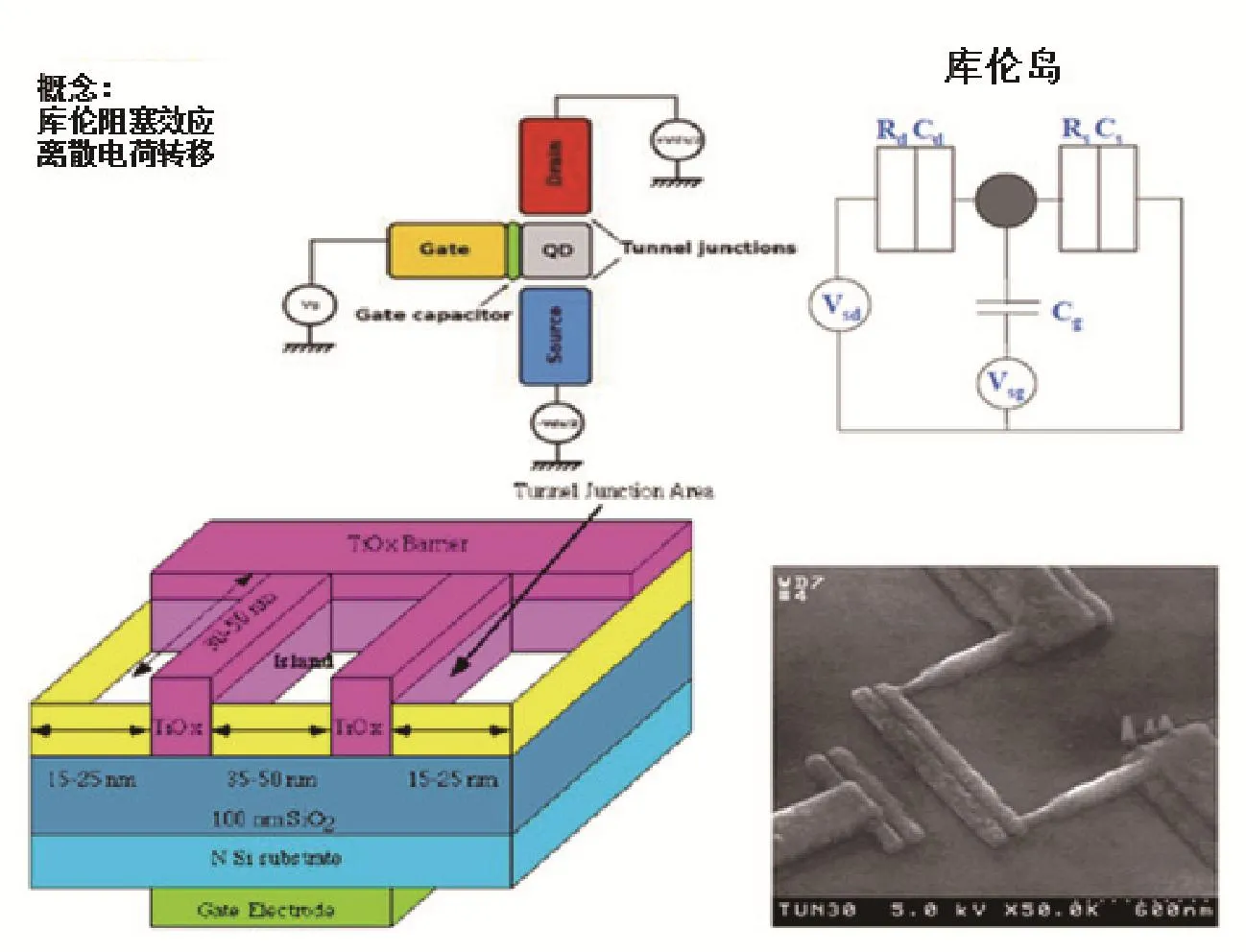

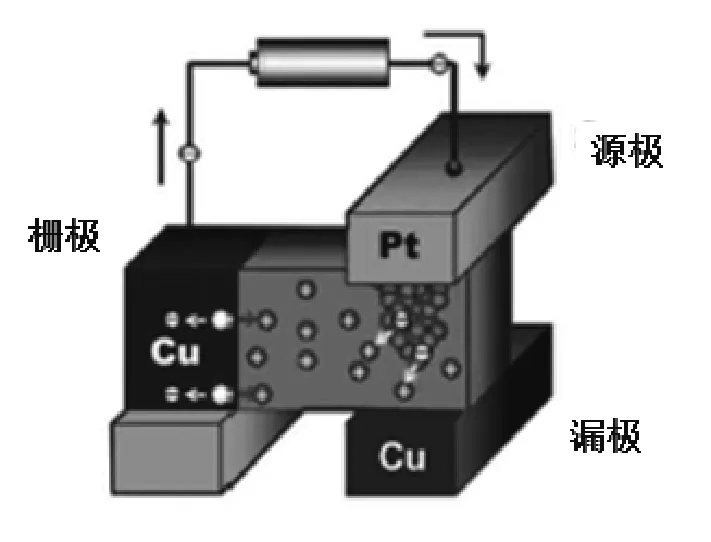

4.3单电子晶体管 (SET)

栅端电压控制稳定状态间的调谐,实现“岛”上单一电子的增或减。

优势有高速、高器件密度、高能效、可能带来新奇的功能和应用以及与 CMOS 工艺兼容;挑战有尺寸

图2 单电子晶体管工作原理

与温度的权衡、低增益、较大的阈值电压变化、寄生电容、低输出电流、高输出阻抗、有限的扇出数、较低的抗噪声能力以及尚未完全成熟的制造工艺。

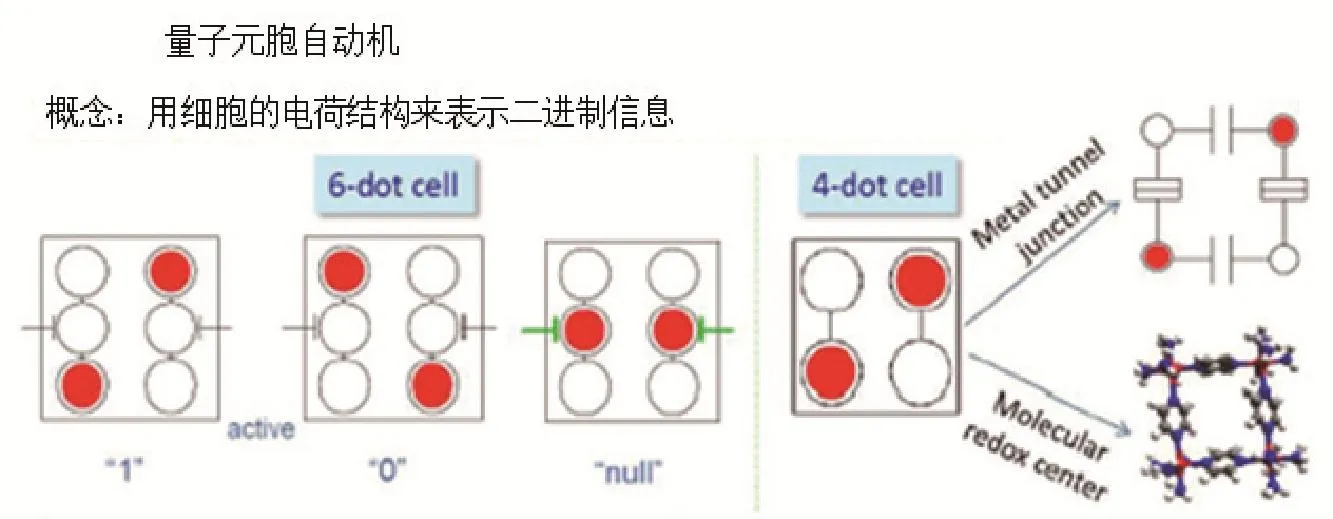

4.4量子元胞自动机(Quantum Cellular Automata)

图3 量子元胞自动机工作原理

通过改变元胞编排结构来表示二进制。相邻的元胞由于库仑耦合效应趋向于对齐一致,从而实现信息的传递。已有通过实验演示的半导体、分子、磁性点类型的量子元胞自动机提供了低功耗、新型信息处理方式、传输机制以及多数决操作。QCA量子电路是未来实现量子计算机的技术之一。

挑战在于工作温度的限制以及在极端尺寸下的图形构造。

4.5原子开关(Atomic Switch)

原子开关基于两电极间的金属原子桥的形成与湮灭,从而形成门(相当于栅极)控开关模式。

图4 原子开关模型

优势:高扩展性,低操作电压和能耗,作为记忆体的双端器件应用时与conductive-bridge RAM (CBRAM)类似,相对来说存在低制造成本的可能,3D 堆叠结构。

挑战:需要提高三端器件所具有的性能(速度、耐久度、均匀度),稳定性和高可变性需要被考量,速度由电极活性表面的离子输运和电化学反应决定,需要对工作机制有更深入的了解。

4.6自旋场效应晶体管(SpinFET)

利用电子的自旋方向来携带信息。相关技术也是未来实现量子计算机的技术之一。

优势:旋转的自由度使额外的信号调制和控制成为可能,具有场效应晶体管的结构且与 CMOS 工艺兼容,理论上有更小的传输耗散,无挥发性,可编程性。

挑战:磁性材料及其制造工艺,需要高效率的自旋注入和侦测来实现足够多的开/关比例,自旋轨道间的栅极调制的强度,自旋弛豫及其寿命。

4.7石墨烯场效应晶体管(Graphene FET)

石墨烯场效应晶体管是蜂窝状的单原子碳结构。优势:高迁移率(有构造更快速 FET 的潜力);挑战:带有电压增益的电路结构难以实现,石墨烯没有带隙(band gap),开/关电流比欠佳,所以这方面也有各种各样的研究尝试。

4.8碳纳米管场效应晶体管(CNT)

碳纳米管是由石墨烯薄片卷起来的纳米级直径的圆管。

优势:在RF电路中的应用较有前景,在表面的一维输运,可实现极佳的沟道控制和高线性度(Id~Vgs),较大的平均自由程,有地热噪声以及操作在 THz 频率的潜力。

挑战:现有实现的高性能碳纳米场效应晶体管内是有金属喷镀的,需要设法摆脱;一个碳纳米管只能承载 10~30 μA 的电流,因此需要几百个碳纳米管来达到 mA 级别的漏端电流;已有碳纳米场效应晶体管在1.3 GHZ处有11 dB的增益;大规模制造工艺仍有待发展。

4.9纳米线场效应晶体管(Nanowire FET)

优势:相比CMOS,对载子/沟道有更好的控制;当直径很小(几个纳米)时,有一维(弹道)的传输效果;相比CMOS有大约4倍的速度提升;环形栅在高速器件中很有前景。

挑战:可靠度和器件的可复制性;达到mA级别的电流需要很多单一器件的排列;仍未有RF应用的实现。

5 结论

由本文的研究分析可以得出,目前集成电路的发展还在遵循摩尔定律,但在未来几年后,摩尔定律将可能会以另外的形式出现,集成电路性能提升的方式可能会发生改变。“摩尔定律”的本质实际上是对人类创造力的一种肯定,是对人类社会发展过程中所经历的信息化革命的时段推测的理论指导。人类利用自然、改造自然的愿望永远没有止境,创新也不会有止境。只要人们能够在改造世界的步伐中不局限于已有的事物,而是不断地去创造和突破,“摩尔定律”就会延续下去,就不会终结。相信在不久的未来,人类在集成电路领域一定能够找到一种全新的方式,使得电子信息产业继续向前发展。

参考文献:

[1] Nam Sung Kim. Leakage current:Moore’s Law Meets Static Power[J]. The IEEE Computer Society, 2003,12: 68-75.

[2] 沈建苗. 摩尔定律是否有未来[J]. 微电脑世界,2011,(9):12-15.

[3] 齐书阳. 摩尔定律会终结吗[J]. 电脑爱好者,2013,(8).

[4] 赖凡. 第十七届全国半导体集成电路、硅材料学术会议[C]. 三亚,2011.9-12.

[5] 杨蕊,程博闻,康卫民,等. 碳纳米管的功能化及其在复合材料中的应用[J]. 材料导报,2015, 29(7): 47-51.

[6] 陈自强. 战胜CMOS Scaling的研究挑战:半导体业发展方向[J]. 中国集成电路,2007,16(1):20-23.

The Past, Present and Future of Moore's Law

DAI Jinwen, MIAO Xiaoyong

(NantongFujistu Microelectronics Co., Ltd, Nantong 226006, China)

Abstract:The past, present and future of semiconductor technology Moore's law are analyzed in the paper, focus on the formation and development of Moore's law and the diffi culties and challenges in basic physics, lithography, manufacturing cost and power consumption,and discussed the development direction and the scope of adaptation of " More-Than-Moore ", and Moore's law in the future.

Keywords:moore's law; chip size limit; more-than-Moore; beyond CMOS

中图分类号:TN303

文献标识码:A

文章编号:1681-1070(2015)10-0030-05

收稿日期:2015-9-2

作者简介:

戴锦文(1961—),男,江苏南通人,通富微电项目办主任,江苏省半导体行业协会副秘书长,长期从事半导体行业分析、科技项目管理工作。