基于USB3.0的多相位帧同步电路设计

刘 亮,林福江,杨 莹(中国科学技术大学 电子科学与技术系,安徽 合肥 230027)

基于USB3.0的多相位帧同步电路设计

刘 亮,林福江,杨 莹

(中国科学技术大学 电子科学与技术系,安徽 合肥 230027)

USB3.0帧同步电路设计的关键在于高速率下串行数据流的帧定位与数据对齐,需同时兼顾高效率和低功耗。使用Verilog HDL描述语言设计了一种基于多相位和并行检测技术的帧同步电路,重点对并行检测电路进行分析和优化。该电路在ISE中编译和仿真,结合数据进行分析,并将仿真结果进行比较验证,证明该电路能满足帧同步的速率和时序要求。

USB3.0;多相位技术;并行检测;帧同步;Verilog HDL

0 引言

近年来,USB(通用串行总线)作为一种标准的传输接口[1],应用十分广泛。从2008年11月首次发布USB3.0规范以来,在快速存储、大数据高速传输等领域都出现了USB3.0[2]的身影,延续USB2.0时代的辉煌,继续展现出强大的竞争力。与USB2.0高速版本的设计[3]相比,USB3.0的复杂度大大增加,尤其是5 Gb/s的差分传输速率成为设计者重点考虑的问题之一。高速率、低功耗是当前芯片设计的主流趋势,在提高器件工作频率的情况下,更需要有效地控制功耗。本文将介绍多相位技术在USB3.0帧同步系统设计中的应用,通过对并行检测电路的优化,实现系统复杂度、实用性以及功耗方面的平衡。

1 接收电路的功能与分析

USB3.0接收部分的功能结构如图1所示。

为了抑制共模干扰,USB3.0的数据采用差分输入,经过双端转单端电路,分为两路送入时钟数据恢复(Clock Data Recovery,CDR)模块和串转并模块。

图1 接收模块功能结构图

CDR模块完成从串行数据流中提取时钟信号的功能,送至时钟管理模块,得到625MHz、500MHz和125MHz时钟信号供其他模块使用。

帧同步模块完成对高速串行数据流的并行低速化,通过并行检测帧定界符得到帧同步信号,同时控制时钟管理模块的时钟输出,完成数据的对齐处理,经过弹性缓冲模块得到500 MHz、10 bit的并行数据流。

帧同步模块输出的并行数据流先后通过8 b/10 b解码模块、解扰模块得到 500 MHz、8 bit数据流与控制信号;通过位宽拼接处理最终得到125 MHz、36 bit的数据流(其中包含32 bit数据和4 bit控制位)写入数据FIFO,供LINK层读取使用。

2 帧同步模块的设计及要点

帧同步模块是接收模块的难点,主要由以下功能模块组成:多相位串转并模块、并行帧定界符检测模块、并行数据流对齐模块、弹性缓冲模块。各大模块及相关时钟结构电路如图2所示。其中,串转并模块和并行检测模块是本设计的优化重点。电路选用 XLINX公司的Virtex-5芯片作为设计与测试平台。

图2 帧同步模块结构图

2.1 基于多相位技术的串转并模块设计

传统的低速串转并电路采用移位寄存器实现,电路的功耗与工作时钟成线性关系。USB3.0的输入信号高达5 Gb/s,移位寄存器产生的功耗很大,并且工艺要求很高,而 0.15μm CMOS工艺条件只能达到3.0 Gb/s的频率,继续提升工作频率极易引起电路的不稳定。因此,有效地降低器件工作时钟频率,在降低器件功耗和降低生产工艺要求方面具有重要意义,同时对相同工艺下提升器件的性能也非常有效。

多相位技术的原理为:利用PLL将CDR恢复得到的f频率时钟分成多个频率为f/N,彼此相位间隔为360°/N的时钟信号,利用这N个时钟对串行数据流进行分时采样,在相移为 0°的 f/N频率时钟同步下,合并为N bit的数据。这种技术的优势在于:在不增加原有功能复杂度的情况下,利用PLL降低CMOS器件的运行时钟,从而降低功耗。PLL的引入,能够一定程度上改善恢复时钟的抖动。在PLL设计中,当分频值N取2的幂次方时,可有效简化设计,在此N取2^3=8。

使用 Verilog HDL[4]语言对 1:8多相位串转并模块进行描述,部分关键代码为:

always@(posedge clk_XXX or negedge rstn)begin

if(!rstn)pdata[n]<=1′b0;

else pdata[n]<=sdata_i;

end

其中 clk_XXX代表 clk_000~clk_315这 8个相位间隔为45°的时钟。采样得到的数据以8 bit为单位送入并行检测模块。

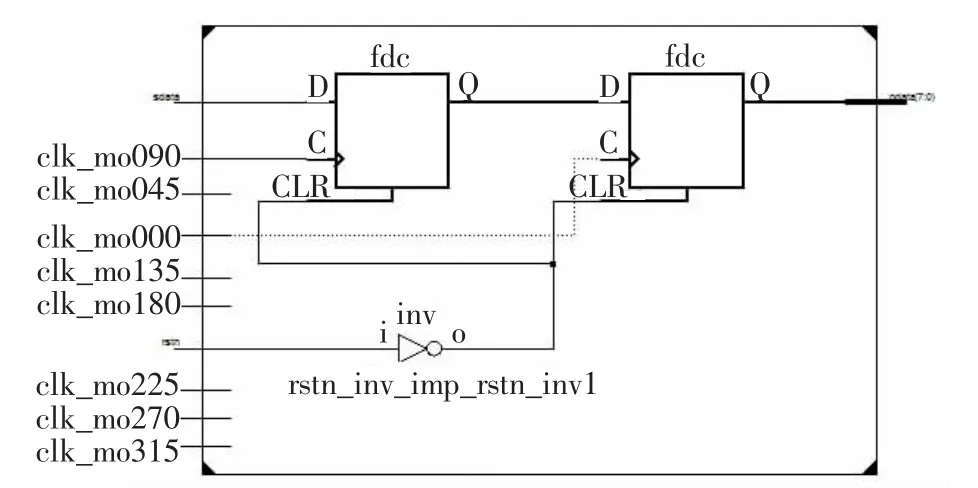

经过 ISE综合后模块非常简洁,RTL电路如图 3所示。

2.2 优化并行帧定界符检测模块设计

根据 USB3.0规范,传输的数据采用控制码 K28.5作为帧定界符。它的特殊性在于:在所有选定使用的控制码与数据码中,有且只有K28.5存在5个连续的高电平信号‘1’。因此,许多采用8 b/10 b编码的传输系统都将其作为帧定界符。在传输的数据流中,检测到“001111010”就可以判定新一帧的开始。

图3 串转并模块RTL图

USB3.0发送部分的数据经过8 b/10 b编码后,数据块由8 bit为单位转换为 10 bit为单位,常用的做法为:接收端在f/10的工作时钟驱动下,并行检测10个相邻位置的10 bit数据。通过并行的方式,从而降低电路的运行速度要求,实际是以空间换时间的思想。虽然电路工作频率降低,但整体功耗因电路规模的相应增大而没有减小。

通过对并行检测电路的分析可以发现:假定串转并模块采用1:N结构,并行检测模块对M bit数据块进行检测,检测单元的规模为N×M bit。在并行度M bit相同条件下,N越大,需要的逻辑运算单元就越多。串转并模块选择 1:8的比例,不仅可以简化 PLL设计,同时也能降低逻辑运算单元的消耗。

其次,减少检测数据块的并行度M也是重要途径。根据K28.5的特点,在数据正确传输的前提下只需检测其中 7 bit,即“0011111”或者“1111101”[5]就能判定为K28.5码。取M=7 bit,则只需要8×7=56 bit逻辑运算单元,相比未优化前的 10×10=100 bit逻辑运算单元减少44%,简化了电路的结构,能够一定程度地提升器件的运行效率。

2.3 并行数据流对齐模块设计

并行检测模块检测到帧定界符后,需通过锁定单元[6]锁定当前的数据流分块方式,锁定单元结构设计如图4所示。

图4 锁定单元结构图

锁定机构的工作原理为:当某一检测单元成功检测到帧定界符K28.5的前7 bit,便可推断数据流3 bit后即为实际所需数据流的起始位置,锁定单元在下一时钟沿锁定当前检测结果不再更改,并根据锁定的结果在对应位置每次取出10 bit并行数据送至下级电路,直到检测到当前帧结束或者复位解除锁定。

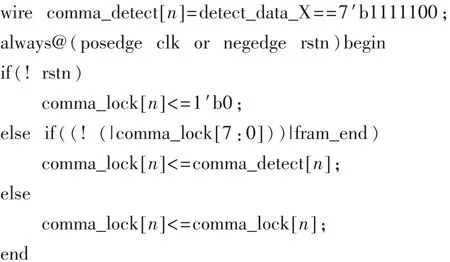

锁定单元关键代码如下所示:

其中,n为 0~7,detect_data_X表示第 0~7个检测单元。

由于串转并模块输出为8 bit并行数据,根据USB3.0规范,实际送入弹性缓冲须为10 bit,因此需要使用位宽转换电路对数据流位宽进行转换。方法为:将8 bit位宽拼接成 40 bit位宽,通过判断锁定单元输出的 comma_lock信号,重新选取对齐后的 40 bit,最后分割成实际需要的10 bit位宽输出。

3 仿真及验证

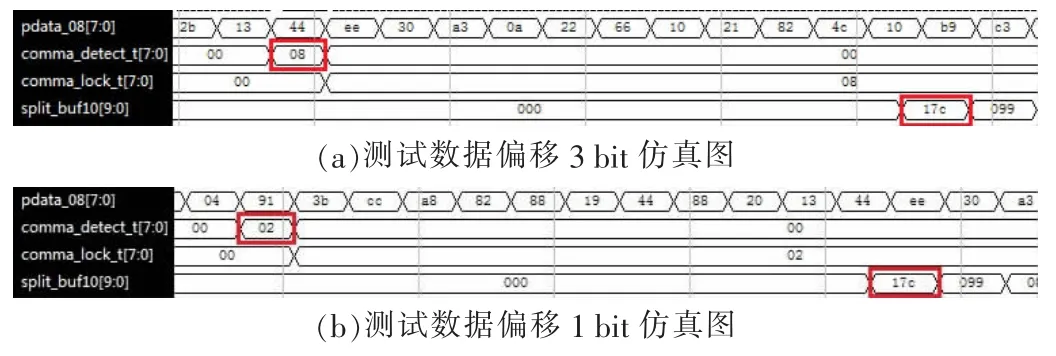

编写test bench,改变串行数据流中 K28.5的位置,模拟发送数据帧,在ISim中对设计的电路进行仿真验证,仿真波形如图5所示。

图5 仿真结果

经过8组不同位置数据(在此只贴出2个结果)的对比可以看出,在不同的数据流中,帧定界符 K28.5的位置总能够被正确检测,通过数据对齐模块后成功分离出后续模块所需 10 bit并行数据,结果完全正确,且满足运行500 MHz的运行速度要求。

4 结论

多相位技术能够显著降低器件的工作频率,从而减少功耗,同时也可以降低制造器件的工艺难度;并行处理技术是当前高速电路发展的趋势,合理地利用编码自身特点,进行针对性的优化,能够使电路更加简洁,运行速度更快。这两者对于提高器件的性能而言,都具有十分重要的现实意义。

[1]Don Anderson Dave Dzatko.USB系统体系(第二版)[M].北京:中国电力出版社,2003.

[2]Hewlett-Packard Company,Intel,et al.Universal serial bus 3.0 specification Revision1.0[R].USA:Hewlett-Packard Company.2008.

[3]王永,白雪飞,方毅,等.基于 UTMI协议的 USB2.0收发器逻辑电路设计[J].微型机与应用,2014,33(10):13-15,19.

[4]夏字闻.Verilog数字系统设计(第二版)[M].北京:北京航空航天大学出版社,2008.

[5]杨卿.Rapid IO高速互联接口的设计研究与应用[D].成都:电子科技大学,2009.

[6]刘昭,金德鹏,曾烈光.基于连续性判别的并行帧同步系统[J].电子学报,2005,33(7):1177-1182.

Design for transm ission circuit in USB3.0 based on multi phase technology

Liu Liang,Lin Fujiang,Yang Ying

(School of Information Science and Technology,University of Science and Technology of China,Hefei 230027,China)

The key point of designing USB3.0 frame synchronization circuit is that frame and data alignment of serial data stream should be designed with high efficiency and low power consumption at high speed.The paper introduces a frame synchronization circuit based on multi-phase sampling and parallel detection technology designed with Verilog HDL.Our method focuses on the analysis and optimization of parallel detection circuit.The circuit is compiled and simulated in ISE.Compared with data,the simulation results show that the circuit can meet with the speed and timing requirements of frame synchronization.

USB3.0;multi-phase technique;parallel detection;frame synchronization;Verilog HDL

TP47

A

1674-7720(2015)24-0035-03

刘亮,林福江,杨莹.基于USB3.0的多相位帧同步电路设计[J].微型机与应用,2015,34(24):35-37.

2015-09-27)

刘亮(1983-),男,硕士,主要研究方向:数字集成电路设计。

林福江(1958-),男,博士,博士生导师,主要研究方向:微波、微电子建模与设计。

杨莹(1992-),女,硕士,主要研究方向:数字集成电路设计。