基于FPGA的FIR滤波器设计方法研究*

张 亮,刘宇红

(贵州大学 大数据与信息工程学院,贵州 贵阳 550025)

基于FPGA的FIR滤波器设计方法研究*

张 亮,刘宇红

(贵州大学 大数据与信息工程学院,贵州 贵阳 550025)

结合FPGA内部资源特点,提出一种高速高阶FIR滤波器设计的改进算法。首先,分析了FIR滤波器的基本结构模型,对应的响应速率,以及占用资源情况等。其次,利用 FPGA内部查找表易于实现分布式算法的特点和寄存器易于实现流水操作的特点,提出了一种在FPGA中实现高速高阶FIR滤波器的加流水操作的并行分布式算法,并且评估引入流水操作后FPGA内部的资源消耗。最后,通过ISim仿真分析响应速率,通过MATLAB仿真验证算法的可行性。

FIR滤波器;分布式算法;查找表;流水线

0 引 言

FIR滤波器被广泛应用于音频处理、语音处理、信息系统等各种系统中[2],其性能对整个系统减少或消除无关信号干扰起到至关重要的作用。因此,FIR滤波器的优劣程度在很大程度上决定了产品的优劣程度。FPGA因其运算速度快、便于实现并行设计、分布式算法以及流水线操作的优点,非常适合用来设计高阶高速FIR滤波系统。

具有线性相位的FIR滤波器(后文所说的FIR滤波器均指其具有线性相位),以M为奇数、单位取样响应为偶对称的FIR滤波器为例y:

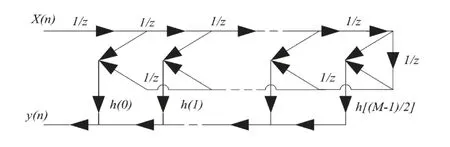

图1 FIR直接型结构

在FPGA中实现直接形结构FIR滤波器,具体实现算法有以下三类:串行结构,并行结构和分布式结构。

1 串行算法结构

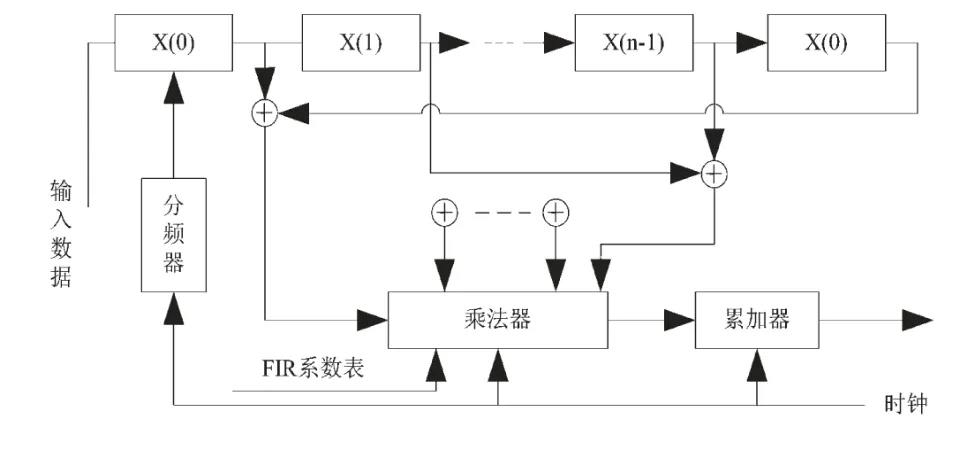

串行结构是用串行的方式把输入延时序列与相应的系数乘积的结果进行累加并输出。串行结构的基本特点:需要用到一个乘法器;对于高阶FIR滤波器设计,系统时延较大,实时性低,整体占用硬件资源少。基本结构如图2所示。

图2 半串行FIR滤波器结构

2 并行算法结构

并行结构是利用并行的方式完成累加操作,在每一个并行数据路上采用一个乘法器把数据与系数相乘,再把各路乘积结果相加输出。并行设计算法具有最快的运算速度,结构如图3所示。如果要设计一个M阶并行结构FIR滤波器,消耗的乘法器资源为M/2个。随着阶数M增大,消耗的硬件资源将成倍增加。因此,虽然并行结构是最快的数据处理方式,但并不是最好的实现方式。

图3 并行FIR滤波器结构

3 分布式算法

分布式算法是一种针对乘加运算专门提出来的算法。这种算法的应用条件需要乘法运算中某一个因子总为常数。前面说到FIR滤波器的本质是对输入序列做大量的乘加运算,并且设计好的FIR滤波器系数都可以事先在MATLAB中仿真得到。因此,把分布式算法用到FIR滤波器的实现中非常恰当。

3.1分布式算法

对于乘加运算:

式中,c(m)表示常数集c中的第m个元素,0≤m≤M-1,x(m)表示无符号二进制B位的变量集,xb(m)=0或1,表示x(m)的第b位,则x(m)的展开式为

将式(2)带入式(1)得:

简单变形得:

变量集x中不同元素的第b位和对应的常量集c中相应元素的乘加组合,并且y的结果随着xb(m)的改变取不同值,这样y的可能取值有2M种情况。以上这种理解方式可以用FPGA中的查找表结构很好地表达出来。

具体而言:把xb(0)、xb(1)、…、xb(M-1)设置为查找表的输入地址,把放在查找表中能够被正确寻址的方式排列,再通过一些附加逻辑以实现输入不同的x变量集中的序列,从而计算对应的y值。当把x(m)看作B位有符号二进制数时,x(m)的表达式:

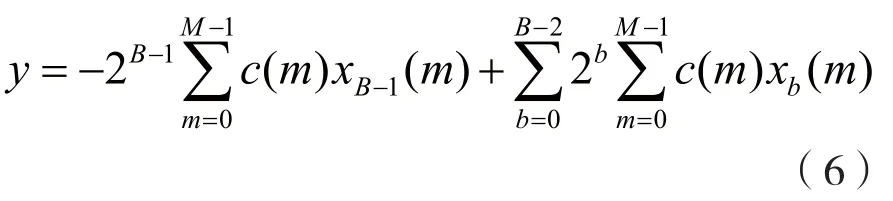

这时,y的表达式如下:

以上分析了变量集x为无符号与有符号情况下的具体过程,可以很清晰得到如图4所示结构。

图4 分布式算法结构

3.2改进的并行分布式算法

用以上讨论的分布式算法设计一个长度为M的FIR滤波器,存在两方面的问题:设计需要2M个存储单元,并且随着长度M增加,消耗的存储单元的数量呈指数倍增加,对于高级FIR滤波器的设计,这种方法显然不合理;当变量x(m)的位数B很大时,所设计的流水的级数也会变长,使最终的输出结果时延较大。因此,需要改进分布式算法,让其在消耗较少硬件资源的情况下尽量提高数据处理速度。

以上分析给我们提供了三个改进思路:第一,能否通过多级分解使M的数值变小;第二,能否把一个串行的流水累加过程变为一个并行的计算过程;第三,为避免因为并行过程消耗的硬件资源过多,能否根据实际应用需求适当加入流水设计。

3.2.1改进一

根据第一条改进思路,设M=R×N,带入式(1):

把式(5)带入式(7):

取式(8)中第r项进行分析:

显然,以上展开式在FPGA中可以通过构造一个N输入的查找表实现。

3.2.2改进二

把具体的实现过程由串行方式变为并行方式,即每一个xb(rN-N)、xb(rN-N+1)、…、xb(rN-1)的组合都用一个查找表,则需要B个N输入的查找表,而总共则需要B×2N个存储单元。

3.2.3改进三

在算法设计中适当加入流水操作,把B个N输入查找表减少为B/p个N输入查找表(B/p为整数),并在后级设计逻辑电路把p级流水输出结果相加,作为等效的N输入查找表的结果。随着流水级数的增加,存储单元的数量会急剧减少。当然,流水操作的级数P值也不能无限增加,而应视系统要求响应速度和芯片选型综合考虑。

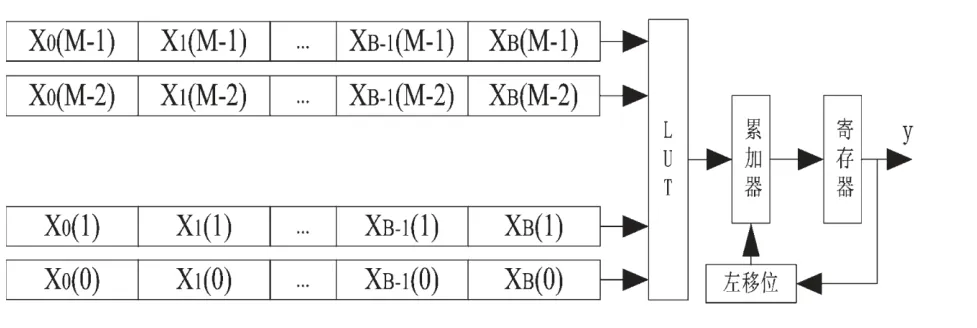

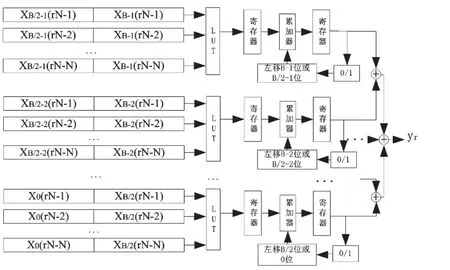

结合以上三条改进思路,得出最终改进的加入流水的并行分布式算法结构图,如图5所示。

图5 加入二级流水的并行分布式算法结构

4 详细设计过程

以设计31阶FIR低通滤波器,截止频率为500 Hz,滤波器系数13位量化,输入数据x(m)的13位量化为例,来说明以上改进设计FIR滤波器的方法。

滤波器的长度M=32。由第一条改进思路,取R=8,N=4,即一个深度为232的大查找表被分为若干个深度为24的小查找表;输入数据的量化位数为13位,从图1的直接型FIR滤波器的结构图可知,A(m)=x(m)+x(31-m)为14位二进制有符号数。根据第二条并行设计的改进思路,式(8)和式(9)的展开式的每一项都可以用一个深度为16的查找表把中括号里面的部分计算出来,2的系数次方运算可以用移位操作实现,总共需要的4输入查找表的个数为R×B=8×14=112个。

现在考虑在全并行的分布式计算过程中加入二级流水操作,使输入数据的速率为FIR滤波器处理速率的一半。第一级流水处理A(m)的低7位,第二级流水处理A(m)的高7位,用一个计数器计数当前流水操作的状态为0还是1,以便于对查找表输出的结果进行移位操作。加入二级流水操作后,所需的查找表个数为R×B/2=56个,比全并行分布式设计要少用56个4输入15位查找表。随着流水级数的增加,所用查找表会迅速减少,这对于在目标器件门数较少的FPGA上设计高阶快速响应FIR滤波器有很大的指导意义。

5 实验仿真分析及验证

验证采用Xilinx公司的xc6slx9-2csg225型号FPGA为目标器件。表1列出利用各种算法实现的31阶串行结构FIR滤波器占用硬件资源的情况。

表1 不同算法实现FIR滤波器的性能对比

由表1各行对比可知,经过改进的分布式并行加二级流水方式实现的FIR滤波器,在消耗硬件寄存器数量和查找表数量上都相对较少,并且在系统频率一定的情况下,其数据吞吐速率也较高,能够处理高速数据。

用MATLAB软件产生包含两个频点的正弦波测试信号文本,在ISim仿真环境中通过din[12:0]输入,把输出结果dout[32:0]写入到文本中,并在MATLAB中画出FPGA完成滤波前后的频谱图以及时域波形图,结果依次如图6、图7所示。在图6中,当滤波器开始正常工作时,由于加入了二级流水操作,它每两个时钟周期输出一个滤波结果。滤波器在前一个时钟周期内,把A(m)的低7位送入查找表的地址线中进行查表操作,并把查表结果放在寄存器中保存;在第二个时钟周期内,把A(m)的高7位送入查找表地址线中进行查表操作,并把查表结果进行移位操作,最后把两个时钟内所得的结果相加输出,以此实现滤波过程。在图7中,输入信号有两个频点,经过高阶FIR低通滤波器滤波后,频率为700 Hz的频点成分被完全滤除,从时域波形图中也可以看到滤波后的信号只包含单一频点成分。表1中列出的实验结果和图6、图7的仿真实验结果表明:加流水操作的并行分布式算法能够利用FPGA内部的大量其它硬件资源替代内部珍贵的专用DSP硬核资源,增加了系统设计的灵活性;加流水操作的并行分布式算法能够有效的利用FPGA内部的查找表资源和寄存器资源,并且随着FPGA的发展,其内部查找表的输入端口数不断变化,因此可以结合查找表的特点,利用以上算法设计出更加节约资源的高速高阶FIR滤波器;加流水操作的并行分布式算法设计的高速高阶FIR滤波器在响应速率上接近于全并行结构的FIR滤波器,并且具有良好的滤波性能。

图6 ISim中仿真结果

图7 实验前后对比

6 结 语

本文对高速高阶FIR滤波器的设计方法进行研究,对目前常用的几种算法进行分析,并通过理论分析,提出一种适用于高速高阶FIR滤波器设计的算法,最后在所选用的目标器件上实现,验证了加流水操作的并行分布式算法的有效性,以及对高速高阶FIR滤波器设计的指导作用。

[1] Albicocco P,Cardarilli G C,Nannarelli A,et al.Degrading Precision Arithmetic for Low-power FIR Implementation[J]. Circuits and Systems,2011,8(01):1-4.

[2] 程佩青.数字信号处理教程[M].北京:清华大学出版社,2001. CHENG Pei-qing.Digital Signal Processing Tutorial[M]. Beijing:Tsinghua University press,2001.

[3] 杨大柱.MATLAB环境下FIR滤波器的设计与仿真[J].电子技术应用,2006,32(09):101-103. YANG Da-zhu.Design and Simulation of FIR Filter in MATLAB Environment[J].Application of Electronic Technology,2006,32(09):101-103.

[4] 田耘,徐文波.无线通信FPGA设计[M].北京:电子工业出版社,2008. TIAN Yun,XU Wen-bo.Wireless Communication FPGA Design [M].Beijing:Electronic Industry Press,2008.

[5] 王英喆,王振宇,严伟等.全并行FIR滤波器的FPGA实现与优化[J].电子设计工程,2015,23(22):94-97. WANG Ying-zhe,WANG Zhen-yu,YAN Wei,et al.The Realization and Optimization of FPGA for All Parallel FIR Filters[J].Electronic Design Engineering,2015, 23(22):94-97.

[6] 刘凌,胡永生.数字信号处理的FPGA实现[M].北京:清华大学出版社,2003. LIU Ling,HU Yong-sheng.FPGA Implementation of Digital Signal Processing[M].Beijing:Tsinghua University press,2003.

[7] 罗朝霞,高书莉.CPLD/FPGA设计应用[M].北京:人民邮电出版社,2007. LUO Zhao-xia,GAO Shu-li.CPLD/FPGA Design and Application[M].Beijing:People's Posts and Telecommunications Press,2007.

[8] 赵宏峰.中频数字化接收机中的下变频器研究[D].南京:东南大学,2006. ZHAO Hong-feng.Research on Down Converter in Digital Receiver[D].Nanjing:Southeast University,2006.

[9] 屈有萍.基于FPGA的数字下变频研究实现[D].西安:西安电子科技大学,2007. QU You-ping.Research and Implementation of Digital Down Conversion based on FPGA[D].Xi'an:Xi'an Electronic and Science University,2007.

[10] 刘朋全.基于FPGA的FIR数字滤波器的设计和实现[D]. 西安:西北工业大学,2006. LIU Peng-quan.Design and Implementation of FIR Digital Filter based on FPGA[D].Xi'an:Northwestern Polytechnical University,2006.

张 亮(1991—),男,硕士研究生,主要研究方向为FPGA及嵌入式技术开发;

刘宇红(1963—),男,硕士,硕士生导师,教授,通讯作者,主要研究方向为语音与图像处理、DSP与嵌入式微处理器的应用与研究。

FIR Filter Design based on FPGA

ZHANG Liang, LIU Yu-hong

(College of Big Data and Information Engineering, Guizhou University, Guiyang Guizhou 550025, China)

Combined with the characteristics of FPGA internal resources, a modified algorithm for design of high-order and high-speed FIR filter is proposed. Firstly, the basic structure, corresponding response speed and resource consumption of the FIR filter are analyzed, then based on easy realization of the distributed algorithm by FPGA internal look-up table and pipeline operation by internal registers, a parallel distributed algorithm added with pipeline operations is proposed, thus to realize the high-order and high-speed FIR filter based on FPGA, and additionally, the FPGA internal resource consumption with introduction of pipeline operations also evaluated. Finally via Isim simulation the response speed is analyzed, and via MATLAB simulation, the feasibility of the proposed algorithm verified.

FIR filter; distributed algorithm; look-up table; pipeline technology

Guizhou Province Electronic Component Detection Network Platform; QianKe Platform [2012]4005

TN713

A

1002-0802(2016)-08-01083-05

10.3969/j.issn.1002-0802.2016.08.024

2016-04-25;

2016-07-26

date:2016-04-25;Revised date:2016-07-26

贵州省电子元器件检测网络平台;黔科平台【2012】4005