一种基于FPGA的视频采集系统设计

范超 赵琳 李真

摘要:该文设计一种基于FPGA的视频采集系统。在本系统中FPGA作为系统的核心控制部件,控制图像传感器MB86S02进行视频采集,并通过SDRAM控制器将采集的视频信息存储在外部高速SDlLAM中以备后续使用。系统采用模块化的设计方法,将整个系统划分为视频采集单元和视频存储单元,并在此基础上进行各功能模块的设计以及各功能模块间数据接口的设计。

关键词:视频采集;FPGA

1概述

在数字图像处理中,图像的采集是第一步,它的好坏直接影响到图像处理的性能。视频信号中除了包含图像信号外,还包括了行同步信號、行消隐信号、场同步信号、场消隐信号以及槽脉冲信号、前均衡脉冲、后均衡脉冲等,因此对视频信号的A/D转换电路非常复杂。

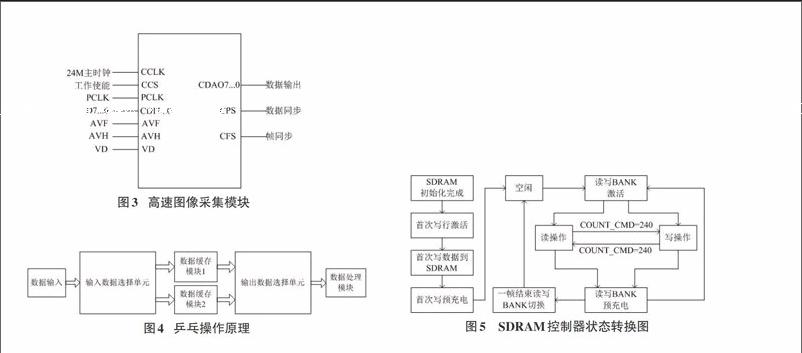

本文采用富士通公司的MB86S02图像传感器作为视频采集器,在FPGA的控制下进行视频采集,并通过乒乓操作实现视频数据的存储,系统总体框图如图1所示。MB86S02片内集成了图像采集的所有前端处理,可以直接输出数字信号,大大简化了图像应用系统的设汁。

2视频采集模块设计

本系统的视频采集模块由MB86S02图像传感器和FPGA芯片组成,MB86S02在FPGA的控制下进行视频信号的采集。首先需要对MB86S02的寄存器进行配置,本系统中MB86S02寄存器采用默认值。MB86S02的硬件接口如图2所示。

如图2所示,FPGA通过控制信号和视频信号连接MB86S02图像传感器和外部高速SDRAM。FPGA控制MB86S02图像传感器进行视频采集,并通过SDRAM控制器将采集的视频信息存储到外部高速SDRAM中,以备后续使用。

图像采集模块接口信号设计如图3所示,在图3模块接口中,由MB86S02芯片输出引脚提供的信号如下:

1、数据线(D0…7):按次序输出格式为YUV422的图像数据,宽度为8bits;

2、数据同步时钟(PCLK):每个时钟周期,当高电平时,就输出一个8位图像数据;

3、有效帧信号(AVF):在节能模式下使用,“1”代表帧有效,“0”代表帧无效,在普通模式下总为“1”;

4、行同步信号(AVH):“1”代表行数据有效;

5、帧同步信号(AVF):“1”代表帧数据有效。

接口的其他信号还包括:

1、24M主时钟(CCLK):平台主时钟;

2、工作使能(ccs):“0”开始采集,“1”停止采集;

3、数据输出(CDAO):输出有效图像数据,宽度为8bhs;

4、数据同步信号(CPS):下降沿输出有效数据。

3视频缓存模块设计

针对视频图像数据量大的特点,系统需要对采集到的视频图像信息进行缓冲处理,缓冲电路常采用以下几种实现方式:

1)双口RAM结构。双口RAM具有两套完全独立的数据地址线,可同时对该存储器进行随机访问;

2)FIFO结构。FIFO即先入先出队列,可以进行双端操作,数据先进先出,不能进行随机性访问;

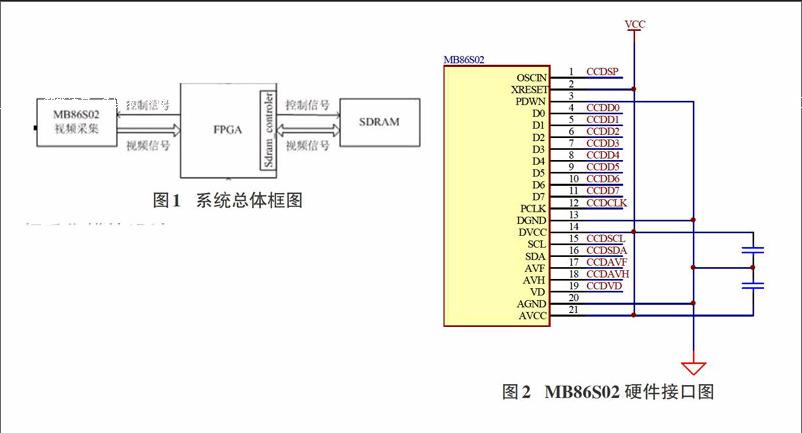

3)乒乓缓存结构。乒乓缓存结构的工作原理如图3.1所示,输人数据流通过输人数据选择单元等时地将数据流分配到两个数据缓冲区。在第一个缓冲周期,将输入的数据流缓存到数据缓冲模块1上。在第二个缓冲周期,通过输入数据选择单元的切换,将输入的数据流缓存到数据缓冲模块2上。同时,将数据缓存模块1缓存的第一个周期的数据通过输出数据选择单元的选择,送到运算处理单元进行处理。在第三个缓冲周期,再次切换数据的输入与输出缓冲模块。如此循环,周而复始。

由于大容量的RAM和FIFO价格昂贵,性价比不高,为满足系统的实时性要求,本系统采用SDRAM实现的乒乓缓存结构进行数据缓存。如图4所示数据缓存部分是数据输入与数据处理之间的通道,输入的数据首先经过缓存再进行数据处理,数据缓存部分的设计是确保数据输入与数据处理间无缝衔接的关键。

如图4所示,乒乓操作的工作原理是通过输入数据选择单元将输人数据流存储到两个数据缓存模块中并通过输出数据选择单元分别从两个数据缓存模块中读取数据。

乒乓操作多采用两片存储器芯片来实现,本系统通过对SDRAM的不同BANK分别执行读写操作在一片SDRAM芯片上实现了乒乓操作。SDRAM共分为4个BANK,可以将SDRAM的不同BANK分别作为读写缓存,分别执行读写操作。当读取第一帧图像时使用SDRAM的1、2 BANK作为读缓存,3、4 BANK为写缓存,一帧图像读写完毕时切换BANK的读写操作,读取第二帧图像时SDRAM的3、4 BANK切换为读缓存,1、2 BANK切换为写缓存,这样即在一片SDRAM芯片上实现了读写缓存。由于SDRAM只有1组数据/地址线,所以不能同时对SDRAM进行读写操作,设计中采用分时的方式,通过在控制器中设计了一个指令计数器来切换读写操作,实现乒乓操作。SDRAM控制器状态转换图如图5所示。

4结论

本设计方案已经经过了硬件验证,达到了预定的设计要求,实现了大数据量的实时采集及存储功能,为图像的后续处理打下良好的基础。