一种处理器体系结构级功耗评估工具设计

刘志宏张星张洪峰

(武汉第二船舶设计研究所武汉430064)

一种处理器体系结构级功耗评估工具设计

刘志宏张星张洪峰

(武汉第二船舶设计研究所武汉430064)

体系结构级功耗评估能让设计者在设计前期对处理器进行架构权衡,极大地减少设计开销。论文从体系结构级、电路级和工艺级三个层次,结合工艺缩放比例原理和RTL反馈建模方法,进行处理器功耗建模;在功耗模型基础上,实现体系结构级功耗评估工具的设计;通过速度、精度分析,表明该体系结构级功耗评估工具在极大提升了功耗评估速度的前提下保证了功耗评估精度。

体系结构级;功耗模型;功耗评估

Class NumberTP302

1 引言

体系结构级功耗评估对于处理器设计是非常重要的,它能让设计者在设计前期对处理器进行架构权衡,极大地减少设计开销。试想若一款处理器设计到工艺级才发现其功耗指标不满足,用RTL级和工艺级手段并不能解决,而需返回到体系结构级重新设计,其代价是非常大的。

目前有许多商业化功耗评估工具,如晶体管级的HSPICE、PSPICE、NanoSim等,门级或RTL级的Power Designer、RTL Compiler、Blast Power等,这些工具能在不同层次上提供较准确的功耗评估,但它都要求电路完整的硬件描述,RTL级的verilog代码、门级网表甚至更低层次的电路设计,不可能在处理器总体架构规划阶段及时地作出功耗评估,同时这些工具进行功耗评估占据极大的内存空间,需要相当长的时间;指令级功耗评估[1~2]和系统级功耗评估[3]速度非常快,但没有体现出处理器的体系结构设计,一般适用于算法开发。而体系结构级功耗评估在微体系结构基础上展开,能有效地保证评估精度,同时评估效率也极高。

事实上,越来越多的处理器设计者在关注体系结构级功耗分析。如Brooks等开发的Wattch[4]是一款经典的体系结构级功耗分析工具,但其研究对象限于Alpha这种以动态电路为主的高功耗处理器,并不适合评估所有处理器,同时静态功耗评估不准确。SimplePower[5]是一种执行驱动、周期精确的体系结构级功耗评估工具,对于功耗单元的功耗计算使用预定义的跳变模型,计算比较详细准确,但其对存储模型使用经验功耗模型,计算太过粗略。

本文详细介绍一种新的体系结构级功耗评估工具,并对其评估性能做出分析。

2 功耗模型设计

如图1所示,CMOS集成电路功耗来源有三个部分,有动态翻转功耗Pdyn、短路电流功耗Pshort和静态功耗Pstat。CMOS电路的功耗计算公式可以表达为

关于动态功耗计算,CL取决于每个IC元件的电路设计和布局,本文使对于规整结构如存储阵列和连线使用分析模型,对于部分随机逻辑结构使用经验模型。翻转因子α根据性能模拟器的统计数据结合电路属性可以计算得到。VDD是供电电压,f是时钟频率。这样可以计算出动态翻转功耗。

短路功耗是在电路动态切换瞬间产生的。据文献[6~7],短路功耗大约占总动态翻转功耗的10%,但在某些情况下可达动态翻转功耗的25%左右。当电路翻转时,同时消耗翻转功耗和短路功耗。电路的内部属性决定短路功耗和动态翻转功耗的比例,是Vdd/Vth的强函数。本文使用来自文献[6]的以下三个公式计算一个门每次翻转的短路能量。

其中,Es(tT≪τ)是快输入时一个门每次翻转的短路能量,Es(tT≫τ)是慢输入时一个门每次翻转的短路能量,vT是规格化亚阈值电压(Vth/Vdd),α是饱和速率,Cin是门的输入电容,Vdd是供电电压,fo是后续门的晶体管驱动率,FO是扇出(Cin/Cout)。

静态功耗主要考虑两种泄漏电流,亚阈值漏电流和栅极漏电流。亚阈值电流、栅极漏电流的计算使用MASTAR[8]。

2.1 体系结构级功耗建模

本文将处理器划分为处理器核、片上存储器、总线和时钟几大模块,然后深入分析各模块的功能及电路级映射。

处理器核包括取指单元(IFU),地址产生单元(AGU),标量运算单元(SCU),程序控制单元(SEQ)。它们都可以进一步划分为硬件结构。IFU单元进行取指操作,将地址发送到存储器,然后将得到的指令放在指令缓存中,映射为RAM结构的阵列。AGU单元进行地址计算、寄存器传送、立即数赋值、标量加载存储等功能,映射为逻辑结构。SCU单元可能包括ALU、旁路逻辑和寄存器文件。在本文的层次化框架中,ALU在电路级被映射为复杂逻辑,旁路逻辑被映射为线和逻辑模型的组合逻辑,寄存器文件则被映射为阵列模型。SEQ单元实现程序控制相关的指令,包括跳转、调用和循环等指令,主要是产生使能、PC等信号,映射为逻辑。

片上存储器包括指令存储器和数据存储器。指令存储器是常规的存储器实现;数据存储器实现了支持行列多粒度并行读写的片上存储结构,本文将此段逻辑归类于总线部分,数据存储器也视为常规存储器。这样,片上存储器映射为阵列结构。

总线一般包含仲裁和选通逻辑,这需要通过较为复杂的组合逻辑产生,另外存储器区域较大,长连线不可避免。总线在电路级映射为逻辑和连线。

时钟的功耗占据相当大的比例,对时钟建立体系结构级功耗模型是非常重要的。时钟电路有两个主要部分:锁相环(PLL)[10~11]和分布式时钟网络。本文对PLL使用经验性的功耗模型[9],而将分布式时钟网络映射到电路级的时钟网络模型。

2.2 电路级功耗建模

导线性能的主要参数有电阻、电容和电感。对于简单的短导线,本文使用如图2的π-RC模型。其中Rwire和Cwire的计算见公式。

对于带中继的长导线[12],本文使用CACTI6.0[13]提供的功耗计算方式。

阵列主要有两大类:RAM(Random Access Memory)和CAM(Content Addressable Memory)。RAM用来随机地存储和恢复数据,例如寄存器文件堆、分支预测和指令窗口等;CAM则是相联处理的硬件实现,包括TLB、指令窗口恢复逻辑和加载/存储顺序检查等。阵列的动态功耗主要考虑译码器、字线、位线和敏感放大器的动态功耗,因为它们构成了阵列动态功耗的绝大部分,短路功耗简化计算为动态功耗的1/10。

逻辑部分主要可以归为两类:一类是简单的逻辑实现,如取指单元、译码单元、同步单元、加载存储单元、总线等模块;一类是比较复杂的运算单元,包对于简单的逻辑,使用较为精确的经验模型。对于运算单元,对其进行体系结构级功耗建模非常困难,本文使用RTL反馈建模的方法实现。

时钟分布网络将由锁相环(PLL)产生的时钟信号分布到各个部件的时钟输入端。本文参考Wattch的时钟建模方法并根据处理器进行优化,实现对处理器时钟分布网络的电路级功耗建模。单一的全局时钟网络功耗来源主要包括时钟金属线、时钟缓冲区和时钟负载。

2.3 工艺级功耗建模

工艺上,本文基于工业标准的国际半导体技术蓝图(ITRS),使用“CMOS工艺评估模型及其蓝图”(Model for Assessment of CMOS Technologies and Roadmaps,MASTAR)计算40nm工艺下的设备参数,如单位阻抗、电容和电流密度。

ITRS是由欧洲、日本、韩国、台湾、美国五个主要的芯片制造地区发起的。通过全球芯片制造商、设备供应商、研究团体和consortia的协作努力,路线图团队识别关键的挑战,鼓励创新解决方案,并欢迎来自半导体团体的分享。这些团队同时还参与了其他具有战略意义的路标的研究,例如电子学和纳米技术,所以ITRS能够很好地理解对于基本研究能力和产品潜力的需求谱图。ITRS提供的MASTAR具有很高的权威性,可用来计算指定工艺下的设备参数。

2.4 RTL反馈建模

RTL反馈建模,根据已有的RTL实现,对目标模块进行RTL功耗评估,得到其功耗,将之制作成表的形式,这样每次进行功耗评估时,根据查表即可得到期望功耗。下面介绍本文的RTL功耗评估流程。

如图3是本文采用的RTL功耗评估流程。需要的资源主要包括:工艺单元库、模块的RTL代码、测试激励(testbench)、RTL仿真工具VCS及后端综合工具Design Compiler。一方面输入测试激励给RTL模型,以生成backward saif文件,另一方面RTL代码结合工艺单元库进行后端流程,在read_saif阶段接收前面生成的backward saif文件,进而得到该模块的功耗值。

3 体系结构级功耗评估工具设计

本文基于体系结构级周期精确模拟器,提出一种体系结构级功耗分析框架,它是体系结构及功耗评估工具的核心。体系结构级功耗分析框架主要由体系结构级模拟器和体系结构级功耗评估工具组成。体系结构级模拟器为功耗评估工具提供详细的统计数据,功耗评估工具结合用户输入的微体系结构参数以及电路、工艺参数,即可评估出指定体系结构在特定应用和工艺下的功耗值。

用户需要设定静态配置,包括三个层次的参数,体系结构级、电路级和工艺级。体系结构级参数与性能模拟器的配置文件中的参数类似,包括核数目、硬件线程数目等。电路级参数指定实现细节。例如,你可以指定某阵列使用基于触发器单元实现而不是使用SRAM单元搭建。工艺级参数包括设备类型(高性能,低待机功耗,低运行时功耗)及互连。

功耗评估工具还有的输入就是动态输入,即周期级性能模拟器产生的统计信息,模拟器关于统计数据以文本形式输出,而功耗评估工具仅提供XML格式的输入接口。需要设计一种方法将统计数据转换为XML格式。本文首先建立一个XML的输入模版,然后编写批量处理的脚本,将模版中的相关数据用模拟器的统计数据替换,如此便自动化地实现了文本到XML格式的转换。

性能评估模拟器调度功耗评估工具以生成运行时功耗值。在计算运行时功耗之前,性能评估模拟器需要通过XML接口文件将各个独立器件的翻转系数传给功耗评估工具。一个组件的活动因子有此组件的访问数和某时间间隔内所以访问的平均海明距组成。通过改变时间间隔,可以改变运行时功耗计算的间隔尺寸。如果性能模拟器每个周期都调用功耗评估工具进行运行时功耗计算,就会生成一个周期精确的功耗文件,这对研究实时功耗峰值很有用。如果性能模拟器在功耗仿真完毕后进行运行时功耗计算,生成的则是平均功耗文件。

其中,n是一个指定仿真时间的周期数,Access-Count是仿真时间指定单元的访问次数,Hamming-Distance是两次连续访问的总翻转位总数。如果性能评估模拟器不能追踪海明距,功耗评估工具假定所有bit位每周期都翻转。性能评估模拟器大多数情况下能提供每个独立组件的翻转系数,然而只要性能评估模拟器能提供基本统计信息,功耗评估工具可以推算出组件的翻转率。例如,如果性能评估模拟器只能追踪访存指令数目,但没有加载存储队列翻转率的详细信息,功耗评估工具假定加载存储队列的每个存储器指令包含一次读,一次写,这种假定基于访存单元的普遍统计结果。

4 性能分析

本文从评估精度和评估速度两方面对处理器体系结构级功耗评估工具的性能给出分析。

4.1 准确度测试

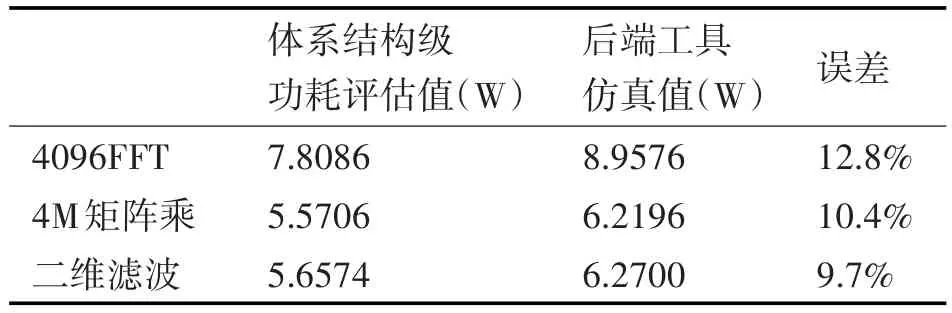

为了分析体系结构级功耗评估工具的准确度,本文在不同测试激励下将其评估结果与后端工具的结果进行对比。测试采用TSMC LP40nm工艺,时钟频率为1.2G。对于4096FFT、4M矩阵乘、二维滤波等算法,其评估数据如表1所示。

通过以上三个典型算法的测试评估,总的功耗误差控制在15%以内,说明了结构级功耗评估工具的准确度是足够高的。其一,层次化的功耗建模思想,层层深入由体系结构级到工艺级实现,实现了高准确度的功耗模型;其二,对比较复杂难以用分析模型建模的运算功能单元逻辑,采用了RTL反馈建模的方法,大大提高了体系结构级功耗评估的准确度;其三,体系结构级周期精确级模拟器完整准确的数据统计功能,为功耗评估的准确度提供了保证。

表1 三种算法下功耗评估表

4.2 速度评估

体系结构级功耗评估实现的必要性是其相比后端评估工具的高速度性,从而为处理器体系结构级探索提供便利。功耗评估的速度会根据应用程序的不同会有一定的改变,但对于体系结构设计者,评估工具速度量级的重要程度不亚于评估精度。针对上节的各算法,在RTL后端功耗评估,其速度约为70 insts/s(每秒指令数);而通过该处理器体系结构级功耗评估工具,速度可达350k insts/s。可见体系结构级功耗评估工具的速度是RTL后端工具的约5000倍,其速度优越性彰显无遗。

5 结语

本文采用层次化建模思想,从体系结构级、电路级和工艺级三个层次,结合工艺缩放比例原理和RTL反馈建模方法,进行处理器功耗建模;在功耗模型基础上,提出一种体系结构级功耗分析框架,进而实现体系结构级功耗评估工具;最后通过算法实验对其进行速度、精度分析,表明该体系结构级功耗评估工具有很高的评估效率。

[1]Bona,A.,ALaRI,Lugano.An Instruction-level Methodology for Power Estimation and Optimization of Embedded VLIW Cores[C]//Design,Automation and Test in Europe Conference and Exhibition,2002.

[2]S.Nikolaidis and Th.Laopoulos.Instruction-Level Power Consumption Estimation of Embedded Processors for Low-Power Applications[C]//Intelligent Data Acquisition and Advanced Computing Systems:Technology and Applications,International Workshop,2001:139-142.

[3]V.Tiwari,S.Malik,A.Wolfe,M.Tien-Chien Lee.Instruction Level Power Analysis and Optimization of Software[C]//VLSI Design,1996:326-328.

[4]D Brooks,V Tiwari,M Martonosi.Wattch:A Framework for Architectural-level Power Analysis and Optimizations[C]//Proc of the ISCA-27,2000:83-94.

[5]W.Ye,N.Vijaykrishnan,M.Kandemir,M.J.Irwin.The Design and Use of SimplePower:A Cycle-Accurate Energy Estimation Tool[C]//Design Automation Conference,2000:340-345.

[6]K.Nose and T.Sakurai.Analysis and Future Trend of Short-circuit Power[J].IEEE TCAD,19(9),2000:1023-1030.

[7]V.Zaccaria,D.Sciuto,and C.Silvano.Power Estimation and Optimization Methodologies for VLIW-Based Embedded Systems[M].Norwell,MA,Kluwer Academic Publishers,2003.

[8]Semiconductor Industries Association.Model for Assessment of CMOS Technologies and Roadmaps(MASTAR)[OL].2007,http://www.itrs.net/models.html.

[9]H.T.Ahn and D.Allsto.A Low-jitter 1.9-V CMOS PLL for UltraSPARC Microprocessor Applications[J].JSSC,2000,35(3):450-454.

[10]Razavi,B.,Monolithic.Phase-Locked Loops and Clock Recovery Circuits[M].IEEE Press,1995.

[11]Maneatis,J.Low-Jitter Process-Independent DLL and PLL Based on Self-Biased Techniques[J].IEEE Journal on Solid-State Circuits,1996,31(11):1723-1732.

[12]K.Banerjee and A.Mehrotra.A Power-optimal Repeater Insertion Methodology for Global Interconnects in Nanometer Designs[J].IEEE Transactions on Electron Devices,2002,49(11):2001-2007.

[13]N.Muralimanohar,R.Balasubramonian,and N.P.Jouppi.CACTI 6.0:A Tool to Model Large Caches[R]. School of Computing,University of Utah,Tech.Rep.,2007.

Design of An Architectural Level Power Estimation Tool for Processors

LIU ZhihongZHANG XingZHANG Hongfeng

(Wuhan Second Ship Design and Research Institute,Wuhan430064)

Power estimation at architectural level provides the designer with more flexibility to trade off power with speed and area in the early stage of design procedure,and also greatly reduces design cost.In the paper,power models are designed at architecture-level,circuit-level and technology-level,both the technology scaling theory and the RTL backwards modeling method are used.Based on the power models,the architectural level power estimation tool is designed.At last,an analysis of the estimation tool’s performance is given from the respect of accuracy and speed,the architectural level power estimation tool speeds up a lot while ensuring the estimation accuracy.

architectural level,power model,power estimation

TP302

10.3969/j.issn.1672-9730.2017.07.042

2017年1月7日,

2017年2月29日

刘志宏,男,高级工程师,研究方向:自动控制及舰船电子武备技术。张星,男,博士,高级工程师,研究方向:自动控制及计算机体系结构。张洪峰,男,硕士,工程师,研究方向:舰船电子武备技术。