基于FPGA和DSP的遥测数据实时谱分析卡设计

褚建平,甄国涌*,刘东海

(1.中北大学电子测试技术国家重点实验室,太原 030051,2.太原市华纳方盛科技有限公司,太原 030051)

基于FPGA和DSP的遥测数据实时谱分析卡设计

褚建平1,甄国涌1*,刘东海2

(1.中北大学电子测试技术国家重点实验室,太原 030051,2.太原市华纳方盛科技有限公司,太原 030051)

为了实时分析遥测数据单位频带内谱信息随频率的变化情况,设计了一种遥测数据实时谱分析卡。设计采用FPGA+DSP系统架构,配合流水线作业的设计理念。振动信号功率谱密度(PSD)计算采用快速傅里叶变换法(FFT),冲击信号冲击响应谱(SRS)采用递归数字滤波法,极大降低运算量,缩短谱分析的时间,从而实现谱信息分析的实时性。测试结果表明,该谱分析卡可以在9 ms内完成一路高频振动数据的处理,在67 ms内完成一路冲击数据的处理,设计具有良好的实时性、稳定性和扩展性,在实际应用中得到较好的效果。

FPGA+DSP;遥测数据;功率谱密度(PSD);冲击响应谱(SRS);FFT

对信号进行频谱分析,可以得到信号的频率结构,了解信号的频率成分。这对于工程上确定信号产生的原因,对系统参数进行识别及校正、动态监测设备的状态等都是非常有用的[1-2]。通过阅读已有的大量文献发现,对于遥测数据的谱分析都是在数据接收完成后,再进行谱分析的,不具有实时性,针对遥测数据实时谱分析的要求,设计了遥测数据实时谱分析卡,实现对3路高频振动数据的实时功率谱密度分析和2路冲击数据的实时冲击响应谱分析。分析完成后,将分析结果实时发送给上位机。

1 系统硬件设计

遥测数据实时谱分析卡系统总体设计框图如图1所示。谱分析卡主要由数据预处理及接口控制模块、数据实时处理模块和电源模块3部分组成。FPGA模块主要由FPGA芯片、晶振、PROM和程序下载接口组成,完成遥测采编数据的接收、挑选以及预处理工作。FPGA芯片采用Spartan6系芯片XC6SLX150_FGG484芯片,程序缓存PROM采用M25P64芯片。DSP模块由DSP芯片、复位电路、晶振、程序缓存Flash和程序下载接口组成,完成对高频振动数据和冲击数据的谱分析工作,DSP芯片选用TI公司推出的低功耗浮点型TMS320C6747芯片[3],程序缓存Flash选取NOR型Flash S29AL032D芯片。电源模块采用3片TPS54331电源芯片,包括5 V转3.3 V DC-DC、5 V转2.5 V DC-DC和5 V转1.2 V DC-DC为整个系统供电。

图1 系统总体设计框图

2 FPGA功能设计

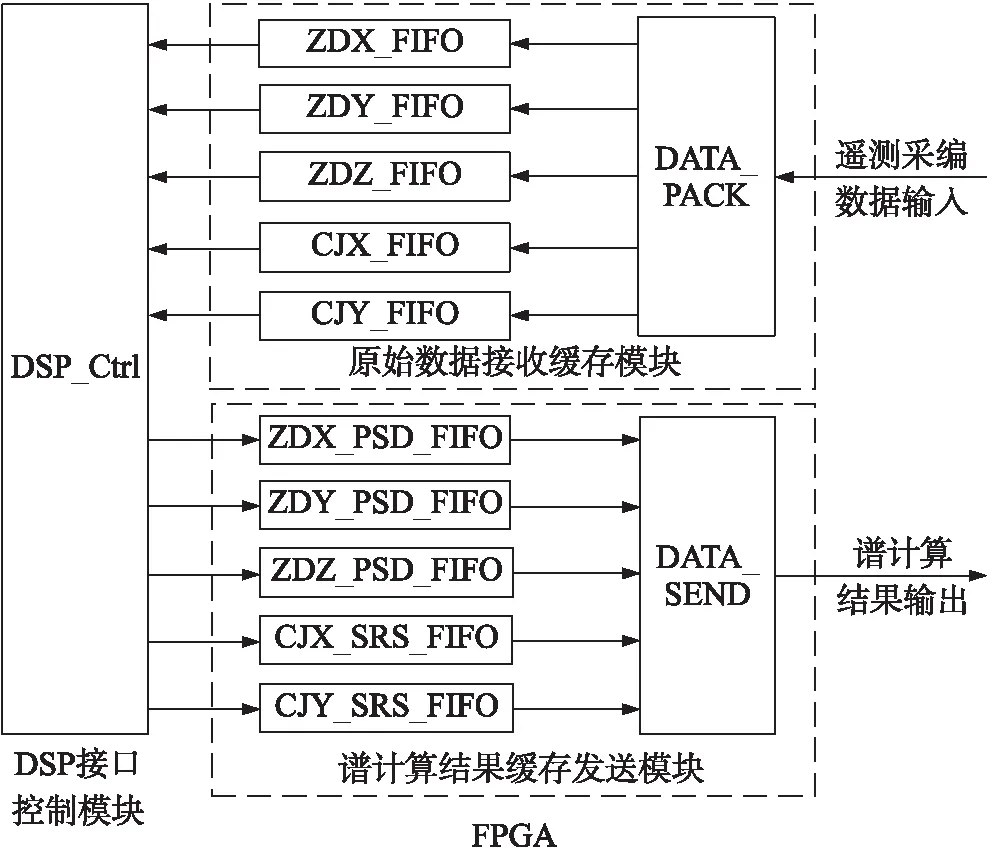

FPGA内部功能划分图如图2所示,由原始数据接收缓存模块、DSP接口控制模块和谱分析结果缓存发送模块组成。

图2 FPGA内部功能划分图

系统工作流程图如图3所示,原始数据接收缓存模块中的DATA_PICK模块,通过同步422接口接收遥测采编数据,在接收到的数据中不断地搜索同步字“EB90”以实现帧格式同步,从而保证对数据帧结构中信息的正确识别。正确识别帧格式后,将需要处理的3路高频振动数据和2路冲击数据挑选出来,分别缓存在相应的FIFO中,以便后续数据的处理。当FPGA原始数据接收缓存模块中的任意一个FIFO半满后,半满信号作为上升沿中断发送给DSP,DSP响应该中断,读出半满FIFO中的数据到DSP中,等待进行谱分析。DSP谱分析完成后,通过IO口向FPGA发送上升沿,作为谱分析完成的标志。FPGA通过识别完成标志来识别DSP发送过来数据的种类,并存储在谱分析结果缓存发送模块相应的FIFO中。谱分析结果缓存发送模块中DATA_SEND模块用来接收上位机发送过来的读数指令,将谱分析数据通过HDLC协议发送到上位机界面,上位机解析HDLC协议后,实时显示谱分析情况。

图3 系统工作流程图

3 DSP功能设计

DSP内部功能划分图如图4所示。DSP采用外部存储器接口EMIFA,控制原始数据的输入和谱分析完成数据的输出。原始振动数据采用快速傅里叶变换谱分析算法进行功率谱密度计算,原始冲击数据采用递归数字滤波法进行冲击响应谱计算。谱分析完成数据缓存采用乒乓缓存结构[4],如果正在写PING_FIFO,那么就将PONG_FIFO的分析结果发送出去;如果正在写PONG_FIFO,那么就将PING_FIFO中的分析结果发送出去,保证写数据和传输数据的流水线作业,实时将谱分析完成数据发送给FPGA。

图4 DSP内部功能划分图

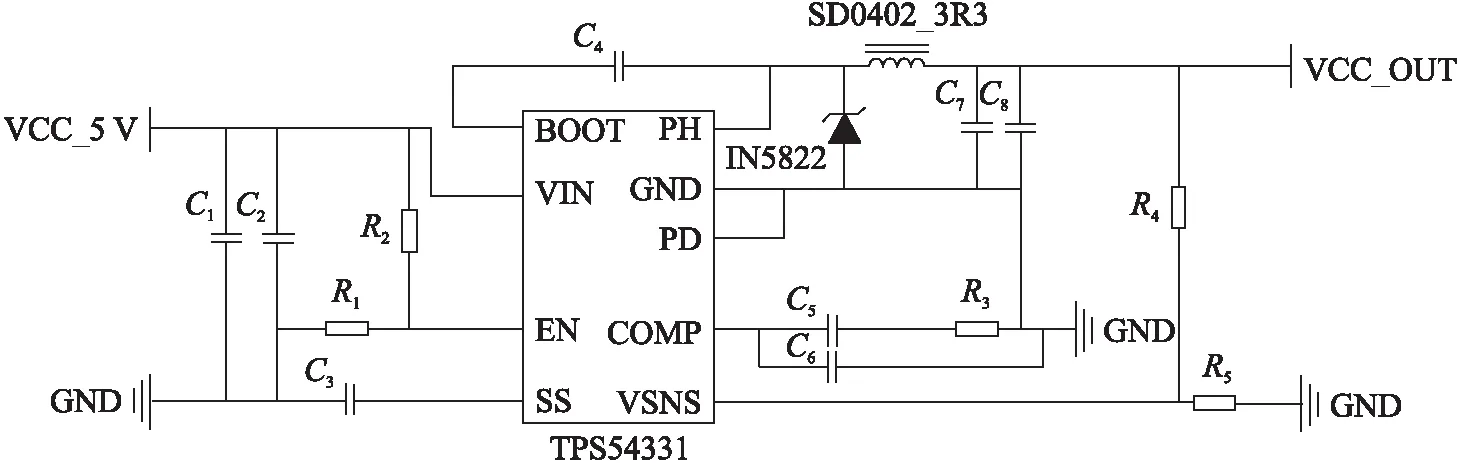

4 供电模块电路设计

供电模块电路图设计如图5所示。由于DSP芯片对上电顺序有一定的要求:在IO口供电电压达到1.65 V之前,核供电电压至少要攀升到900 mV。所以选用的供电芯片一方面要求输出电压可调,另一方面要求可以延缓电源启动时间。综合以上两个方面要求,选用TI公司的TPS54331电源芯片。

图5 供电模块电路设计图

该电源芯片可以使用表达式(1),通过配置电阻R4和电阻R5的阻值来控制VCC_OUT输出,其中Vref=0.8 V。将电阻R4和电阻R5分别设置成10.2 K、3.24 K,控制5 V转3.3 V DC-DC;将电阻R4和电阻R5分别设置成10 K、4.64 K,控制5 V转2.5 V DC-DC;将电阻R4和电阻R5分别设置成10 K、19.6 K,控制5 V转1.2 V DC-DC。

Vout=Vref×[R4/R5+1]

(1)

TPS54331电源芯片可以通过改变电容C3的容值,控制芯片上电延迟时间在1 ms到10 ms之间。利用公式(2)可以计算上电的延时时间,其中Vref=0.8 V,Iss=2 μA。为控制DPS不同电压的上电顺序,将5 V转3.3 V DC-DC、5 V转2.5 V DC-DC、5 V转1.2 V DC-DC的电容C3分别设置成27 nF、22 nF、15 nF,控制上电延迟时间分别为10 ms、8.8 ms、6 ms。

(2)

通过示波器可以捕捉到上电时3路电压输出的时间延迟情况,具体情况如图6所示。图中圆圈位置为核电压值上升到900 mV位置,方块位置为IO口电压上升到1.65 V位置,后者时间比前者晚0.5 ms左右,符合设计要求。图中竖直黑线分别代表各输出电压达到稳定值的位置,可以看出各路电压延迟启动情况符合设计要求。

图6 电源模块3路电压输出延迟图

5 系统稳定性设计

FPGA芯片和DSP芯片之间的数据衔接是决定系统稳定性的关键,为了实现FPGA芯片和DSP芯片的无缝衔接,需要了解各芯片的工作机制,FPGA芯片和DSP芯片具有不同的工作机制:FPGA芯片是并行工作状态机制,而DSP芯片是串行工作状态机制。即FPGA中3路振动数据和2路冲击数据的FIFO是同时被写入数据的,任意一路FIFO达到半满后,FIFO的编程满引脚都会输出高电平。但是DSP只能按照半满信号拉高的先后顺序,捕捉到各路FIFO编程满引脚由低电平变成高电平时的上升沿中断,进行数据的读取和处理。由于DSP读取和处理每路数据的时间是固定的,那么在这段时间内5路数据累积量的大小将决定系统是否可以稳定地运行下去。

假设单路数据的数据采样率为10.24 K,振动数据进行一次功率谱密度计算需要采集1 024个点,冲击数据进行一次冲击响应谱计算需要采集2 000个点,即振动数据完成一次数据的采集时间约为100 ms,冲击数据完成一次数据采集的时间约为195 ms。根据对功率谱密度算法和冲击响应谱算法的在线仿真,得知完成一次功率谱密度计算需要9 ms,完成一路冲击响应谱计算需要67 ms。DSP对两种数据的流水线处理情况如图7所示。从图7可以看出流水线的工作流程为FPGA完成第一次振动数据采集,DSP开始处理第一次采集到的振动数据,其间FPGA一直在采集冲击数据,FPGA完成第一次冲击数据的采集,DSP开始处理第一次冲击数据,处理两路冲击数据需要67 ms×2=134 ms,处理完冲击数据后,读取第二次采集到的振动数据并进行振动数据的处理。在处理第一次冲击数据的过程中,FPGA完成对振动数据的第二次采集和第三次采集,然而DSP只能实时对第二次采集到的数据进行处理,3路振动数据的FIFO中都积累了一次采集的振动数据。可以推断,每次采集和处理完成一次冲击数据,振动数据的FIFO就会产生一次数据量的积累。久而久之造成振动数据FIFO的溢出,不能实时地处理振动数据。

图7 5路数据采集和处理非实时流水线作业图

然而实际测量的结果与推测的结果是有所差异的,实际测量中发现在最开始有少量振动数据被读取和处理,后期却只有冲击数据被读取和处理,振动数据不再被读取和处理,振动数据FIFO处于一种“假死”的状态。经过分析,原因如图8所示,在上文提到过处理一次冲击数据,就会有一次振动数据的累积。假设振动数据FIFO的容量经过一次冲击数据的处理后,由1 000 byte增长到3 000 byte,编程满引脚由低电平变成高电平,DSP捕捉到编程满引脚的上升沿触发一次读振动FIFO的动作,读取和处理一次振动数据后,振动FIFO中还是会缓存2 000 byte的数据,大于编程满界限,编程满引脚电平一直处于高电平,DSP不能捕捉到编程满引脚的上升沿中断,因此不能读取振动FIFO中的数据,振动FIFO全部处于“假死”状态。通过进一步分析发现,产生上述问题最根本的原因是系统实时性的问题,为了实现系统实时性,拟定了3种解决方案。

图8 振动FIFO“假死”状态分析图

方案1 将DSP芯片TM320C6747DZKBA3更改为TM320C6747DZKBD4,芯片工作主频由300 MHz提高为456 MHz,振动数据的处理时间缩短为6.58 ms,冲击数据的处理时间缩短为44 ms,处理数据时间共需要6.58 ms×3+44 ms×2=107.74 ms,处理时间大于100 ms不能达到实时处理数据的目的,因此还需要优化振动数据和冲击数据的处理算法,将时间控制在100 ms以内,才可以实现系统的实时性;

方案2 将单路数据采样率由10.24 K减缓到5.12 K,减缓采样率后的流水线作业图如图9所示。从图9可以看出流水线的工作流程为:完成第1次振动数据采集,进行振动数据的处理,完成第1次冲击数据的采集,进行冲击数据的处理,完成第2次振动数据的采集,进行第2次振动数据的处理,完成第3次振动数据的采集,进行第3次振动数据的处理,完成第2次冲击数据的采集,进行第2次冲击数据的处理等等,数据的采集和处理工作会有序的进行下去,不会出现FIFO“假死”现象的出现。

图9 5路数据采集和处理实时流水线作业图

方案3 采用一种约束优先级的方法实现系统的实时性。由于振动数据是高频数据,冲击数据是低频数据,并且冲击数据只有在大于一定的阈值之后才会被采集一次,因此在数据采集过程中有效的冲击数据是非常少的,约定冲击数据的优先级高于振动数据的优先级,即冲击数据采集完成时,优先保证冲击数据的实时性,对冲击数据处理过程中采集到的振动数据不做处理。如上文所述,冲击数据处理的过程中,不管振动数据处理还是不处理,振动数据都会被采集回来,造成振动FIFO的“假死”现象。

由于编程满信号是大于1 536 byte才有效,DSP读取一次振动数据会读走1 024 byte,固振动FIFO中如果数据量积累到大于1 536 byte+1 024 byte=2 560 byte时,振动FIFO就会出现“假死”现象。判断振动FIFO的编程满引脚高电平持续时间超过100 ms,就可以断定振动FIFO出现了“假死”现象。“假死”现象出现后,需要对FIFO进行复位,重新激活FIFO开始工作,保证系统稳定的工作下去。

综上所述,根据单路采样率的大小,可以采用不同的解决方案。在单路采样率大于5.12 K时,可以采用方案1加方案3;单路数据小于5.12 K时,可以采用方案2;两种解决办法都可以实现实时地谱分析。本设计采用设计方案2,可以很好的满足设计要求,测试结果如下。

6 测试结果与分析

为了验证遥测数据谱分析卡设计的系统稳定性,使用示波器监测DSP的EMIFA接口写使能信号,写使能信号监测图如图10所示。由于振动数据和冲击数据的数据量不同,根据写使能信号维持的时间可以判断发送数据的类型,从图中可以看出数据读出的顺序为振动X轴谱分析数据、振动Y轴谱分析数据、振动Z轴谱分析数据、冲击X轴谱分析数据、冲击Y轴谱分析数据。相邻不同数据种类之间的空闲时间,即为谱分析的时间。图中振动X轴谱分析数据与振动Y轴谱分析数据之间的空闲为9 ms,即该谱分析卡可以在9 ms内完成一路功率谱密度的计算。图中冲击X轴谱分析数据与冲击Y轴谱分析数据之间的空闲为67 ms,即该谱分析卡可以在67 ms内完成一路冲击响应谱的计算。谱分析卡可以稳定地进行谱分析。

图10 EMIFA接口写使能信号监测图

图11 正弦振动信号图

为了验证谱分析卡功率谱密度和冲击谱响应谱密度计算的正确性,将振动和冲击原始数据和谱分析结果进行绘图对比分析。图11所示的是500 Hz的正弦振动信号,图12是其功率谱密度图。从功率谱密度图中可以看出在100 Hz的位置都会有一个的功率谱密度突出点,其他位置功率谱密度都接近零。图13和图14分别表示的2 kHz随机振动的原始信号图和功率谱密度图,功率谱密度直接反应了原始振动数据的每个单位频率波携带的功率。

图15为冲击测试中一次测试信号,在经过递归数字滤波法处理后,冲击响应谱如图16所示。

图13 随机振动信号图图

图12 正弦振动信号功率谱密度截图

图14 随机振动信号功率谱密度图

图15 冲击信号原始数据图

图16 冲击响应谱图

7 总结

综上所述,该谱分析卡可以实时地处理3路高频振动数据和2路冲击数据。经过与专门的谱分析仪器分析的信号进行对比,该功率谱密度与冲击响应谱与专用仪器分析结果一致,说明分析程序正常,谱分析方法正确。

[1] 杨宇,叶宇风,王洪. 基于DSP的实时信号频谱分析模块设计[J]. 电子测量技术,2006,29(2):124-126.

[2] 周权,盖淑萍,林楠森,等. 基于DSP与FPGA实时功率谱分析仪[J]. 仪表技术与传感器,2015(2):26-28.

[3] 王成. 基于TMS320C6747阵列的超声无损检测的实时处理平台[D]. 黑龙江:哈尔滨工程大学,2011.

[4] 康艳霞,曹剑中,田雁,等. 实时视频处理系统中乒乓缓存的设计[J]. 弹箭与制导学报,2007(4):218-221.

[5] 李桂花,赵五元,马进忠,等. 基于CPCI总线DMA方式的实时高速数据交换系统[J]. 强激光与粒子束,2014(11):115103.

[6] 高文,朱明,刘剑等. 基于DSP+FPGA框架的实时目标跟踪系统设计[J]. 液晶与显示,2014(4):611-616.

[7] 徐婷. 信号频率测量的DSP实现[J]. 电子质量,2011(11):6-7.

[8] 洪嘉. 高速测试系统中的功率谱估计的DSP算法实现[D]. 四川:电子科技大学,2006.

TheDesignofRealTimeSpectralAnalysisCardofRemoteMeasurementDataBasedonFPGAandDSP

CHUJianping1,ZHENGuoyong1*,LIUDonghai2

(1.National Key Laboratory for Electronic Measurement Technology,The North University of China,Taiyuan 030051,China;2.Taiyuanshi Huana Fangsheng Technology Co,Ltd.,Taiyuan 030051,China)

In order to analyze signal spectrum changes with the frequency information in units of frequency band in real-time remote measurement data,a real-time spectral analysis card of remote measurement data is designed. FPGA+DSP architecture with assembly line is adopted. The vibration signal power spectral density(PSD)is calculated using the fast Fourier transform(FFT),and the shock signal Shock Response Spectrum Signal(SRS)calculated using recursive digital filter method,that the calculations make it reduce the amount of computation greatly,and short the time of the spectral analysis greatly. Therefore,real-time spectral analysis information is achieved. Test results show that the spectral analysis card can complete the high frequency vibration signal analysis within 9 ms and the shock signal analysis within 67 ms,and the Design has a good real-time performance,stability and scalability to give good results in practical applications.

FPGA+DSP;remote measurement data;Power Spectral Density(PSD);shock response spectrum

10.3969/j.issn.1005-9490.2017.05.012

2016-08-28修改日期2016-10-31

TP274

A

1005-9490(2017)05-1108-07

褚建平(1992-),男,黑龙江省七台河市人,硕士生,主要从事测试系统集成技术与应用软件技术研究工作,724721005@qq.com;

甄国涌(1971-),男,山西阳泉人,教授,硕士生导师,主要从事测试系统集成技术与应用软件技术研究工作,zhen_gy0124@163.com。