基于模拟预失真的2.4 GHz CMOS功率放大器设计*

徐 乐, 陶 李, 刘 宏, 田 彤

(1.中国科学院 上海微系统与信息技术研究所,上海 200050; 2.中国科学院大学,北京 100049)

0 引 言

为了满足低成本、小尺寸的无线通信收发机的要求,互补金属氧化物半导体(complementary metal-oxide-semi-conductor,CMOS)功率放大器(power amplifier,PA)作为无线通信收发机中的关键模块已经广泛研究。然而在非恒包络调制信号的通信系统中,要求功率放大器有好的线性度和高效率,在实际的CMOS功率放大器设计时,线性度和效率往往是矛盾的[1,2]。目前提高CMOS PA线性度的技术有多栅晶体管、自适应偏置控制、电容补偿技术和预失真技术以及包络跟踪等[3~6]。同时对于功率放大器输入输出匹配网络,传统的匹配电路大多数采用片外变压器匹配或者采用片上电感电容(LC)无源谐振网络[7]。对于CMOS工艺而言,片外变压器匹配不利于单片集成CMOS PA,片上LC网络由于片上电感器的面积较大,衬底损耗大以及品质因子较低,因此采用片上电感匹配,不利于降低芯片面积和提升功放的效率和线性度等性能。

本文提出一种将驱动级作为预失真器的模拟预失真方法来提高功率放大器的线性度,同时利用片上变压器实现阻抗匹配功能,设计一种高线性度、高增益和高集成度CMOS功率放大器芯片。

1 两级功率放大器电路设计

1.1 功率放大器整体电路结构

本文所设计的功率放大器整体结构框图如图1所示,包括偏置电路,输入、输出匹配网络,级间匹配网络和功率单元PA1,PA2。功率放大模块采用两级全差分共源共栅结构用于达到高增益的要求。图1 所示的功率放大器工作在2.4 GHz,通过合理设置偏置电压,分配驱动级PA1和功率级PA2的增益和-1 dB输出压缩点功率(P0(1 dB))来达到整体结构的高线性度和高增益的性能。

图1 功率放大器整体框图

1.2 模拟预失真消除MOS管非线性

对于工作在大信号条件下的功率放大器,MOS管的跨导gm的非线性是功率放大器幅度非线性的主要来源[4]。在考虑到功率放大器的线性度主要由2次和3次谐波决定,因此,忽略高次谐波项和交调项后,跨导的泰勒级数展开式为

(1)

交流电流ids为

(2)

考虑输入信号为频率相近的两个等幅信号,则Vgs(t)=A(cosω1t+cosω2t)代入式(2)中,得到ids三阶部分展开式为

3cos(ω1t+2ω2t)+3cos(2ω1t-ω2t)+

3cos(2ω2t-ω1t)]

(3)

产生的三阶互调分量2ω1-ω2,2ω2-ω1的幅度为3gm3A3/4,这两个三阶互调分量与信号频率靠近,难以用滤波器滤除,其非线性产物会干扰到信号,造成交调失真。功率放大器的三阶非线性产物主要受三阶跨导系数gm3的影响。

采用65 nm CMOS工艺,N通道MOS(NMOS)管尺寸W/L=960 μm/0.06 μm,栅极电压扫描0~1.2 V,仿真得到如图2,表示了gm的非线性系数随不同的栅极偏置电压Vgs变化。由图2可以看出,gm3在接近MOS管的阈值电压附近时通过零点,一般为了抑制gm3对线性度的影响,可以将偏置电压设置在gm3的零点,从而提高功率放大器的线性度[8]。

图2 跨导非线性系数随栅极电压变化曲线

文献[9,10]提出了模拟预失真技术来提高功放的线性度并优化线性,但设计时一般需要增加调节电路来使预失真器和功率放大器匹配,结构比较复杂。

本文通过对模拟预失真的文献调研总结,基于模拟预失真的原理,提出了一种将驱动级作为预失真器的模拟预失真方案来优化功放的线性度,不需要额外增加调节电路,节省面积,降低设计难度。本文的模拟预失真电路工作原理如图3,通过将驱动级既作为驱动电路,也作为预失真器,通过产生和功率级幅度一致,相位相反的谐波,用来补偿功率级的非线性,以提高PA的线性度。

图3 基于驱动级的模拟预失真原理

在双音测试的输出频谱,图3中两边的频谱分量分别代表驱动级和功率级产生的三阶交调分量,相位相差180°,幅度相同。具体电路偏置情况如图2所示通过将驱动级和功率级设置在不同的栅极偏置下,驱动级三阶跨导系数gm3-drive系数小于0,功率级三阶跨导系数gm3-power大于0。由式(4)可得,对于驱动级和功率级产生的三阶互调分量IM3drive和IM3power为

IM3drive(t)=K1(cos(2ω2-ω1)t+φ1)

(4)

(5)

IM3power(t)=K2(cos(2ω2-ω1)t+φ2)

(6)

(7)

式中A1,A2为驱动级和功率级输入信号幅度,φ1,φ2为IM3drive和IM3power相位,K1,K2为IM3drive和IM3power幅度。驱动级产生的互调信号通过功率级时被放大α,IMD3drive为

(8)

1.3 功率放大器的主体电路结构

功率放大器整体电路结构如图4所示,驱动级采用全差分的共源共栅结构来实现高增益,提高输入输出的隔离度,为下一级提供大的电压输出摆幅,驱动级NMOS管采用薄栅氧化层的晶体管提供大的跨导和小的寄生电容;功率级采用全差分共源共栅结构,功率级共栅管M7-M8采用厚栅氧化层的 NMOS 管,来提供更高的电压摆幅,更大的输出功率和稳定性。NMOS管采用深N阱工艺,不仅可以增加不同晶体管之间的隔离度,还可以用来提高 PA 的线性度。对于共栅管的偏置电路,采用自适应偏置结构,栅极电压随漏极电压变化,保证栅漏电压在一个合适的范围内,同时和自偏置结构相比又可以灵活地设计共栅管的直流偏置电压,以满足所需要的增益要求。为了增加系统的稳定性,阻容器(resistor-capacitor,RC)串联网络从功率级共栅管的漏极负反馈到共源管的栅极,同时在实际设计时需要优化RC的取值,使得功率放大器得到合适的输入和输出阻抗值;输入、输出端匹配电路采用片上变压器T1和T2实现阻抗匹配,实现单端信号和差分信号的转换,有效实现功率的分配和合成,减少了片上电感的使用,从而减小芯片的面积,降低了版图设计难度;CT为调谐电容器,使得变压器在工作点谐振,提高变压器的性能;级间匹配电路完成驱动级和功率级之间的阻抗匹配。

图4 功率放大器的整体电路结构

1.4 片上变压器设计

对于功放的输入输出匹配网络,本文采用片上变压器耦合进行设计,采用变压器进行阻抗变换,相比于LC网络进行阻抗变换,一方面变压器作为一种无源器件,不仅可以实现阻抗匹配,且有隔直流、通交流、单端和差分信号之间转换的作用,对于全差分结构,采用变压器进行匹配,可以有效进行功率的合成和分配;另一方面对于CMOS工艺,片上电感的面积较大且品质因子Q较低,片上电感不仅会增加了芯片的成本,还会降低功放的效率。在图4中,对于输入输出端匹配电路采用片上变压器T1,T2实现,同时通过在变压器的两端并联调谐电容CT,使功放在所需要的频率上进行谐振,同时也提高片上变压器的性能。

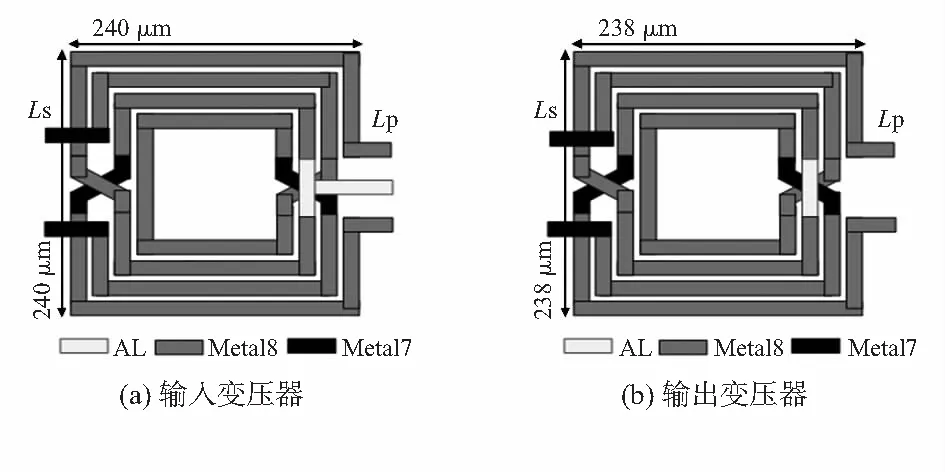

片上变压器设计采用65 nm CMOS工艺实现,采用电磁仿真软件对变压器进行电磁仿真,将仿真结果生成相应的电磁模型,与功率单元PA1和PA2进行联合设计仿真。设计的输入输出片上变压器版图结构如图5中所示,输入输出变压器参数主次线圈的等效电感Lp,Ls以及线圈比n分别依次为1.54 nH,1.32 nH,2∶2,以及1.47 nH,1.25 nH,2∶2。主次线圈的等效电感计算为

Lp=imag(Z11)/(2πf)

(9)

Ls=imag(Z22)/(2πf)

(10)

图5 输入输出片上变压器的版图

2 整体版图及仿真结果

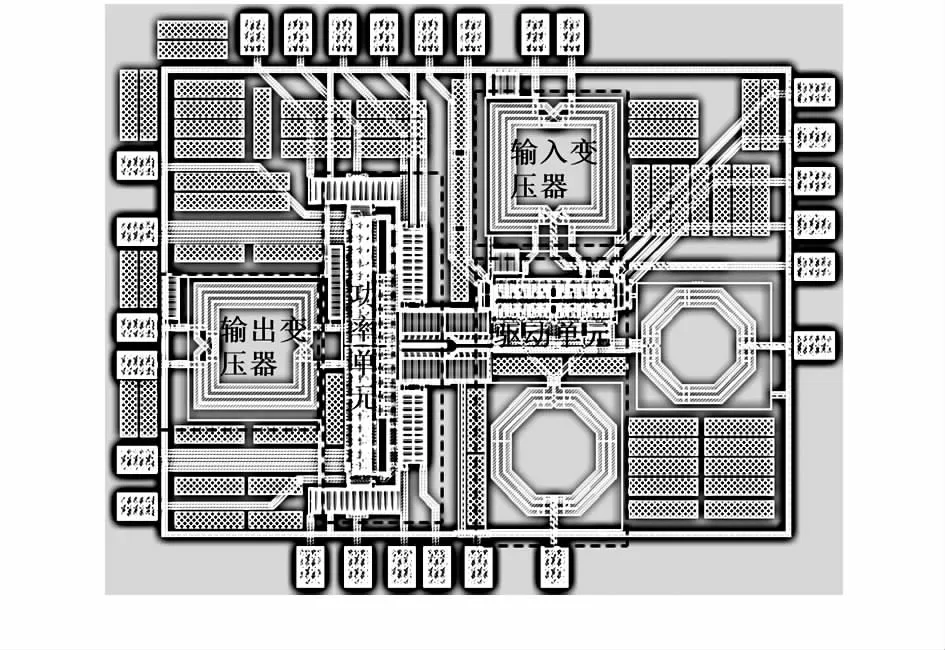

基于65 nm CMOS工艺进行功放的版图设计,如图6所示,芯片面积为1.08 mm×1.37 mm。考虑整体电路是差分结构,因此,在版图布局时需要充分考虑对称性和匹配。

图6 整体功率放大器版图

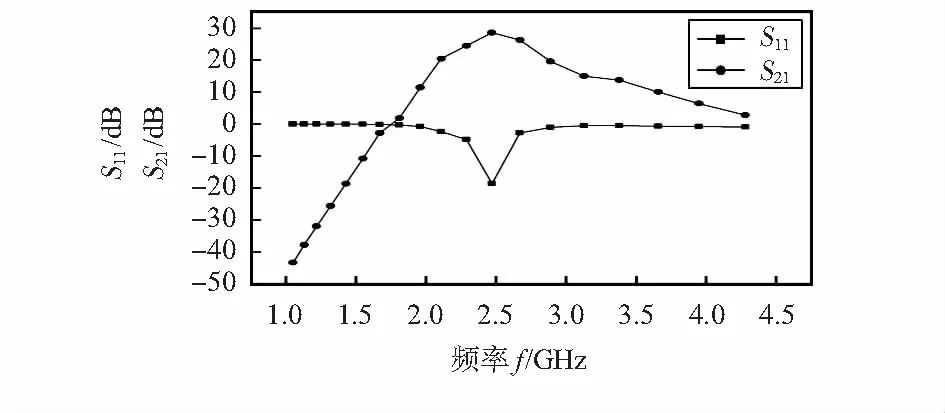

提取整个电路的版图寄生参数,利用Spectre RF对整个功率放大器结构进行后仿真验证。功率放大器的小信号S参数如图7所示,在2.4 GHz频段处,S21=27.2 dB,S11=-13.2 dB,S参数满足系统设计要求。

图7 功放小信号S参数随频率的变化曲线

功率放大器的功率增益G,输出功率POUT,附加效率PAE随输入功率PIN的变化曲线仿真结果如图8所示,功率放大器的-1 dB输出功率P0(1 dB)为22.9 dBm,功率附加效率PAE为23.5 %。

图8 输出功率、功率增益和附加效率曲线

采用偏置电压在gm3零点附近的三阶交调失真IMD3曲线和本文采用的预失真方案的IMD3曲线随输入功率变化曲线如图9中所示,在输入功率PIN为-10~-8 dBm,本文提出的预失真方案的IMD3减小了5~10 dBc,优化了功放的线性度,具有高线性度、高集成度和高增益的特性,满足设计要求。

图9 文中预失真与gm3=0的三阶交调失真曲线

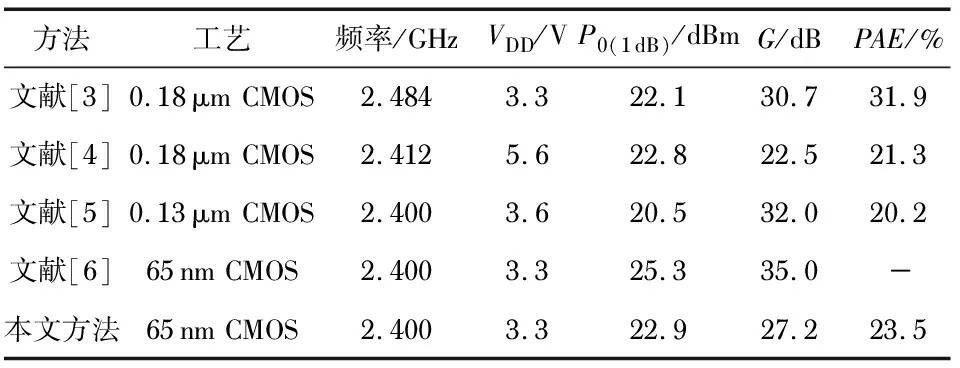

本文所设计的2.4 GHz高线性度,高增益和高集成度的两级全差分级功率放大器的仿真结果与近年来一些主流2.4 GHz功率放大器性能比较如表1所示。

表1 功率放大器设计性能比较

3 结 论

本文基于65 nm CMOS工艺设计了一种2.4 GHz的功率放大器。采用将驱动级作为预失真器的模拟预失真技术来提高功率放大器的线性度,采用片上变压器实现阻抗匹配,有效地进行功率合成与分配,减小了整体芯片的面积,降低了版图设计难度,实现了高增益、高线性度和高集成度的CMOS功率放大器设计。在2.4 GHz的工作频点上,该功率放大器可以达到-1 dB输出功率为22.9 dBm,功率附加效率为23.5 %,小信号增益为27.2 dB,三阶交调失真IMD3为-35.6 dBc,相比于偏置电压设置在gm3通过零点处,在一定的输出功率范围内,三阶交调失真IMD3减小了5~10 dBc。