基于QuartusⅡ的加法器的教学探讨

陈光红

【摘要】以加法器为项目载体,探讨了传统的教学方法和将《数字电子技术》与《EDA技术》课程整合后的教学思路,整合后借助于EDA软件QUARTUSⅡ,对半加器、全加器、四位加法器进行编辑、编译、仿真、编程、电路测试等,使学生对加法器的原理、应用等理解更完整、具体、深刻。

【关键词】加法器 数字电子技术 QUARTUSⅡ

【基金项目】苏州市职业大学《数字电子与FPGA的应用》课程体系及课程模式改革与实践2-3。

【中图分类号】G64 【文献标识码】A 【文章编号】2095-3089(2019)17-0245-01

引言

加法器是产生数的和的装置。常用作计算机算术逻辑部件,执行逻辑操作、移位与指令调用。[1]加法器可以用来表示各种数值,如:BCD码、余3码,加法器主要以二进制作运算。

文主要比较了传统的加法器的教学过程和将数字电子技术与EDA技术整合成一门课程后对加法器的教学思路,可以看出整合后的教学效果更好。

1.传统加法器的教学

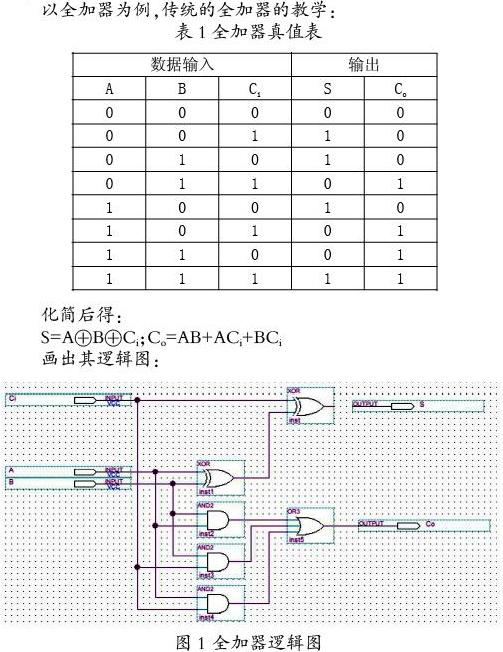

传统的电子专业的课程是数字电子技术和EDA技术作为两门独立的课程,分别在两学期里完成教学。在数字电子技术中讲解加法器时按照是否考虑低位来的进位分为半加器和全加器,常按如下步骤进行分析或设计:

列真值表、化简(代数法或卡诺图法)、找出最简逻辑表达式,画逻辑图。

由于实验条件有限,没有实际电路进行实验验证,学生印象不深,对加法器的理解停留在理论上。等到了下学期上EDA課程时,讲到加法器时还得重复一遍加法器的原理知识。而将《数字电子技术》和《EDA技术》两门课程融合后,可接着已分析出的逻辑图,在QUARTUSⅡ软件里借助原理图进行编辑、编译、仿真、编程,结合实际电路测试效果,结果一目了然,使学生印象深刻,真正掌握半加器与全加器的区别,及如何从一位全加器拓展到n位加法器。

2.基于QuartusⅡ的加法器的教学

仍以全加器为例说明基于QUARTUSⅡ的全加器的教学。

全加器的原理图如图1,在QuartusⅡ中利用原理图法进行编辑,编译后,对输入端A、B、Ci分别加上激励,进行功能仿真后输出端Co、S的波形如图2。

由波形图可看出,符合全加器的真值表表1。

将半加器和全加器分别进行编程、电路测试正确后,可将其生成符号元件,这些符号元件可作为独立的器件供其他设计项目调用。

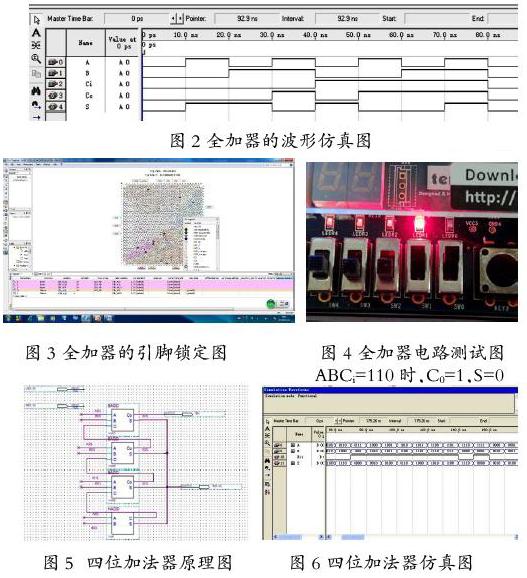

3.扩展到4位加法器的教学

利用半加器和全加器的符号元件可扩展到n位的加法器,下面以四位加法器为例,其原理图如图5所示,仿真结果如图6所示。

从仿真结果中可清楚地看出两个四位二进制数的加法计算的结果,进位也能直观地体现。

4.结论

将数字电子技术与EDA技术整合成一门课程,在我们应用电子技术专业实践了三年,结合《数字电子技术与FPGA应用》的在线课程及微课视频等,学生的学习积极性较高,且对加法器的掌握更好。

参考文献:

[1]杨志忠.数字电子技术[M].北京:高等教育出版社.

[2]于润伟.EDA技术与应用[M].北京:机械工业出版社.