一种卫星导航抗干扰处理器低功耗设计方法

潘未庄,王璐,夏效禹

(广州海格通信集团股份有限公司,广东 广州 510663)

0 引 言

全球卫星导航系统(GNSS)在军民用等领域已经得到广泛的发展,但GNSS信号功率非常小,极易被干扰,而且现在的电磁环境比以前恶劣很多,民用GNSS设备面临带内无意和恶意干扰的威胁,没有防护的军用GNSS设备在电磁对抗战场环境中根本无法使用. 带外干扰可以简单地用前端模拟滤波器滤除,但带内的强干扰必须采用阵列信号处理架构才能抑制,最近十多年来,源于雷达相控阵技术结合天线阵列信号自适应算法被广泛地应用在卫星导航抗干扰天线中,带有抗干扰天线的GNSS设备能在各种压制式干扰下正常工作,采用射频前端高性能大动态器件和多通道并行处理技术,自适应算法结合波束指向进一步增强了抗干扰性能,但也增加了设备功耗.

目前国内外对导航抗干扰处理器的低功耗研究主要分为两类,一类是随着芯片工艺进步,借鉴GNSS接收机软硬件优化降低功耗[1],另外一类是直接研制专用芯片大幅度降低功耗[2],但专用芯片设计难度高,周期长,成本高. 导航抗干扰处理器的一个主流设计是采用FPGA芯片,因此有研究从优化FPGA软硬件方面进行低功耗设计[3],综合采用多种改进可以降低一部分静态功耗和动态功耗[4]. 本文分析了GNSS智能天线的抗干扰处理器功耗来源,在不改动、不增加硬件的条件下,通过改进软件架构进一步降低功耗,最后利用实验验证了该方法的有效性.

1 主流抗干扰天线架构

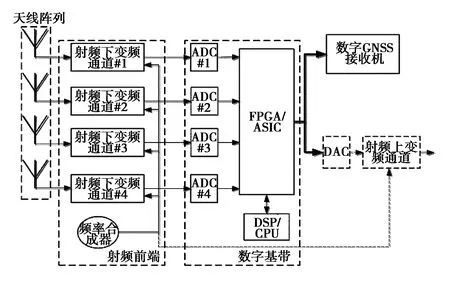

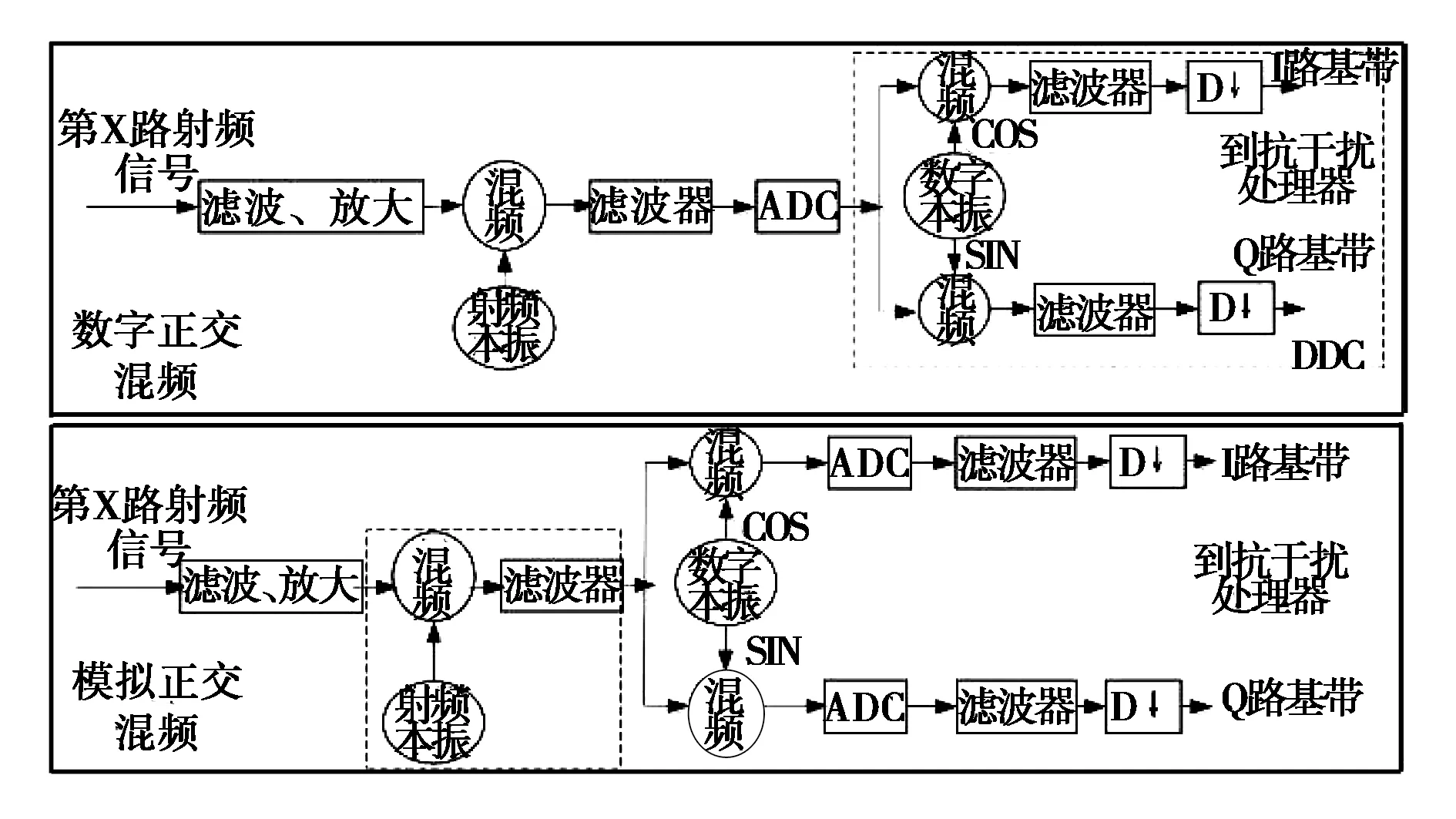

目前主流的抗干扰天线架构是通过阵列天线,同时输出多路信号,然后通过射频前端变频到中频,以便数字基带处理能够处理. 模数转换器(ADC)完成模拟中频到数字中频的转换,数字基带处理一般有数字信号处理器(DSP)或者中央处理器(CPU)配合现场可编程门阵列(FPGA)或者专用集成电路(ASIC)完成抗干扰处理,形成一路信号直接输出到新式的GNSS数字接收机,或者经过上变频到模拟射频后,连接到传统GNSS接收机的射频输入接口,替换掉普通天线让传统接收机也具备抗干扰功能[5]. 主流抗干扰天线的架构如图1所示.

图1 主流四阵元抗干扰天线组成示意图

2 抗干扰天线的功耗来源分析

2.1 模拟信号处理链路

如图1所示,如果仅考察单路模拟信号链路组成,抗干扰天线与普通天线相差不大. 但从数量上看,抗干扰天线比普通天线增加了N-1路射频下变频通道和ADC通道,N为天线阵元数,一般是4~16甚至更多. 如果需要将抗干扰处理后的信号再变频回射频,则还需要1路数模转换器(DAC)和1路射频上变频通道;通道数量的急剧增多导致元器件的数量呈几何级数增加,硬件设计也比单通道接收机要复杂很多,因此总体功耗会明显增加.

2.2 抗干扰处理器功耗

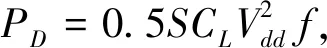

抗干扰处理器通常由ADC、DAC、DSP/CPU、FPGA或者专用的抗干扰ASIC等组成,完成模数转换、通道误差校正、均衡、干扰检测和估计、干扰抑制、波束指向、数模转换等功能. 为有效抑制干扰,抗干扰处理器均采用12~16 bit的并行高速ADC,采样时钟达到几十甚至是上百MHz. 虽然大部分抗干扰处理器架构对中频信号采用带通采样,进一步降低采样时钟,但由于导航信号带宽较宽,根据带通采样定理采样率Fs至少是信号带宽B的2倍才能不失真地还原信号,而在工程实践中,考虑到抗混叠滤波器的矩形系数和过渡带等因素,一般设计为2.56倍,如果用过采样率技术,再抽取则会进一步推升ADC采样时钟,而抗干扰处理时钟通常大于基带数据时钟. 抗干扰处理器无论采用FPGA还是ASIC,其均属于超大规模集成电路(VLSI),VLSI的动态功耗PD占总功耗的80%左右,动态功耗的估计公式[6]为

(1)

式中:S是电路开关频度;CL是输出负载电容;Vdd是供电电压;f是电路工作频率.S和CL由天线阵元数N和算法复杂度决定,本质上取决于芯片具体使用资源规模,可视为常量,Vdd由器件选型和工艺决定,一旦确定了抗干扰处理采用FPGA型号,则可视为常量.

根据公式(1),可以通过开发先进算法减少S、CL,优化改进架构降低f、采用专用ASIC结合动态电压调整(DVS)等技术来降低功耗.

3 抗干扰天线低功耗设计研究

3.1 采用DVS技术降低功耗

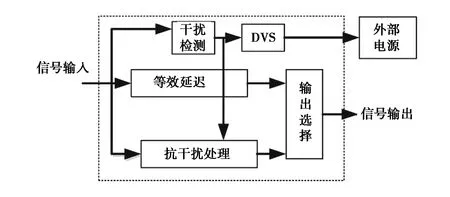

通过借鉴操作系统(OS)根据CPU的负载大小自适应调整CPU电压高低的DVS技术原理,根据干扰检测的结果来调整抗干扰处理器的供电电压或者切换工作状态,是降低平均功耗可行的方式. 卫星导航系统采用扩频技术,因此GNSS接收机本身具备一定的抗干扰能力,大概在40 dB左右,因此通过干扰检测技术实时监控接收机周围的电磁干扰状况,在干扰强度未达到但快接近接收机干扰极限时,切换抗干扰天线进入抗干扰模式;在判断无干扰时,判决策略要比有干扰的门限要严格,即采用迟滞门限切换工作模式. 为保证载波相位同步,需要设计和抗干扰处理时延相同的延迟模块,同时干扰检测模块本身的功耗不能超过抗干扰模块,否则得不偿失. 在切换正常接收和抗干扰处理模式等细节方面需要仔细设计.

60年峥嵘岁月,中国氮肥工业在砥砺前行中书写下了粮安天下的雄壮诗篇,以不忘初心的情怀高高筑起了中国复兴的宏伟梦想。氮肥工业以自身发展助推农业发展,以自身强大守护粮食安全,在种植面积有限的情况下,保证了粮食总产的稳定增长,满足了不断增长的人口和日益提高的人民生活需求。

而DVS技术需要硬件支持才能实施,目前主流的FPGA器件无法完全支持DVS技术的,而抗干扰ASIC则需要特殊设计才能实现. 采用干扰检测切换模式以及DVS技术来降低功耗的示意图如图2所示.

图2 采用DVS技术降低抗干扰模块功耗示意图

一般而言,性能优良的抗干扰算法占用芯片资源多,功耗大些.芯片的工艺越老,功耗也越大.而干扰检测配合模式切换的策略,以及DVS技术会进一步增加芯片的复杂度和资源,对抗干扰性能影响和降低功耗方面需要做进一步的研究,因此降低频率和减少芯片资源比开发低功耗高性能的算法和复杂的控制更能明显降低功耗.

3.2 采用带通采样和正交混频技术降低功耗

由于模拟同相/正交(I/Q)通道难以做到完全一致,几乎所有传统抗干扰天线都采用中频实信号采样,将射频信号变频到低中频[7],在保证无失真采样前提下,选择最低的采样率可以降低ADC的功耗,经过ADC后,在基带里面再进行正交变频,将中频信号变频到基带,用复数形式构造解析信号,有效带宽减少一半,抗干扰处理器的运行时钟将降低一半,从而降低了功耗.

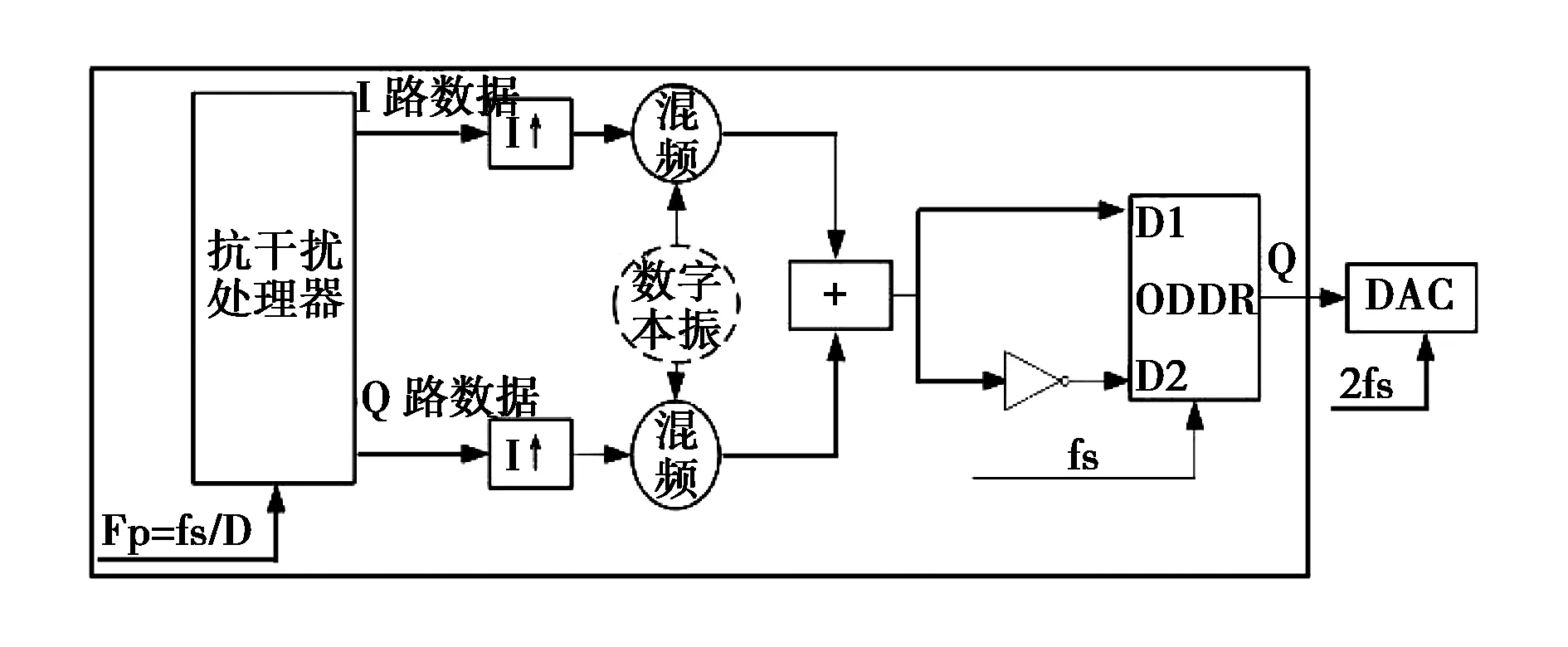

随着芯片技术的进步,模拟I/Q通道的幅相不平衡已降低到可接受的范围,可以在模拟域实现正交混频,甚至直接变到基带,即零中频的形式,采样率将进一步降低,抗干扰处理器也可以省掉混频和滤波器资源,但ADC数量将翻倍,印刷电路板(PCB)面积也增加,功耗未必能显著降低,而且零中频架构本身会带来额外的问题,工程实践中需要仔细权衡. 以1路通道信号链路为例,采用上述两种技术的框图如图3所示.

图3 带通采样和正交混频示意图

图3中,D↓是D倍抽取. 模拟正交混频中的虚线框中的实数下变频部分,就简化为零中频架构.

3.3 采用DAC欠采样技术降低功耗

如图1所示,对于天线和接收机隔离设计的应用是在数字基带完成抗干扰处理,主流的架构是设计数字上变频和模拟上变频,将信号变频到射频. 基带信号先内插后,与数字中频本振混频,然后通过DAC转换成模拟中频信号. 为满足纳奎斯特采样定理,DAC的时钟频率至少是中频本振的2倍.

为降低功耗,主流方式有如下三种:

第二种:采用具有混频[8]或者上变频[9]功能DAC芯片. 此类DAC一般在输出级设计有四象限乘法器或四开关架构,具有混频、归零(RZ)、双相保持(TPH)等模式,从而增强高次纳奎斯特区间频谱,通过后端滤波器即可实现以较低时钟频率实现高中频信号重建.

第三种:外部电路辅助. 主要有采用两个低速DAC芯片进行乒乓轮流输出数据,与高速混频器配合可实现采样率翻倍[10];或者采用放大器、延迟电路与高速电子开关实现,相当于采用分立器件实现第二种方式中DAC的TPH模式[11].

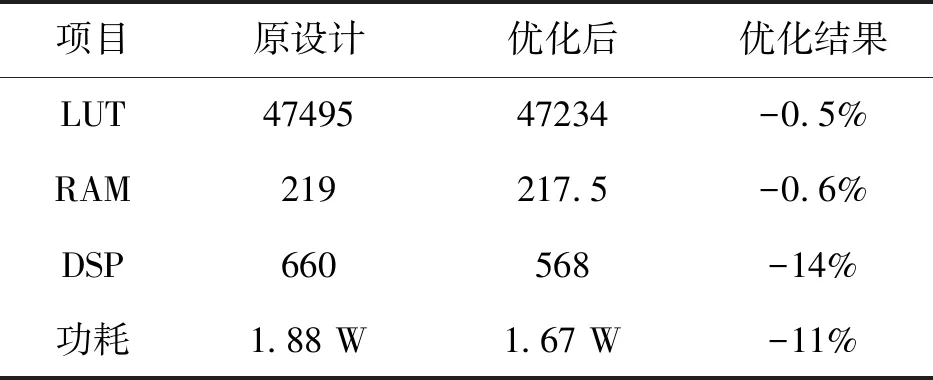

上述三种方式主要从改进硬件方面进行,缺点在于局限于特殊架构的DAC芯片,原有设计需要改动硬件,仅适合于新设计,通用性受限. 本文提出的思路是在不改动硬件基础上进行软件优化,简化数字上变频,降低抗干扰处理器的频率从而降低功耗. 本方案功能组成框图如图4所示.

图4 低功耗架构优化示意图

相比传统的架构,本方案进行如下几点改进:1) 多路信号在进行抗干扰处理进行D倍抽取,利用正交混频到基带信号带宽减半特性,将抗干扰处理器频率从fs降低到fs/D; 2)如图4中虚线框所示,抗干扰处理后的数字上变频运行时钟从2fs降低到fs,同时复用了数字下变频的数字本振,省去了2倍时钟和上变频本振,简化了混频模块的设计;抗干扰处理后的信号首先进行I倍内插,然后进行混频,混频输出I路数据和Q路数据合成实信号后分成两路,一路进入FPGA的ODDR元件D1输入端,另外一路是取反的数据进入ODDR的D2输入端,然后合成1路2倍速率的信号从Q端口输出到DAC,从而实现了以低速时钟产生高中频信号. FPGA资源占用传统方案降低. 本方案不增加额外硬件电路,不改变原有的硬件电路,原来的DAC时钟运行在2fs上.

由于DAC原理架构具备的零阶抽样保持 (ZOH)特性,DAC输出的频谱包络会形成辛格(SINC)函数的滚降特性,为保持通带平坦度,可以在原有的数字滤波器或者DAC后端的成形滤波器进行逆SINC补偿.

本优化功耗方案在FPGA架构的抗干扰处理器上进行仿真和测试,主要考察对比采用优化方案后芯片功耗、资源的变化对抗干扰性能和功能的影响. 资源占用评估主要考察查找表(LUT)、随机存储器(RAM)和数字信号处理器(DSP)这三种.

抗干扰处理器原设计输入的信号中频频率为46.5 MHz,带宽为20 MHz,ADC采样率62 MHz,数字下变频本振为15.5 MHz,数字上变频本振为46.5 MHz,内插因子为2. 仿真和测试如表1所示.

表1 仿真和测试记录表

从表1中可以看到,FPGA资源的占用均有不同程度降低,其中最大是DSP资源,减少了14%,而功耗降低也超过11%.

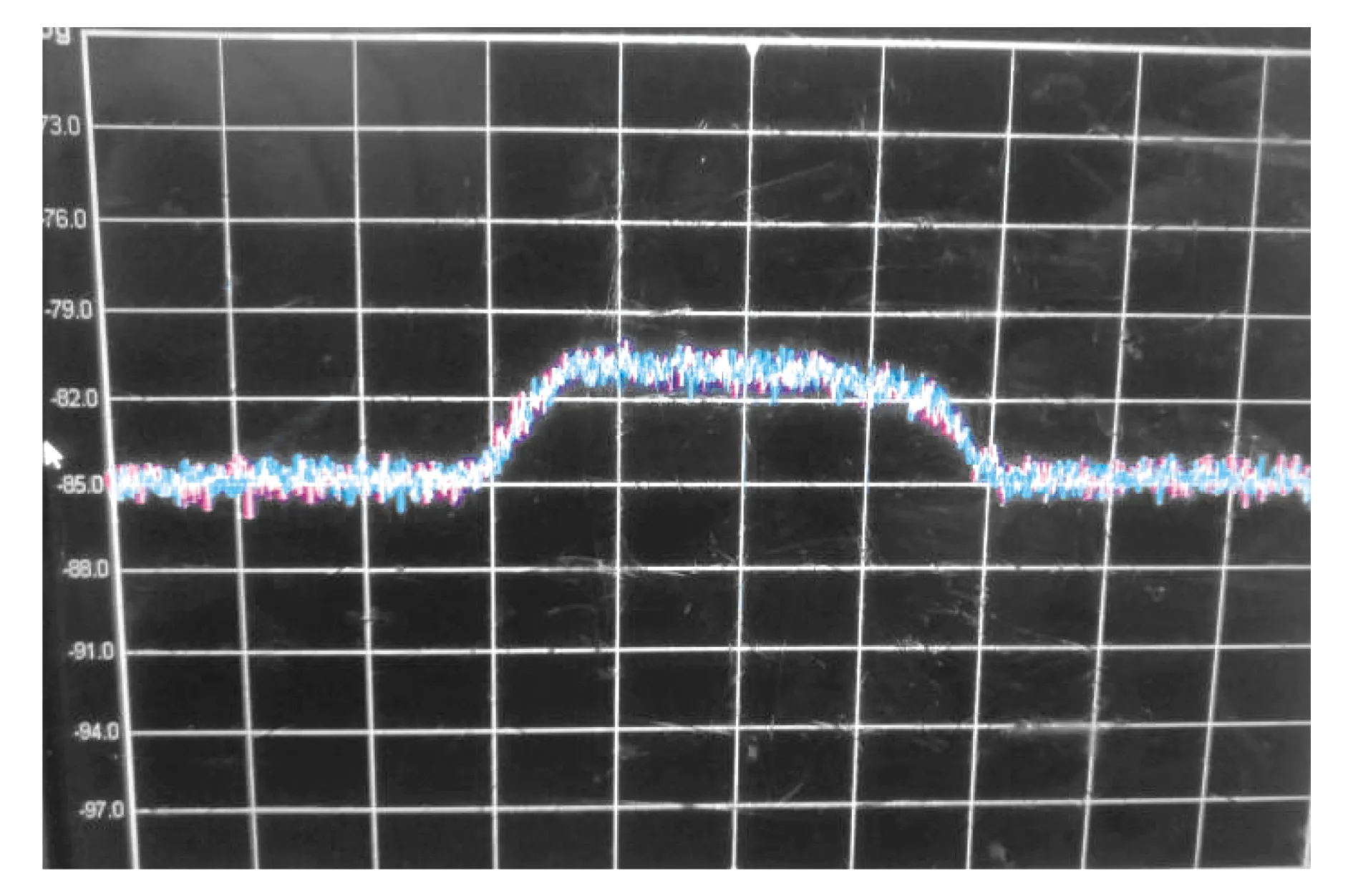

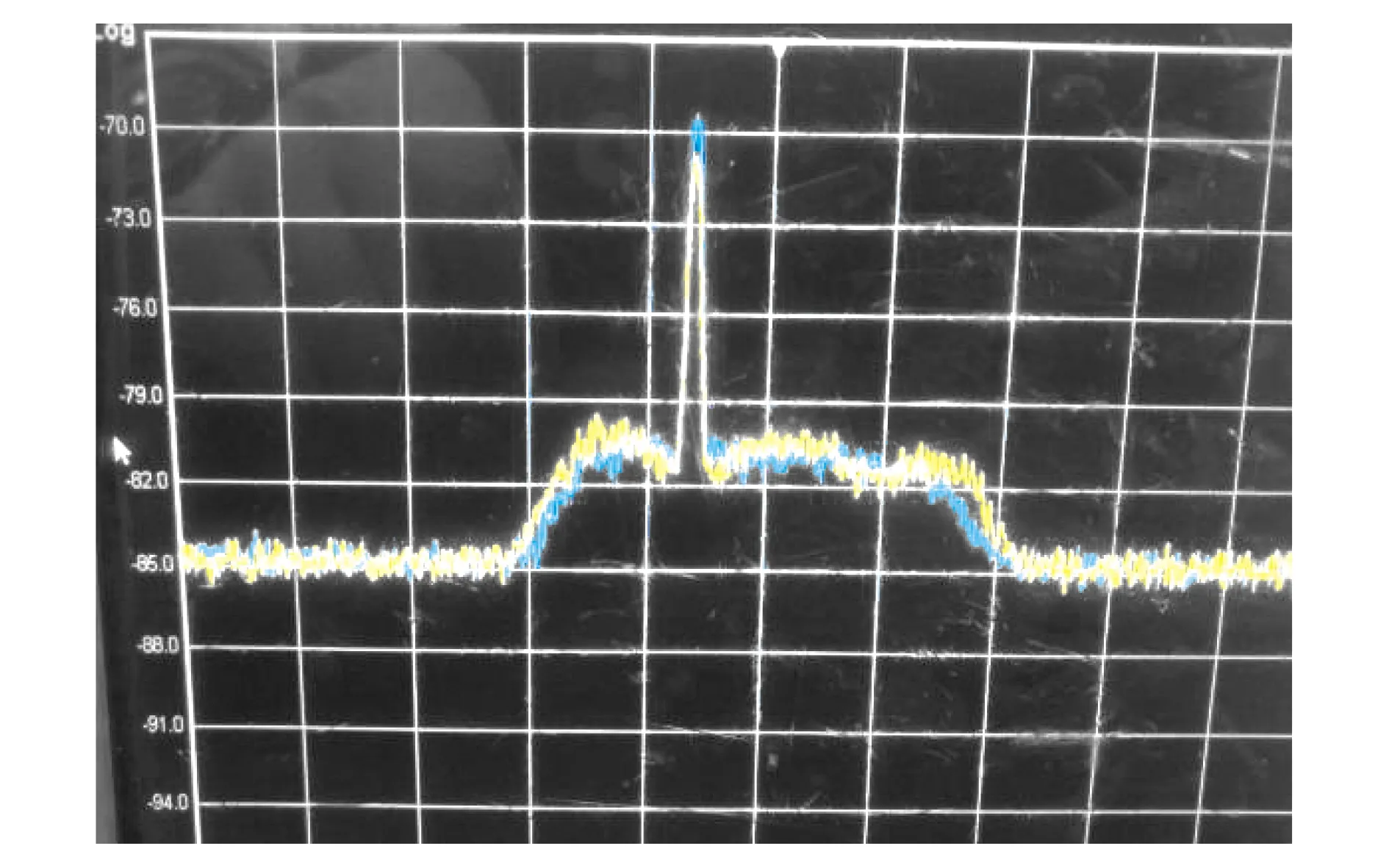

采用频谱仪观测DAC频谱来评估优化前后对信号质量的影响,其中抗干扰后频谱对比和单音直通对比分别如图5和图6所示.

图5 抗干扰DAC输出频谱图

如图5所示,优化前后,抗干扰输出的频谱几乎无变化;而图6显示优化方案不会造成频带内信号链路的衰减也没有产生频谱畸变或者新的频率分分量,优化方案在减少资源占用降低功耗同时不影响原设计的功能.

图6 单音直通模式DAC输出频谱图

4 结束语

本文在主流GNSS抗干扰处理器的架构基础上,综合采用抽取、欠采样和ODDR技术,通过改进软件架构,在不改变和不增加硬件的条件下,进一步降低芯片资源和功耗. 仿真和试验测试表明,优化策略在降低芯片资源和功耗时并不影响原有的抗干扰性能,可应用在GNSS智能抗干扰天线的低功耗设计中.

致谢:感谢王甲池博士以及牟传坤的讨论.