功率MOSFET工艺仿真验证研究

郑莹 迟辛格

(沈阳理工大学 辽宁省沈阳市 110159)

1 引言

功率MOSFET 器件是新一代的电子元器件,由于具有开关速度快、耗能低、稳定性好等优点[1-2],被广泛应用在汽车电子、节能灯、开关电源以及电机驱动等领域。目前,对功率MOSFET 器件的研制主要以逆向设计为主,依赖于现有加工工艺线水平和大量的实验流片,得到满足设计要求的芯片,这样不但需要花费大量的人力、物力,成本也较为昂贵,器件的研发周期也较长。随着计算机技术的快速发展以及对于半导体器件加工工艺的深入了解[3-4],各种各样的半导体模拟仿真软件应运而生,大大提高了器件的设计开发效率。因此,仿真与实验协同设计开发功率半导体器件成为当前研发的主要趋势[5-6]。本文将利用一款半导体模拟软件对已流片的功率MOSFET 器件进行单胞结构建模和工艺模拟仿真,为下一步优化参数提供方向,也为建立功率MOSFET 器件的设计开发平台提供理论和实验依据。

2 工作原理

图1 是P 型功率MOSFET 器件的单胞结构纵向剖面示意图。整个功率MOSFET 器件是由数千个这样的单胞结构并联而成的,作为功率MOSFET 器件的基本单元,该器件的三个电极分别为栅极G、源极S 和漏极D,与普通MOS 器件相比,该器件的不同之处是漏极端位于晶圆片的衬底,这可以大大提高晶圆片表面的利用率[7]。当栅源极短接时,漏极的负电压使得P-外延层和N-体区形成的PN 结反偏,耗尽层宽度以掺杂浓度较低的P-外延层一侧为主,随着漏极负电压的增大,耗尽层宽度也增大,直至达到结发生击穿,此时对应的漏极负电压为该器件的击穿电压BVdss,其强烈依赖于较低掺杂P-外延层的厚度和掺杂,厚度越厚,掺杂浓度越低,越容易击穿;当栅源电压达到某一负电压时,位于栅氧下方N-体区内部的表面区域形成强反型,源漏导通形成电流,此时对应的栅源负电压即为器件的阈值电压Vth,阈值电压的大小主要与N-体区的表面掺杂浓度、栅氧厚度和界面电荷等因素有关,表面掺杂浓度越大,栅氧厚度越厚,反型越困难,要想实现强反型,需要的阈值电压就会越大,另外,栅氧和体区表面界面处的杂质原子、结构缺陷或捕获的电荷等也会影响电场,从而进一步影响阈值电压。

3 工艺模拟与仿真验证

根据前期功率MOSFET 器件的结构与工艺设计要求,所使用的外延片是晶向<100>的P 型Si 外延片,外延片的掺杂浓度为5.9E14cm-3,外延层的厚度为40μm,单个元胞横向尺寸为32μm。

图1:P 型功率MOSFET 器件单胞结构纵向剖面示意图

图2:阱推后的器件结构图

图3:单胞结构图

功率MOSFET器件制作的主要工艺流程是在已有的外延片上,首先进行场氧化形成厚的氧化层,接着进行有源光刻和氧化层刻蚀以形成限定的器件区域,然后通过栅极氧化、多晶硅淀积、掺杂和退火、栅极刻蚀,形成具有周期性的栅极图案,再利用多晶硅的自对准,通过磷注入和退火形成N-体区,而硼注入和退火形成P+区,注入剂量和能量的选择是基于结构参数设计和扩散试验,由于N-体区和P+区在退火的过程中存在横向扩散且扩散的程度不同,因此在外延片表面形成了沟道,沟道的长度由二者横向扩散之差来决定。为了避免电极互连和短接,之后要进行绝缘厚氧化层的淀积和增密,并通过接触光刻和氧化层刻蚀形成源极接触窗口,再在整个芯片表面溅射一定厚度的金属层,形成用于功率MOSFET 器件的源极,为防止由P-外延层、N-体区和P+区形成的寄生三极管导通,需要将N-体区和P+区短接,因此这里的源极同时覆盖了N-体区和P+区这两个区域。为使得器件免受机械损伤,还要在整个芯片表面沉积一层钝化层,从而提高器件的可靠性。按照器件芯片正面版图布局的位置,通常在芯片边缘周围的某个固定区域分布着类似阵列式的金属触点,其与器件单元结构中的多晶硅电极相连,形成功率MOSFET 器件的栅极。为了满足现代电子元器件对芯片轻薄短小的要求,同时提高器件的驱动能力,最后要对晶圆片背面进行相应的减薄处理以降低导通电阻,并在背面做金属层,用作功率MOSFET 器件的漏极。

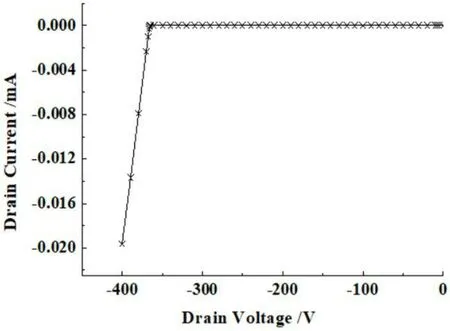

图4:击穿电压曲线

图5:阈值电压曲线

这里涉及的主要工艺步骤及其工艺条件如下:

· 场氧:450nm

· 注入B:1E12,40keV

· 退火:10′,1000℃,H2:7 L/min,O2:6 L/min

· 多晶硅:500 nm,7.5E19

· 阱注入:1.5E14,120keV

· 退火:90′,1100℃,N2:5 L/min,O2:1 L/min

· 注入B:3.5E15,60keV

· 低压淀积:900 nm

· 增密:950℃,N230′

· 溅射:AL,2 μm

流片过程中,通过单步工艺监控测得的场氧厚度、多晶硅厚度和方阻、栅氧厚度分别为445 nm、500 nm 和18.4 Ω/sq、90 nm;流片结束后对器件进行电参数测试,得到击穿电压BVdss=-369 V,阈值电压Vth=-6 V。

在此基础上,利用半导体仿真软件对该功率MOSFET 器件进行了工艺模拟仿真,图2 是仿真过程中阱注入并退火后的器件结构图,图中不同的灰度代表了不同的材料。由图可以看到,此时已形成栅氧和多晶硅栅极结构,但是,由于没有P+区的注入和退火,还没有形成沟道区;图3 是最终得到的器件单胞结构图,利用软件中的参数提取功能,得到最终的场氧、多晶硅和栅氧的厚度分别为450 nm、500 nm 和89 nm,多晶硅方阻为18.5 Ω/sq,均与实际工艺数值基本一致。

根据P 型功率MOSFET 器件的工作原理,当栅极电压达到阈值电压Vth 时,沟道区发生强反型,在漏源电压BVdss 的作用下,形成由源极S、P+区、沟道区、P-外延层到漏极的垂直电流流向,因此,在结构和电参数仿真时,为了能够最大程度的拟合现有条件下器件的工艺流程,不影响计算收敛和运算速度,需要重点在电流流过的区域合理划分网格,同时也需要充分考虑到实际界面电荷等对阈值电压的影响,进而选择合适的物理模型。图4 是仿真得到的击穿电压曲线,图5 是仿真得到的阈值电压曲线,从两幅图中可知,击穿电压BVdss 为-365.63V,阈值电压Vth 为-6V,与实际流片结果基本一致。

4 结论

传统功率MOSFET 器件的研发大多采用逆向设计的方法,不仅要花费大量的时间,而且多次流片的成本昂贵,器件研制效率低下,而借助于半导体仿真软件完成器件的设计和工艺流程制作,可以大大节约时间和成本,缩短器件的研发周期。本文基于一款P 型功率MOSFET 器件,介绍了器件的工作原理和工艺制作流程,依照前期器件结构和工艺设计结果,在半导体模拟软件中对器件结构建模,匹配合适的物理模型,合理划分网格,对各个单步工艺进行了工艺模拟仿真,最终得到的器件电参数仿真结果与实际流片结果基本一致,为下一步器件优化奠定基础,也为后续类似器件的开发提供参考。