基于FPGA的高速大容量数据缓存单元设计

丁 辉,张会新,庞俊奇

(中北大学,电子测试技术重点实验室,山西太原 030051)

0 引言

随着科学技术的快速发展,人类在信息科学技术上有着越来越高的需求,主要的表现形式是更快和更多地接收信息,因此需要专用的设备来对这些信息进行高速接收与精确的处理[1]。在许多的产品中,FPGA外挂DDR3作为存储器有着广泛的应用,通常采用的是FPGA自带的IP Core 进行开发设计,缩短开发周期[2]。由于DDR3只有一套数据访问通道,无法满足多通道数据输入的要求,本设计提出一种分地址存储技术可以对多通道数据进行分别存储,加速了数据存储的速度,并且使用2组DDR3,采用乒乓读写的方式,极大地缩短了数据读写的时间。

1 高速大容量数据缓存器方案设计

高速大容量数据缓存器是针对一些高速大容量数据无法及时存储和处理而设计的一种缓存器,如图1所示,本设计中使用的是高速串行接口GTP进行数据的传输,单通道GTP接口速度最快可达6.6 Gbit/s,数据输入后进入接收总线模块,此模块主要用于将传输的输入数据位宽进行匹配,然后产生数据的写地址信号与写数据信号同时接收来自下一级的写反馈信号[3]。

图1 高速大容量数据缓存器整体设计框图

接收总线产生地址与数据信号后,将信号输入到写仲裁模块,本设计中采用的是2片DDR3切换进行读写的方式,所以数据进入写仲裁模块进行相应的判断,将数据与地址输出到相对应的DDR3模块中,设计中是2片DDR3读写切换进行,所以在完成对一片DDR3写入时,要接着进行读取,所以读仲裁模块在进行相应的判断之后,产生相应的读数据地址信号输入到DDR3中对其进行数据的读取操作,最后数据在读数据模块进行整合后输出到外部进行存储或者直接处理[4]。

2 总线接口模块设计

本设计中使用的是GTP高速串行接口进行数据传输,输入为4路的高速GTP,为了传输信号的稳定,每路的输入速率为3 Gbit/s,当4路同时进行数据传输时,接收模块瞬间接收到高达12 Gbit/s的数据输入[5],如图2所示,四通道串行数据经过解串之后输出为位宽32位的并行数据,同时总线接收模块产生相应的地址信号输入到写仲裁模块中。此时FPGA使用的时钟频率为400 MHz,当输入为12 Gbit/s的数据量时,将串行数据转为32位的并行数据进行存储,可以满足速率要求。

图2 接收总线模块示意图

3 数据缓存模块设计与优化

数据缓存部分主要包括3部分,数据写入仲裁模块,数据读出仲裁模块,2组DDR3缓存单元。数据写入仲裁模块主要是将外部传来的数据经过仲裁之后将数据与地址输入到相应的存储单元,数据读出模块是及时地经过仲裁将已有数据的缓存单元中的数据及时读出,避免造成大量数据的堆积导致数据出现覆盖、丢失[6]。

3.1 DDR3缓存单元

DDR SDRAM是双倍数据速率端口动态随机存储器。DDR SDRAM在每个时钟中期的上升和下降沿各传送一次数据,提高了数据传输带宽[7]。DDR3缓存单元采用的是2个DDR3组成一组DDR3,每个DDR3的存取位宽为16位,2个DDR3并联通过一个DDR3控制器控制,形成32位宽的存取接口,满足数据输入端口的位宽要求。为了提高总线的利用率,DDR3 SDRAM使用的是8n预取结构,其中n表示DRAM芯片的数据I/O宽度,8是指数据的突发长度,突发长度是指数据单次可以采集到的数据量,指的是当发送单个地址时,数据引脚会传送8n个总线字的数据,本缓存单元数据位宽为32位,采用8 bit预取的方式进行读写时,核心频率使用100 MHz时,存取的速度可达32×8×2×100=50 Gbit/s,考虑到一些控制信号的总线资源利用以及考虑到实际DDR3总线利用率不高的因素外,50 Gbit/s的存取速率数完全可以满足12 Gbit/s数据量。本单元采用的是2组DDR3存储单元进行乒乓交互读取,在第一组DDR3_0写入数据时,另一组DDR3_1进行数据的读出,两组进行交互读取,实现了数据总的存取速率到达24 Gbit/s以上,图3为缓存单元的结构示意图。

图3 缓存单元结构示意图

3.2 写数据仲裁模块

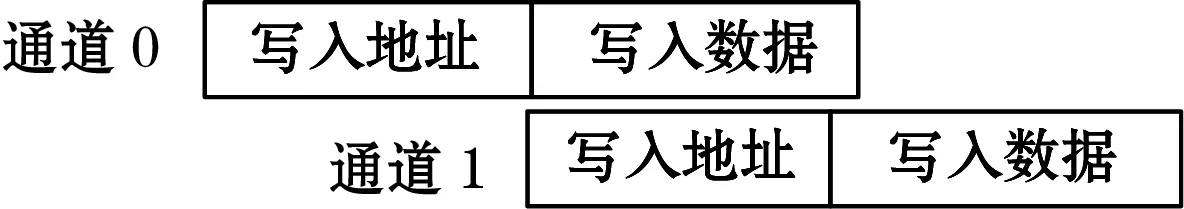

仲裁模块为每个通道分配地址空间进行数据存储,2个通道传输数据时独立进行,互相没有干扰,当数据流进入仲裁模块时,仲裁模块进行判断,当仲裁模块将数据与地址写入到DDR3_0通道时,在DDR3_0通道写入数据的同时,仲裁模块可以产生新的地址信号输入到DDR3_1的模块中去,等到下一帧数据到来的时候,直接将数据输入到DDR3_1模块中去,可以极大地缩短地址输入DDR模块时的等待时间,同时这种交替数据输入的方式可以使2个通道的负载均衡[8]。数据交替流入的结构图如图4所示。

图4 数据交替写入示意图

本设计中采用的是两通道DDR3缓存单元,因此可以直接采用flag标志位置为0或者1来对通道进行选通,设计中地址输入总线和数据输入总线是相互独立,所以可以分别对其设置状态标志位,分别为flag_waddr和flag_wdata两个信号。写标志位的逻辑发生变化是以写入数据的一个突发长度为单位,当第一个通道写入一个突发长度数据时,写标志位发生翻转,开始准备将下一个突发长度的数据写入第二个通道[9]。具体的流程如图5所示,首先初始化flag_waddr=0,awaddr地址信号发出,同时使能awvalid信号,此时表示输入DDR3控制器的地址信号有效,DDR3发出app_rdy信号为高时表示允许接收地址信号,此时完成地址的传输,flag_waddr信号翻转为1,开始向另一个通道传输地址信号。如图6,当写入数据时,第一个通道地址传输同时,即可将数据写入到通道中,等到一个数据突发长度完成后,flag_wdata标志翻转,开始往另一个通道传输数据。2个通道相互独立,写入第一个通道数据的同时,可以将地址写入到第二个通道内,节省等待数据传输完成的时间。

图5 地址信号写入仲裁逻辑图

图6 数据信号写入仲裁流程图

3.3 读数据仲裁模块

DDR3缓存单元的数据读出时,地址输入和数据输出是2组不同的通道,是相互独立的,所以分别为读地址和读数据设置1个判断标志位,分别为flag_raddr和flag_rdata 2个信号,读标志位的判断也是以1次突发长度为单位[10]。读数据仲裁逻辑判断如图7所示。

图7 读数据仲裁模块逻辑图

3.4 乒乓读写仲裁

DDR3数据的读写使用的是同一组地址线,因此在同一时刻我们只能对同一组DDR3芯片进行读或者写操作,为了提高总线的数据读取效率,所以读取和写入数据缓存单元数据时,本设计采用的是乒乓读写的方式,在对其中一个通道写入/读取时,同时对另一个通道进行读取/写入,两组通道同时进行工作,大大缩短了数据读出缓存单元的时间,同时也可以使数据得到更加快速的处理,图8为数据读写时的控制逻辑[11]。

图8 数据读写控制流程图

3.5 AXI4总线

本设计采用AXI4总线控制的方式进行数据传输,AXI协议适合高带宽低延时的设计,而且可以使互联模块之间的灵活性和独立性很强,其地址、数据、控制总线的输出相互分离,而且使用基于burst的数据传输方式,综合以上特点,本设计中缓存单元的读写控制采用AXI4总线[12]。设计中生成的DDR3控制器设计带有AXI4接口的控制器,总线接收模块和总线发送模块通过AXI4总线分别向写仲裁模块和读仲裁模块输入相应的命令、地址、数据进行控制,图9为AXI4总线接口信号图。AXI4也具有握手机制,当主机准备好地址信息,且当awvalid信号为高时,表示地址数据有效,同时接收到从机发送来的awready信号为高时,说明从机可以接收地址信号,完成一次地址信号的传输。数据信号也是在从机wready信号为高时,主机将数据输入到从机中,wlast信号是提醒从机发送最后一个数据。

图9 AXI4总线接口数据信号

4 数据测试仿真结果

图10为写仲裁模块对写入2个通道DDR3的地址进行分配和数据写入,图11为读仲裁模块将接收的数据分别从2个通道DDR3数据读出时的仿真图。

图10 Vivado软件下写仲裁模块地址与数据写入仿真

图11 Vivado软件下读仲裁模块地址写入和数据读出仿真

5 结论

对于高速数据缓存单元的设计,设计中采用2通道DDR3进行存储,采用2通道交替写入的方式,对其中一通道写数据时,另一通道写地址,一方面节省了等待时间,另一方面2片存储器存入的数据均衡,同时采用了乒乓读写的方式,提高了整体读写的速率,有助于数据及时进行处理,也避免大量数据堆积的情况,采用这2种优化的方式,极大提升了缓存单元的性能,解决了因采集数据速率快,数据量大,无法进行及时存储导致数据丢失、覆盖等问题,将在高速设计中得到广泛的应用。