一种抗单粒子瞬态加固的压控延迟线设计

史柱, 王斌, 赵雁鹏, 杨博, 卢红利, 高利军, 刘文平

(西安微电子技术研究所,陕西,西安 710065)

随着航天技术的发展,空间任务对宇航用大规模集成电路的性能提出了更高的要求,以满足海量在轨数据的处理需求. 目前的宇航级集成电路中,已经集成了各种高速接口[1-2],其中包括内存接口、高速总线接口等. 在这些接口电路中,当不需要时钟综合或者频率变化时,延迟锁相环(delay locked loops,DLLs)由于设计简单、具有更低的抖动性而成为时钟和控制信号的主要来源[3-4].

单粒子瞬态指的是高能粒子入射集成电路中的敏感节点时,产生大量的自由载流子通过漂移和扩散,引起的节点电压的扰动. 随着集成电路加工尺寸的不断降低,电路工作频率的不断提高,SET引发的空间应用集成电路中的软错误率愈发受到关注. 研究表明[5-6],压控延迟线是唯一能够在时钟信号的输出端产生丢失脉冲的模块,与电荷泵同为延迟锁相环或者锁相环(phase locked loops,PLLs)中对单粒子事件最为敏感的子电路. 近年来,不少学者将研究的重点集中在压控延迟线的加固上,包括偏置电路和基本延时单元加固. STEPHEN等[7]对基本的延时单元做了冗余备份,然后通过组合逻辑电路,滤除了受到单粒子轰击的输出信号,从而起到了加固效果,但是每个单元都做备份使得压控延迟线的面积和功耗显著增加. QIN等[8]提出了交叉耦合负载结构的延时单元,通过自身负载的正反馈作用抑制节点电压的翻转,但是在尺寸较小的情况下,加固效果并不明显. PIERRE等[9]提出了一种检测补偿电路,通过增加两个运放检测电压的变化,从而控制一个充电管或放电管导通以维持偏置电压恒定,但是运放自身又有引入了敏感节点,且对运放的速度要求较高,设计困难. 赵振宇等[10]通过只增加一个PMOS管、一个NMOS管和一个电阻构成了加固结构,但是必须在电压波动超过一个阈值电压的情况下,才能打开补偿管或者放电管,对于偏置电压波动较小时,并无加固作用.

针对现有加固方法的局限性,本文对压控延迟线的两个主体部分——偏置电路和延时单元中的SET分别采取了不同的处理措施. 对于管子数目较小的偏置模块,通过模拟冗余的方式,对其进行复制,并将输出偏置电压相同的节点连接起来,增加节点电容和支路的驱动能力;对于SET产生概率较低但影响不可忽略的延时单元,本文提出了相应的锁定检测电路,将发生SET的输出信号及时显示出来,以此来提高延迟锁相环输出信号的可靠性.

1 电路结构及敏感性分析

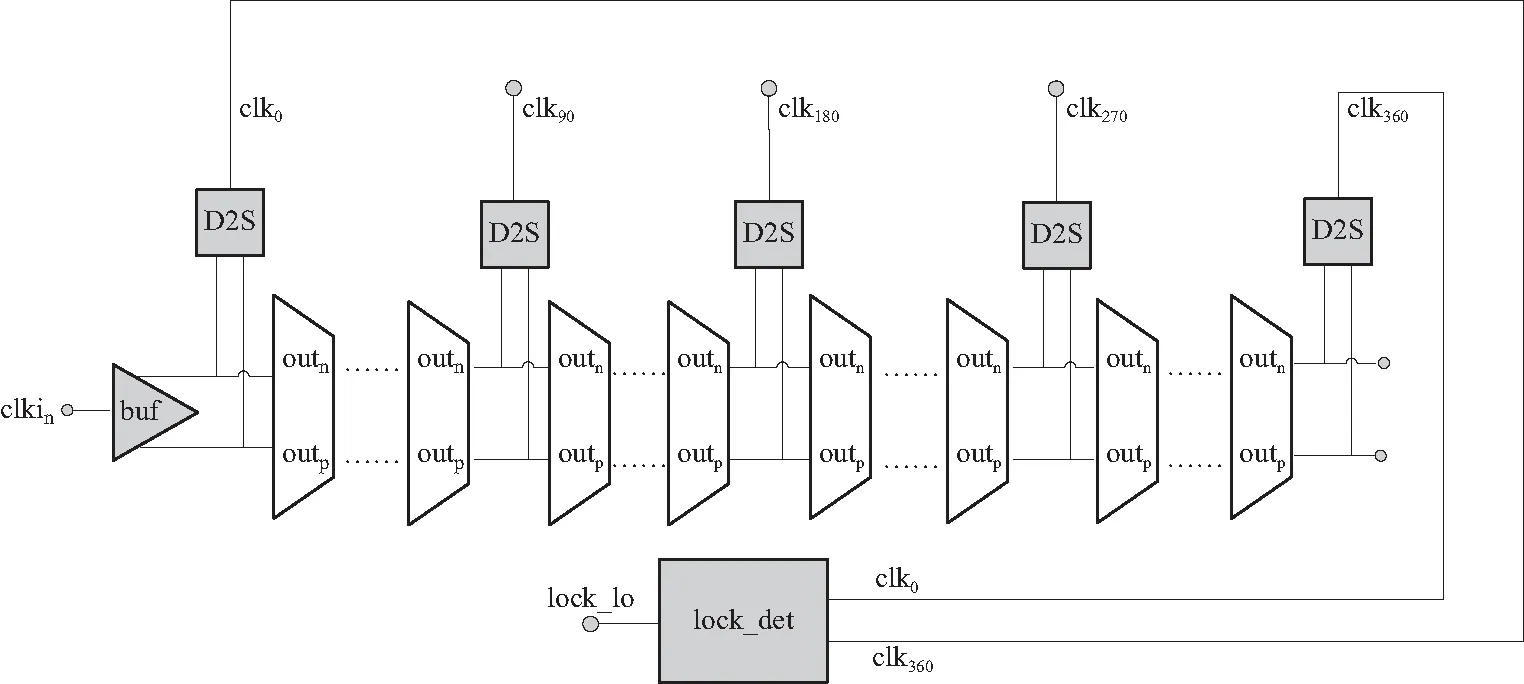

图1为延迟锁相环中的压控延迟线. 输入参考时钟clkin经过缓冲级之后,分成两路差分模拟信号,同时经过双端转单端电路(D2S)生成clk0时钟信号. 然后,每经过1/4总长度的延时单元,便通过相同的过程产生一路单相时钟,依次分别形成相位差为90°的四相时钟clk90,clk180,clk270和clk360. 这样具有固定相位差的信号,便可以作为高速内存的数据读写控制信号.

图1 延迟锁相环中的压控延迟线Fig.1 The voltage-controlled delay line in a DLL

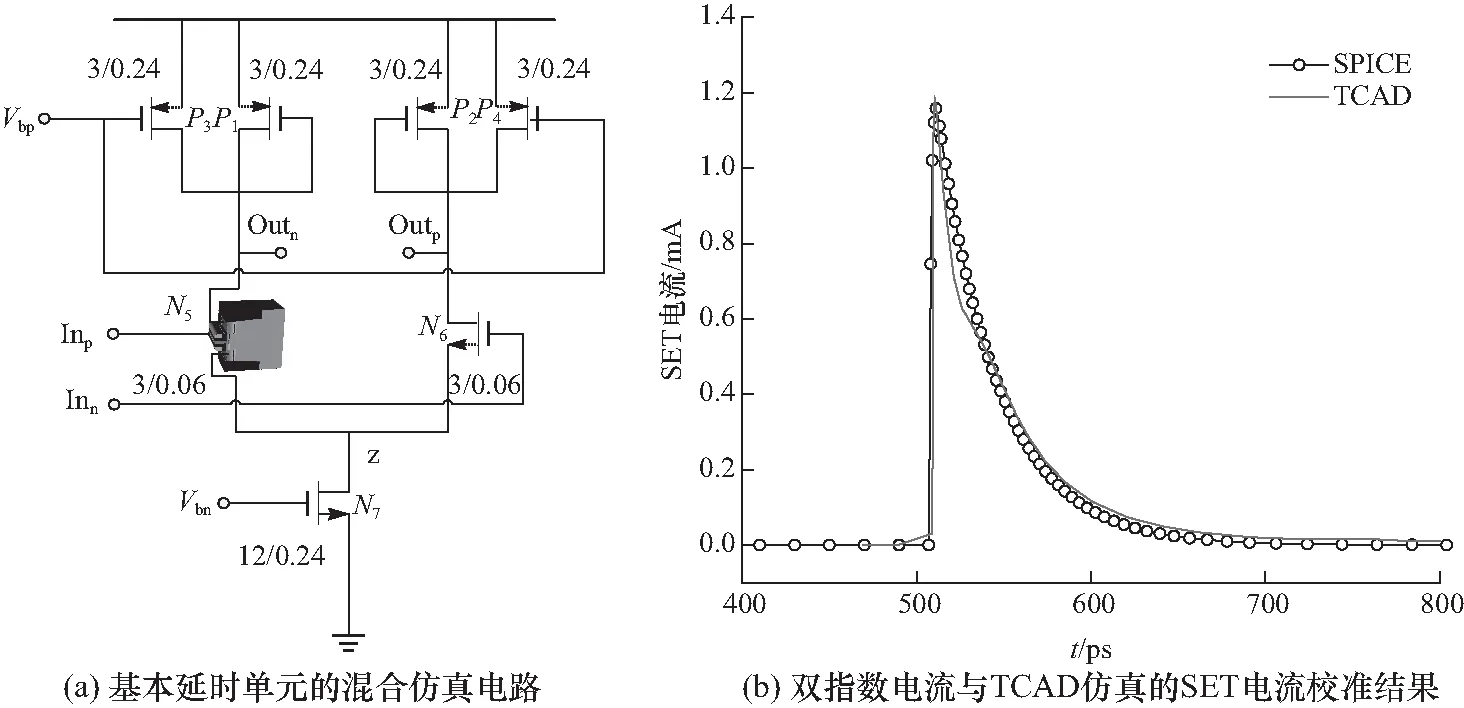

事实上,完整的压控延迟线不仅包含重复的延时单元、D2S模块,还包括调整单级延时单元延时大小的偏置电路[11]. 研究表明[12-14],偏置电路才是压控延迟线或者压控振荡器中对单粒子事件最为敏感的模块,其产生的SET响应持续时间更长. 因此,本文将依次对延时单元和偏置电路的单粒子敏感性分别进行分析. 图2(a)为延时单元的TCAD混合仿真电路,将经过工艺校准的三维NMOS器件代替Spice模型,再进行单粒子入射得到SET电流. 然后,利用Spice仿真中的双指数电流源与三维器件产生的SET电流拟合,作为整个延迟锁相环仿真时的粒子入射条件. 该电流模型如式(1)所示.

(1)

式中:I0表示双指数电流脉冲峰值;τr和τf分别为上升和下降时间常数. 图2(b)给出了在本文的电路尺寸、工作点以及工艺条件下,入射粒子能量为80 MeV·cm2/mg时,双指数电流与TCAD混合仿真中的SET电流拟合结果:I0=1.18 mA,τr=6 ps,τf=35 ps.

图2 基本延时单元中SET电流校准过程Fig.2 The SET current calibration process of the basic delay cell

根据本文设计,除了clk0之外,每经过5级基本延时单元便产生一路单相时钟. 延时单元之间传输着相位交替的差分信号,前一级的输出即为后一级的输入. 图3是延时单元的输出信号与输出时钟之间的关系:当Outn高于Outp时,D2S模块将该状态转换为高电平,下一个时刻则为低电平. 在1 GHz的输入参考时钟频率下,一个延时单元的周期即为时钟周期,1 ns. 将拟合好的双指数电流作为Spice仿真中的粒子入射条件,对实际工作中的延迟锁相环进行轰击. 分析表明,输出节点为延时单元中最敏感节点,当Outn输出为高时,对该节点的轰击会造成时钟的错误翻转. 为了方便描述不同时刻的单粒子敏感性,对于一个延时单元输出的高电位,采用7个点ti,i=1~7,将波形周期平均分成6份.

图3 延时单元的输出信号与时钟的关系Fig.3 The relationship between output signals of a delay cell and clock

现将延时单元的敏感性分析结果总结如下.

1) 如果轰击时间为t1时刻,那么不分延时级,从轰击的那一级开始,往后的所有时钟占空比都会发生一个周期的变化.

2) 如果轰击发生在t2时刻(或者t1与t2之间的任意时刻),那么只有产生时钟的那一级(第5级)或者前一级受到轰击才会导致被轰击级对应的时钟变化,其他时钟不变.t2~t6时刻(不包括t2),不论哪一延时单元受到轰击,都不会产生输出波形变化,主要是由于轰击产生的Outn低于Outp持续时间较短,未被D2S模块识别;而t7时刻,本来就是Outn开始低于Outp的点,即使受到轰击,只会加速Outn下降速度,并不影响时钟波形.

3) 在本文给定的电路尺寸和LET值为80 MeV·cm2/mg的粒子入射条件下,轰击延时单元只发生了占空比变化的现象,而且只产生一个时钟周期的影响.

图4为压控延迟线中偏置电压产生的线路结构. 通过两路电流镜确定电路的电流,进而产生偏置电压Vbn和Vbp. 图中的Vpmrr和Vtrim为固定电压,由电荷泵的输出电压Vc不断调节P2管的电流大小,进而调节Vbn和Vbp,改变延时单元的延时. 同样采用拟合的双指数电流作为入射条件的Spice仿真方法[15],遍历a,b,c,d,e5个节点,得出d,e点是偏置电路中最敏感的节点. 这两点的电压扰动会直接改变延时单元的输出波形,造成多个周期的波形畸变.

图4 压控延迟线的偏置电路Fig.4 The bias circuit of the voltage-controlled delay line

2 单粒子瞬态的加固措施

根据前文分析,压控延时单元和偏置电路都是对SE敏感的模块. 在敏感性分析时发现,偏置电路产生的SET更为严重,影响可能会持续更久;而压控延时单元受到轰击之后只产生一个时钟周期的波形畸变. 因此,根据SET响应的严重程度和电路结构的不同,本文分别制定了不同的加固方案:对于偏置电路,采用模拟冗余的设计方法[16]来降低偏置电压Vbn和Vbp的扰动幅度;对于延时单元而言,因为其影响较小,且只在特殊的时刻才会产生SET响应,因此没有必要使用三模冗余(triple modular redundancy,TMR)等付出巨大性能牺牲的方法[17]专门进行加固. 本文设计了一种用于检测延时单元SET响应的电路,该电路将发生畸变的时钟显示出来,以提高时钟信号的可靠性.

图5为偏置电路加固后的线路结构图. 由于电路中管子数目较少,因此可以通过模拟冗余的方法,复制一套偏置电路,然后将偏置电压的输出节点通过阻值相同的电阻连接,并引出最终的输出节点,再用电容进一步稳定. 资料表明[18],如果原电路受轰击后偏置电压扰动幅度为ΔV,那么复制M份之后,该扰动将会降低为ΔV/M. 本文正是基于此思想,设计了一份冗余电路,来降低偏置电压的扰动.

图5 偏置电路加固方法Fig.5 The hardened method of the bias circuit

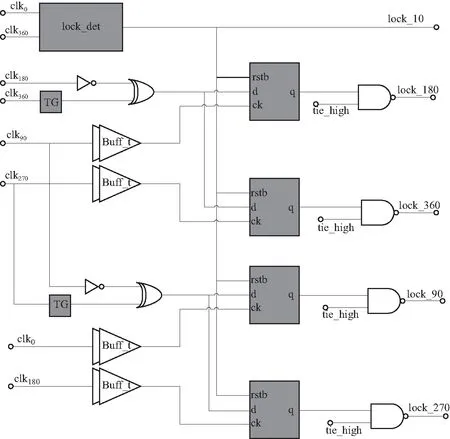

对于压控延时单元,可以根据输出四相时钟之间的相位关系,通过逻辑运算来检测出波形发生畸变的时钟信号. 图6为设计的SET检测电路,图中Buff_t为采样时钟缓冲器,tie_high恒定为高,可认为数字“1”. 正常工作条件下,锁定之后,clk180与clk360,clk90与clk270之间的相位为互补关系. 通过相互之间的异或运算来检测受到轰击的输出时钟信号.

图6 压控延时线中的SET检测电路Fig.6 The SET detection circuit in the voltage-controlled delay line

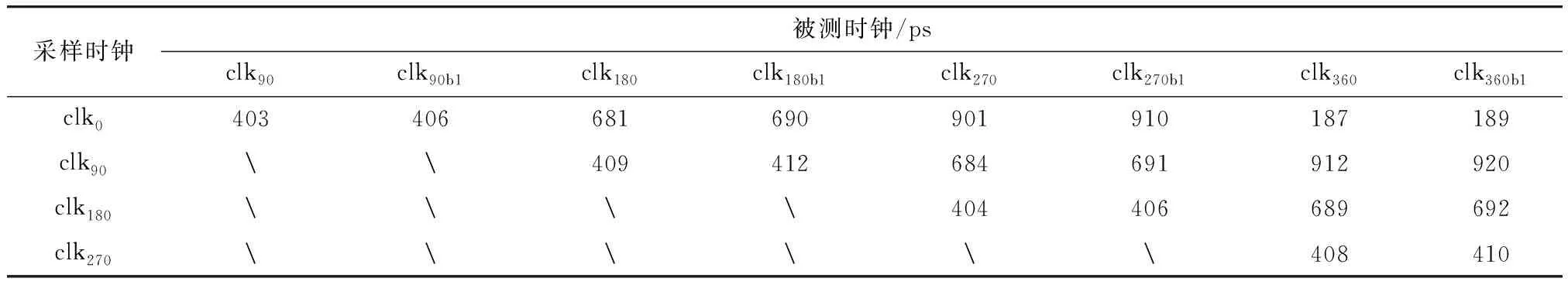

表1给出了采样时钟上升沿到被测时钟产生的SET脉冲中心的时间间隔,可以发现,以90°相位差的前一相时钟采样,具有几乎固定的延时大小,同时还可以定位出错的时钟. 表中clk90b1,clk180b1,clk270b1>以及clk360b1分别表示该路时钟产生的延时单元的前一级在t2时刻受到轰击产生的时钟.

表1 采样时钟与SET脉冲间隔时间的关系Tab.1 The relationship between sampling clock and the interval of SET pulses

在该电路设计中,为保证电路正常工作,需要有一路时钟保证其波形的正确性. 根据延时单元中的SET出现的特殊性,若使用三模冗余加固可以使得clk0免受单粒子干扰. SET检测电路的工作原理如下:在未锁定时,lock_lo一直保持为高,电路处于复位状态,输出的结果无效;当clk0与clk360上升沿时间差处于锁定误差范围内时,lock_lo拉低,电路锁定,lock_90~lock_360输出为高;在所有的输出结果中,以lock_lo的优先级为最高,如果该信号发生了跳变,那么需要将所有的输出时钟同时无效,直到电路重新锁定.

3 仿真结果与分析

通过双指数电流源对压控延时单元中3-D TCAD混合仿真产生的SET电流进行拟合. 将拟合好的电流作为Spice仿真中的粒子入射条件,轰击敏感节点,得出在实际工作状态下的延迟锁相环中压控延迟线的SET响应,并验证其加固效果.

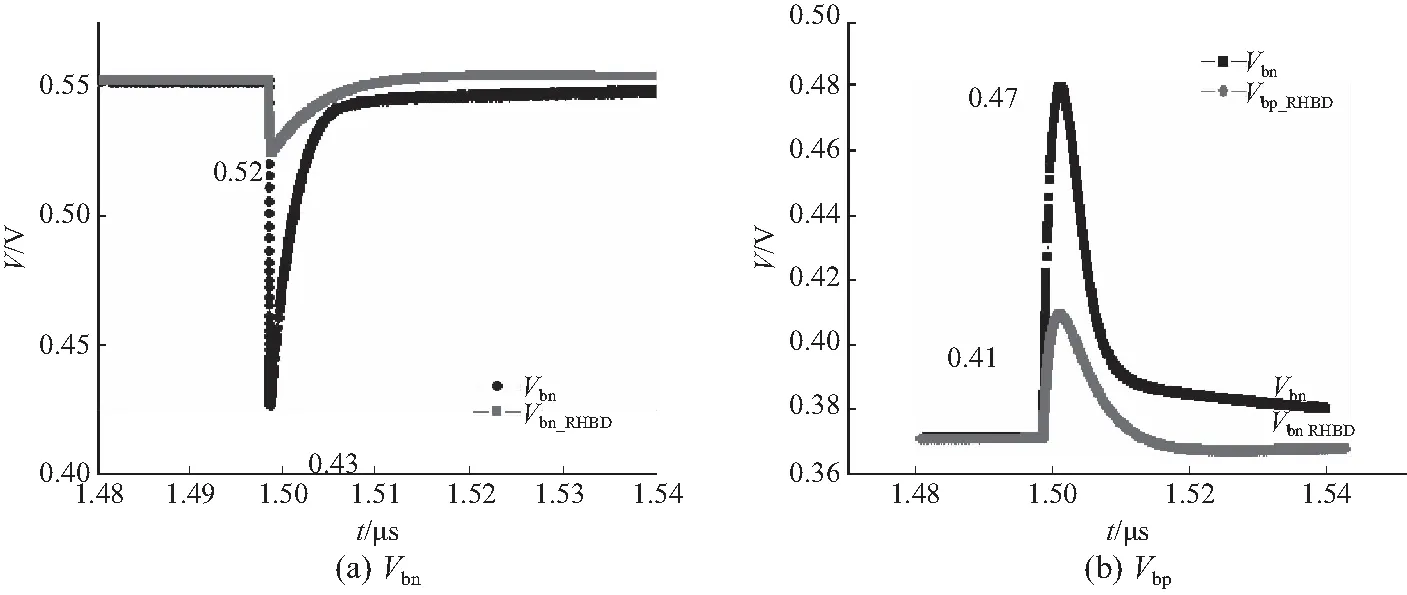

如图7所示,给出了加固前后,偏置电路中d点和e点分别受到粒子入射之后,Vbn和Vbp节点的电压翻转幅度. 结果显示在未加固的偏置电路中,当1.5 μs受到单粒子轰击之后,Vbn从0.55 V降至最低的0.43 V,翻转幅度为0.12 V;Vbp从0.37 V升至最高的0.47 V,扰动电压高达0.1 V;加固之后,Vbn的最低值为0.52 V,幅度为0.03 V,和未加固相比,翻转幅度下降了75%;Vbp的最高点为0.41 V,翻转幅度降低了60%,起到了明显的加固作用.

图7 加固前后偏置电压的变化Fig.7 The variation of bias voltage before and after hardening

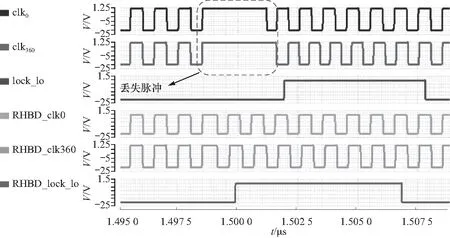

为了进一步验证偏置电路加固的效果,通过Spice仿真,用单粒子轰击实际工作中的延迟锁相环偏置电路中的d点. 图8给出了偏置电路加固前后的输出时钟波形和锁定检测结果. 从图中可知,在未加固的电路中,出现了丢失脉冲现象,而且锁定检测信号lock_lo并未将这种错误指示出来. 然而,在加固之后的偏置电路中,丢失脉冲现象不存在,只出现了轻微的时序失配.

图8 加固前后的输出时钟波形对比Fig.8 The comparison of output clock before and after hardening

图9给出了提出的压控延时单元中的SET检测电路工作情况. 图9(a)为了clk90的产生级在t1时刻受到轰击之后的检测结果. 从图中可以发现,自clk90之后的所有时钟都发生了一个时钟周期的占空比错误,并且lock_lo被拉高. 这种情况下,以lock_lo输出信号优先级最高,为了保证数据传输的正确性,需要将以clk0~clk360为采样时钟的数据或者控制信号无效一个周期.

图9(b)中,clk180产生级的前一级受到轰击,lock_180被拉低一个周期,将占空比的错误指示出来. 但是这个时候,为了保险起见,也需要将clk270无效一个周期,因为clk180是clk270的采样时钟,clk180出现错误,不一定能将有可能同时发生的clk270的错误显示出来. 但是其他时钟clk0,clk90和clk360信号保持有效,因为lock_lo一直为低. 同理,如果只是clk90发生了一个占空比错误,也需要将clk180,clk270都无效一个周期.

图9 不同时刻轰击不同延时级的加固效果Fig.9 The hardening results of different delay cells struck at different time

需要补充说明的是,如果只是clk360的延时级或者该延时级的前一级在t2时刻受到轰击导致该时钟发生占空比错误. 这种情况不仅被lock_360检测出来,锁定检测信号lock_lo也会检测出来,同样需要把所有时钟信号无效一个周期. 综上所述,发生在压控延时单元中的所有SET响应都可以被提出的检测电路捕获,因此提高了输出信号的可靠性.

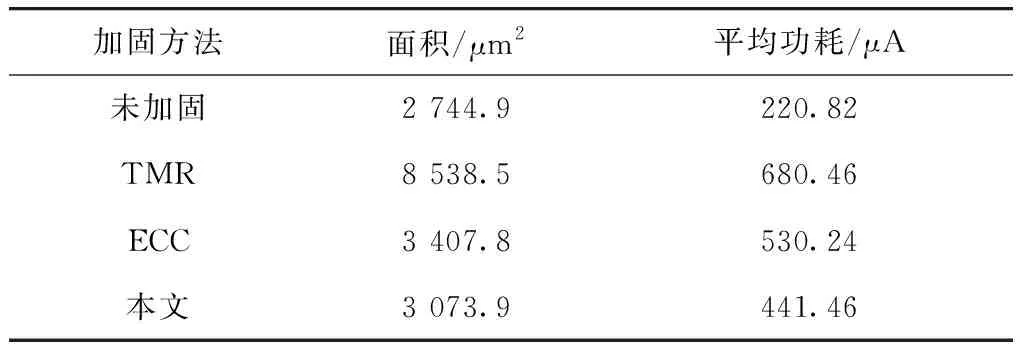

集成电路的辐射加固设计通常是以牺牲性能为代价,换取了可靠性的提高,本文中的方法也不例外. 针对压控延迟线中的延时单元,本文将几种加固方法:三模冗余(TMR)、文献[7]中的错误校正电路(ECC)以及本文的检测电路在本电路中进行了仿真,结果如表2所示.

表2 压控延迟线的不同加固方法对比

从表2结果来看,本文提出的加固方法从面积和功耗方面都具有一定的优势. TMR对于数字电路而言,几乎达到了单粒子完全免疫的效果,但是功耗和面积代价太大;ECC方法能够直接滤除被轰击单元中的单粒子瞬态,但是其所能承受的入射粒子能量有限,一旦发生了错误,便无法恢复. 本文提出的加固方法,针对内存接口的应用,能够将高达80 MeV·cm2/mg的入射粒子产生的单粒子瞬态检测出来,通过将错误信号无效,从而保证了数据的可靠性,达到了很好的加固效果.

4 结 论

本文首先利用双指数电流源拟合了TCAD仿真中的SET电流,以此为Spice仿真的粒子入射条件,分析了压控延迟线中偏置电路和压控延时单元的单粒子事件敏感性. 根据SET响应程度的不同,分别制定了不同的加固措施. 偏置电路中的冗余设计使得偏置电压Vbn和Vbp在受到粒子轰击后,翻转幅度分别下降了75%和60%,消除了输出时钟信号中的丢失脉冲;对于压控延时单元,因为其SET响应与轰击的级数以及时刻密切相关,且造成的影响只维持一个时钟周期. 对于这种发生概率较低的错误,设计了SET检测电路. 仿真结果表明,在1 GHz的输入参考时钟频率下,设计出的检测电路能够将各种情况下有可能出现的SET响应检测出来,提高了输出时钟信号的可靠性. 本文设计的抗单粒子瞬态加固压控延迟线可用于面向空间应用的延迟锁相环中.