基于FPGA的数字式锁定放大器设计

杨晨曦

(电子科技大学 电子科学与工程学院,四川成都,611731)

0 引言

在实际工程中,常常需要进行微弱信号的检测。而本数字式锁定放大器采用相关检测法实现了数字相敏的检波,通过噪声信号和确定性信号的相关特性实现有用信号的提取。一般情况下,有用信号在时域上不同时刻的取值具有相关性,而比如热噪声之类的干扰噪声具有随机性,因此,可以利用这一特性差异,区分出有用信号与干扰噪声[1-2]。

1 数字相敏检波

■1.1 数字相敏检波特点

采用数字相敏检波,可以方便进行低频信号的检测。在模拟式相敏检测器中,当参考信号频率很低时,相敏检波器的Q值会严重下降,而数字相敏检波不会,而且由于数字信号处理的特性,使得数字相敏检波有很高的线性度。且由于FPGA代码便于修改,可以对工作频率、时间常数、灵敏度等参数进行灵活控制,使得数字相敏检波有很好的灵活性[2]。

■1.2 数字相敏检波原理

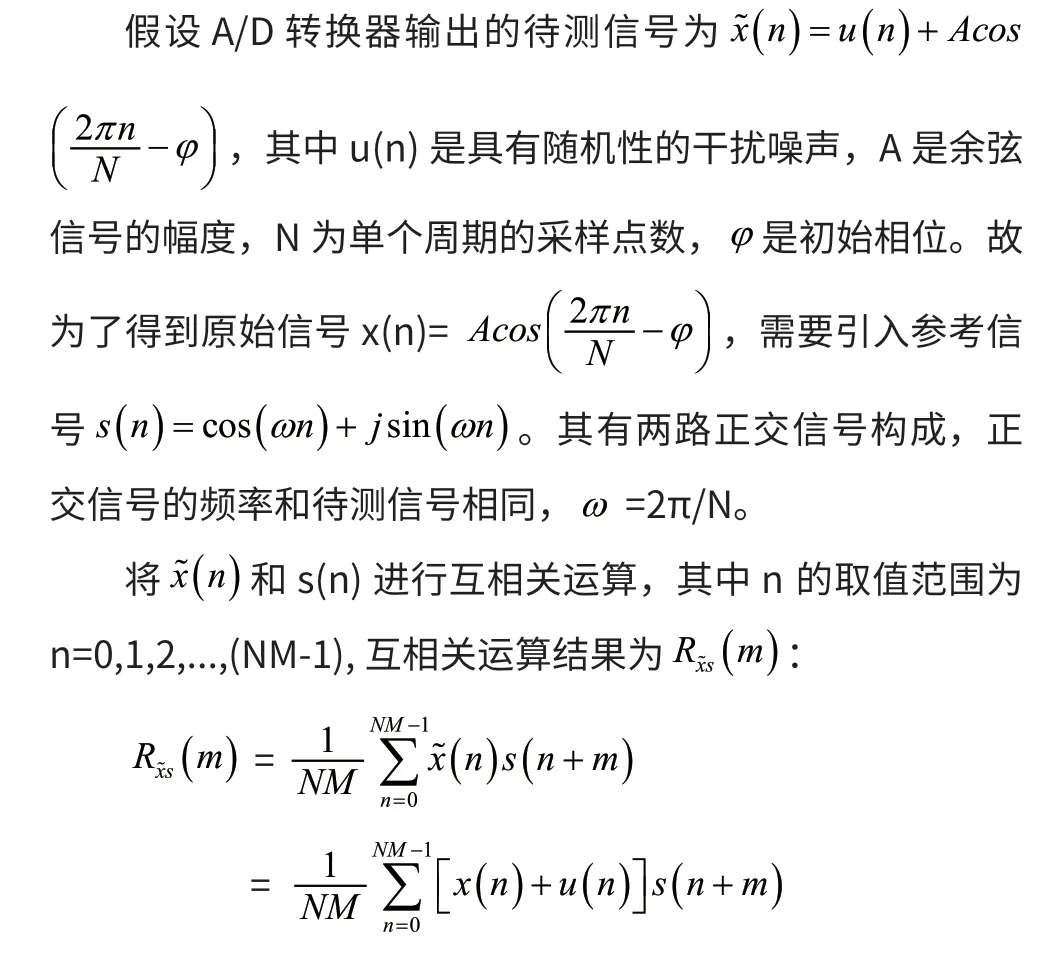

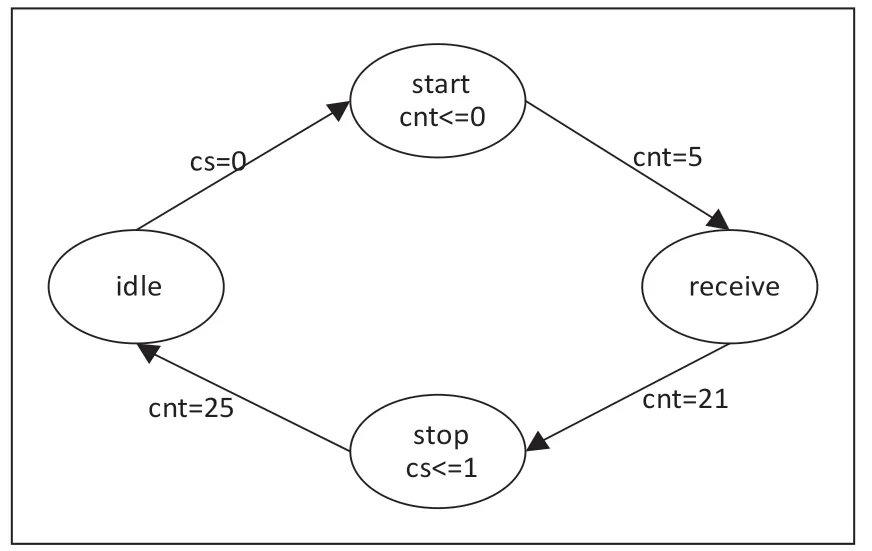

综上,数字相敏检波可以很好的抑制随机噪声的干扰,提取出微弱的有用信号,并且使用起来比模拟相敏检波更加的灵活方便[3]。数字相敏检波的原理如图1所示。

图1 数字相敏检波原理图

2 数字式锁定放大器设计

■2.1 数字式锁定放大器框架

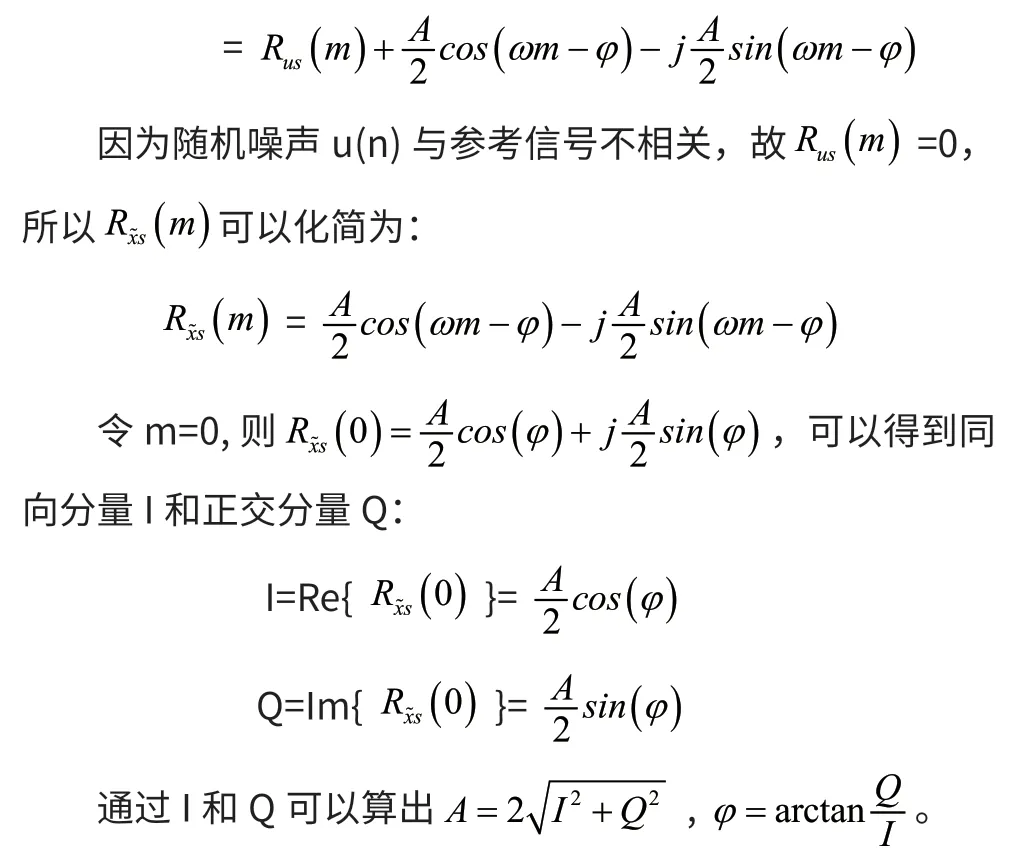

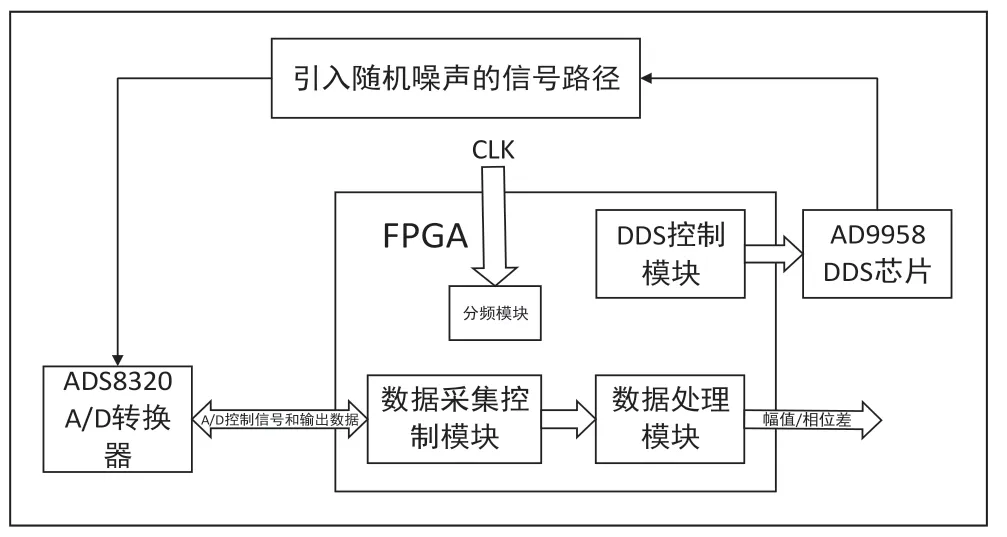

在设计中采用ADS8320作为A/D转换器,50MHz外部晶振作为系统时钟,以12.8kHz的采样频率对200Hz的正弦信号进行采样,即每个正弦周期采样64个点。正弦待测信号和参考信号通过直接数字频率合成器(DDS)芯片AD9958生成。

数字式锁定放大器的系统框图如图2所示。FPGA内部有分频模块、数据采集控制模块、DDS控制模块和数据处理模块四个部分组成。系统工作流程为FPGA通过DDS控制模块对AD9958进行控制,使其产生两路正交的正弦信号,一路正弦信号经过会引入随机噪声的路径后到达A/D转换芯片,进行数字化处理,另外原始的两路正交的正弦信号直接送入A/D芯片。随后FPGA采集控制模块控制A/D芯片进行数据的接收,并将接收到的数据送入数据处理模块进行相乘、累加等数据运算,最终求出幅值和相位并进行输出。

图2 数字式锁定放大器系统框图

■ 2.2 分频模块设计

在FPGA开发中,时钟设计是时序电路非常重要的一部分。在本设计中FPGA芯片所使用的时钟是由外部晶振提供的50MHz的时钟。分频模块先调用PLL的IP核分出一个32MHz的主时钟,该时钟主要是用于后续数据处理模块的乘法、开方和反三角函数的计算。同时该时钟还可以很方便的通过计数的方式进行分频,产生用于控制DDS芯片的2MHz时钟和用于A/D转换芯片采样的320kHz的时钟。该设计共使用了4种频率的同步时钟,并不存在跨时钟域数据传输,整体时钟结构比较简单。

■ 2.3 数据采集控制模块设计

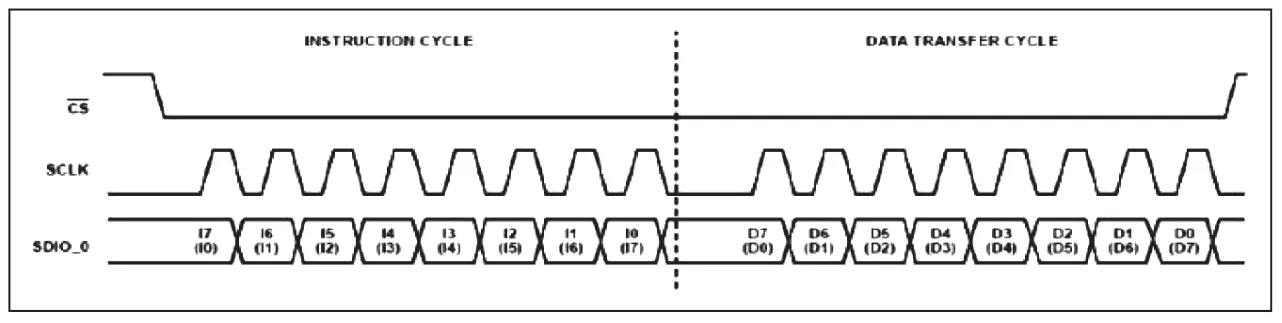

数据采集模块的功能主要是通过SPI协议与ADS8320进行通信,由分频模块为ADS8320提供320kHz的采样时钟,每25个时钟将CS管脚(片选)拉低21个时钟。在CS刚被拉低的前5个时钟,DOUT处于高阻态,随后输出一个时钟周期的低电平信号作为输出转换结果开始的标志,接下来的16个时钟由高到低的输出16位的转化结果。之后将CS端拉高,停止转换。AD转换器通过SPI协议输出的数据由移位寄存器接收并进行串并转换。控制时序如图3所示。

图3 ADS8320控制时序图

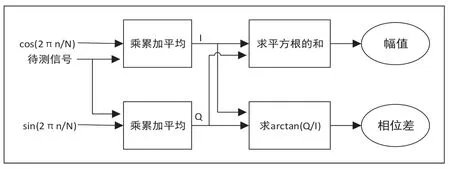

得到的数据送入数据处理模块,实现幅值和相位的检波运算。整体的数据采集控制模块采用状态机进行设计。状态机有idle、start、receive、stop四个状态,通过计数器控制状态的转移,在idle状态发现片选信号有效时,进入start状态,将计数器清零。计数器计数5个时钟后进入receive状态,开始接收数据。数据接收完成,计数器计数到21,进入stop状态,停止采集数据,将片选信号撤销。计数到25后重新开始一轮数据采集。状态转移图如图4所示。

图4 数据采集模块状态转移图

■ 2.4 DDS控制模块设计

DDS控制模块的功能是通过SPI协议对DDS芯片的片内寄存器进行配置,从而实现指定频率正弦波的产生。AD9958内部拥有10个寄存器,分别对应着不同的地址,这些寄存器为:通道选择寄存器CSR、线性扫描斜率LSRR、LSR上升增量RDW和LSR下降增量FDW、功能寄存器FR1和FR2、通道寄存器CFR、通道频率调整字CFTW0、通道相位偏移字CPOW0、幅度控制字ACR[4]。本模块采用单bit串行模式进行数据写入,实现对AD9958片内寄存器的配置。控制时序图如图5所示。每次传输16bit的数据,其中前8bit是指令周期,其中I7决定数据的读写模式,I0-I4是寄存器的地址,后8bit是寄存器中的数据。

图5 AD9958串行写入时序图

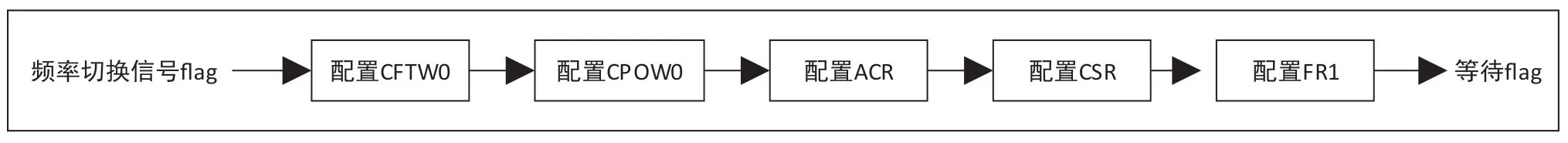

DDS控制模块通过控制CFTW0可以设置通道的频率参数,控制ACR可以对输出信号的电压幅度参数进行设置,控制CPOW0设置相位偏移参数,相位偏移字有14位精度可以调节,分辨率为控制CSR设置SPI的指令控制的具体通道是哪个,控制FR1设置PLL的分频系数和VCO增益等等。每次进行频率的切换都需要对这些寄存器重新进行配置。DDS控制模块流程如图6所示。

图6 DDS控制模块工作流程

■ 2.5 数据处理模块设计

数据处理模块主要是对采集到的数字信号进行计算,首先从数据采集模块的移位寄存器中将同步采集到的两组数据读到乘法器的输入寄存器中,对其进行相乘后送入累加寄存器进行累加。当每个正弦信号的64个采样点的数据相乘累加结束后,通过截位进行平均操作,将低6位的数据直接舍弃,这样做虽然会丧失一点精度,但是避免了使用除法器,节省了运算时间和逻辑资源。截位得到的数据就是数字相敏检波算法中的同向分量I和正交分量Q。然后计算对应的就得到了待测信号的幅值和相位。数据处理流程图如图7所示。

图7 数据处理流程图

数据处理模块所涉及到的乘法器、开平方根和反三角函数登运算,都是通过调用ise工具提供的IP核实现的,在进行FPGA开发的时候,调用成熟的IP核可以大大缩短程序开发的时间,同时还可以获得更好的性能。

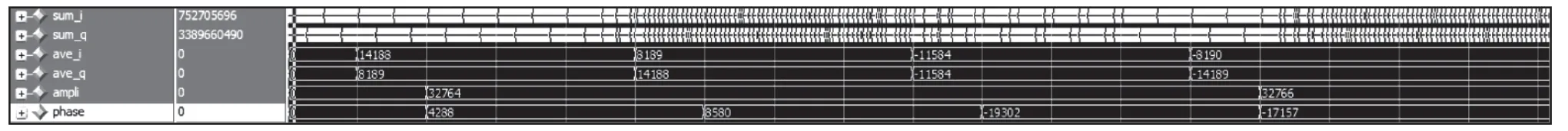

为了对基于FPGA实现的数字相敏检波模块进行仿真分析,我编写一个DDS模块,用来生成频率为200Hz的正弦信号,输出的结果加上随机噪声来模拟待测信号,同时生成两路正交的余弦信号作为参考信号,送入数据处理模块,改变待测信号的幅值和相位参数,观察输出的结果与设置参数的区别,仿真的截图如图8所示,最终仿真数据如表1所示。

图8 数字相敏检波时序仿真图

表1 仿真数据

3 结语

本文设计了一款基于FPGA的数字式锁定放大器,该系统能够实现对200Hz的低频信号进行检波,由于A/D转换芯片采样率的限制,可以通过改变DDS控制模块的程序参数实现最高约100kHz的信号幅相检测。通过对FPGA程序进行仿真发现数字相敏检波算法可以达到预期目标,相信FPGA在微弱信号检测领域会发挥越来越大的作用。