微波组件幅相特性影响因素分析

肖 晖,脱英英,吕英飞,罗建强

(中国电子科技集团公司第二十九研究所,成都 610036)

1 引言

在雷达、通信、导航等应用领域,用于信号接收和发射的收发(T/R)组件是阵列天线和相控阵雷达中的核心组成部分,其性能决定着整个系统的性能。但是,对于批量生产的微波组件,因原材料的批次差异或生产厂家的不同,电路基板的材料参数(例如介电常数、损耗角正切值、金属表面粗糙度等)存在差异;因微组装设备的不同或操作人员的差异,微组装工艺参数(例如级联金丝弧高、级联金丝跨距)存在波动。这导致不同组件或同一组件不同通道之间的信号幅度和相位出现不同程度的偏差,使得微波组件的幅相一致性不达标,最终影响系统的性能。

为将微波组件的幅相特性控制在设计范围内,减少后续组件调试和装配校准的工作量,需要研究电路基板材料参数和微组装工艺参数对组件幅相特性的影响,明确影响微波组件幅相特性的主要因素。本文以T/R 组件中常用的移相模块为例,采用三维电磁仿真软件HFSS18.0 对移相模块进行建模仿真,分析电路基板的介电常数、损耗角正切值、信号传输线表面粗糙度、级联金丝弧高和跨距等因素对微波组件幅相特性的影响,并根据分析结果提出基板选材和微波组件装配过程中的注意事项,从而为微波组件的幅相一致性提供保障。

2 仿真建模

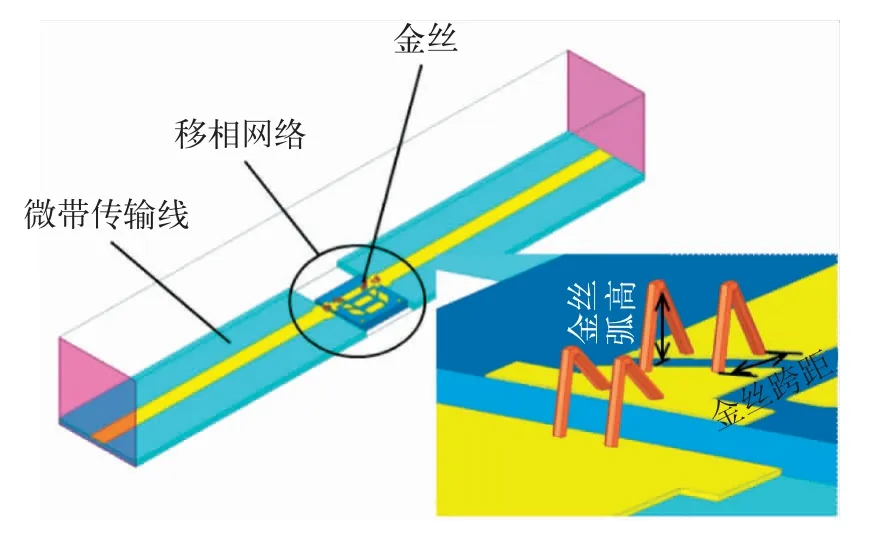

采用三维电磁仿真软件HFSS18.0 对移相模块进行建模,微带线结构移相网络见图1 中圆圈内所示的深蓝色电路片,将移相网络直通路径的各部分以及移相网络和微带传输线通过键合金丝级联得到移相模块,级联金丝结构见图1 的内插图。微带传输线的基板材料为0.19 mm 厚的Duriod5880,基板介电常数为2.2,损耗角正切值为0.0009,信号传输线是厚度为0.015 mm 的铜,表面粗糙度为0 mm;移相网络的基板材料为0.254 mm 厚的氧化铝陶瓷,基板介电常数为9.8,损耗角正切值为0.0001,信号传输线是厚度为0.004 mm 的金,级联金丝直径为0.025 mm,金丝弧高为0.10 mm,金丝跨距为0.20 mm,仿真频段为1~40 GHz。相位滞后仿真结果为负值,相位超前仿真结果为正值。

图1 移相模块仿真模型

3 仿真分析

因原料的差异或制备工艺的不同,微波组件中起互连、支撑、绝缘作用的电路基板材料参数(例如介电常数、损耗角正切值和金属表面粗糙度)存在批次性差异。受器件加工偏差、腔体加工偏差、装配定位偏差等因素的影响,微组装工艺参数(例如级联金丝弧高和跨距)的波动范围较大。为分析每一个参数对组件幅度和相位的影响大小,明确主要影响因素,下面分别将每一个基板材料参数和微组装工艺参数设为仿真变量,仿真分析当其他参数保持不变、单个参数变化时组件幅相特性的变化情况。

3.1 电路基板材料参数仿真

3.1.1 基板介电常数

电路基板的损耗角正切值、金属表面粗糙度、级联金丝弧高和跨距取仿真模型中的设定值,仅将基板材料的介电常数εr设为仿真变量,仿真分析εr的变化对组件幅相特性的影响。εr的初始值为2.2,变化范围为2.0~2.5,步进为0.1。

基板介电常数变化时,移相模块相位φ、通道损耗S21和电压驻波比(VSWR,记作RVSW)的仿真曲线见图2。以εr取初始值时的相位为基准进行比较,对比介电常数取不同值时通道的相位变化,从图2(a)中可以看到,1~40 GHz、不同介电常数下的通道相位随着频率增加而近似单调变化,同一频率下随着介电常数的增加,相位由超前变为滞后,相位变化范围为48.89°~-72.14°@40 GHz。同时,如图2(b)所示,通道损耗和电压驻波比随着介电常数的变化而小幅波动,全频段内,S21的最差值变化范围为-0.33~-0.37 dB,RVSW的最差值变化范围为1.19~1.31。

仿真结果表明,通道损耗和驻波受介电常数变化的影响较小,而通道相位对基板介电常数的变化比较敏感。因此,为保证微波组件的相位一致性,在微波电路的制备初期就要对基板材料的介电常数进行检测 和筛选,严格控制基板介电常数的一致性。

图2 基板εr 变化时,移相模块的φ、S21 和RVSW 仿真曲线

3.1.2 基板损耗角正切值

电路基板的介电常数、金属表面粗糙度、级联金丝弧高和跨距取仿真模型中的设定值,仅将基板介质材料的损耗角正切值tan δ 设为仿真变量,仿真分析tan δ 的变化对组件幅相特性的影响。tan δ 的初始值为0.0009,变化范围为0.0005~0.0025,步进为0.0004。

基板损耗角正切值变化时,移相模块相位、通道损耗和电压驻波比的仿真曲线见图3。以tan δ 取初始值时的相位为基准进行比较,对比通道相位随基材损耗角正切值的变化情况,从图3(a)中可以看到,1~40 GHz、不同损耗角正切值下的通道相位随着频率增加而近似单调变化,而同一频率下通道相位随着损耗角正切值的变化波动极小且无规律,相位变化范围为-0.31°~1.79°@40 GHz。同时,如图3(b)所示,通道损耗随着损耗角正切值的增加而增加,全频段内,S21的最差值变化范围为-0.30~-0.44 dB,通道电压驻波比随着损耗角正切值的增加基本不变,RVSW的最差值变化范围为1.12~1.18。

仿真结果表明,基板损耗角正切值变化对移相模块的相位和驻波的影响均极小,可以忽略,而通道损耗随着损耗角正切值的增加而增加。因此,为降低通道损耗、提高通道增益,微波电路应选择损耗角正切值较小的基板材料。

图3 基板tan δ 变化时,移相模块的φ、S21 和RVSW 仿真曲线

3.1.3 金属表面粗糙度

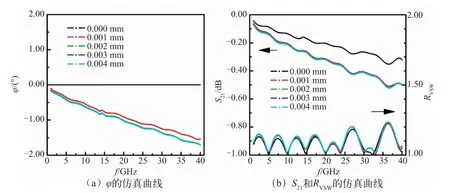

因趋肤效应,电路中微波信号沿传输线表面传输,如果金属表面粗糙度变化较大,组件微波传输性能将受到影响。因此,将金属传输线表面均方根粗糙度Ra设为仿真变量,仿真分析仅Ra变化时组件幅相特性的变化。Ra的初始值为0.000 mm,变化范围为0.000~0.004 mm,步进为0.001 mm。

金属表面粗糙度变化时移相模块相位、通道损耗和电压驻波比的仿真曲线见图4。以Ra取初始值时的相位为基准进行比较,对比分析金属表面粗糙度不同时通道的相位值,从图4(a)中可以看到,1~40 GHz、不同粗糙度下通道相位随着频率的增加而近似单调变化,同一频率下随着粗糙度的增加,通道相位几乎不变,相位变化范围为0.00°~-1.70°@40 GHz。同时,如图4(b)所示,通道损耗和电压驻波比随着金属表面粗糙度的变化而波动,全频段内,S21的最差值变化范围为-0.35~-0.52dB,RVSW的最差值变化范围为1.22~1.23。

仿真结果表明,传输线表面粗糙度的变化对通道相位和电压驻波比的影响极小,而通道损耗随着粗糙度的增加而明显增加。同时随着频率的升高,趋肤深度减小,当趋肤深度小于Ra后,通道损耗将基本不再受Ra变化的影响。因此,微波组件制备时需要减小金属传输线的表面粗糙度以降低微波信号的传输损耗,进而保证微波组件的幅度一致性。

图4 Ra 变化时,移相模块的φ、S21 和RVSW 仿真曲线

3.2 微组装工艺参数仿真

本节将级联金丝弧高和跨距分别设为仿真变量,仿真分析各工艺参数变化对组件幅相特性的影响。移相模块的直通路径上共有4 处级联金丝,每一处的级联金丝根数为2 根,金丝弧高和跨距变化时,4 处的参数同时变化。

3.2.1 级联金丝弧高

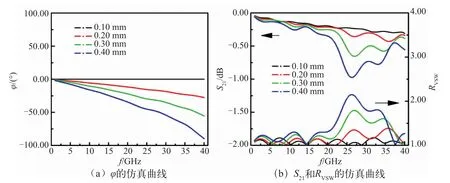

电路基板的介电常数、损耗角正切值、金属表面粗糙度、级联金丝跨距取仿真模型中的设定值,将级联金丝弧高h 设为仿真变量,仿真分析h 变化对组件幅相特性的影响。h 的初始值为0.10 mm,变化范围为0.10~0.40 mm,步进为0.10 mm。

级联金丝弧高变化时移相模块相位、通道损耗和电压驻波比的仿真曲线如图5 所示,以金丝弧高取初始值时的相位为基准进行比较,对比不同金丝弧高下通道的相位值,从图5(a)中可以看到,1~40 GHz、不同金丝弧高下的通道相位随着频率增加而近似单调变化,同一频率下随着金丝弧高的增加,通道相位逐渐滞后,变化范围为0.00°~-89.72°@40 GHz。同时,如图5(b)所示,通道损耗和电压驻波比随着金丝弧高的增加而恶化,全频段内,S21的最差值变化范围为-0.31~-0.97 dB,RVSW的最差值变化范围为1.17~2.15。

图5 h 变化时,移相模块的φ、S21 和RVSW 仿真曲线

仿真结果表明,金丝弧高变化会对移相模块的幅相特性产生较大的影响。金丝弧高增加,模块的幅相特性变差。因此,在微波组件的装配过程中,应注意保持级联金丝弧高的一致性。同时金丝弧高不宜过高,一般情况下应低于0.20 mm。

3.2.2 级联金丝跨距

将移相模块中的级联金丝跨距d 设为仿真变量,仿真分析仅d 变化时通道幅相特性的变化。d 的初始值为0.20 mm,变化范围为0.15~0.35 mm,步进为0.05 mm。

级联金丝跨距变化时移相模块相位、通道损耗和电压驻波比的仿真曲线如图6 所示,以金丝跨距取初始值时的相位为基准进行比较,对比不同金丝跨距下通道的相位值,从图6(a)中可以看到,1~40 GHz、不同金丝跨距下的通道相位随着频率增加而近似单调变化,同一频率下随着金丝跨距的增加,通道相位由超前变为滞后,变化范围为7.26°~-26.76°@40 GHz。同时,如图6(b)所示,通道损耗和电压驻波比随着金丝跨距的增加而小幅恶化,全频段内,S21的最差值变化范围为-0.31~-0.44 dB,RVSW的最差值变化范围为1.14~1.38。

仿真结果表明,金丝跨距对通道损耗和电压驻波比的影响相对较小,而对通道相位的影响较大。因此,在微波组件的装配中,应保持级联金丝跨距的一致性。同时金丝跨距不宜过长,一般情况下应小于0.30 mm。

图6 d 变化时,移相模块的φ、S21 和RVSW 仿真曲线

4 结论

本文以微波电路中常用的移相模块为例,仿真分析了电路基板的介电常数、损耗角正切值、金属表面粗糙度、级联金丝弧高和跨距等因素对组件幅相特性的影响。组件相位对基板介电常数的变化比较敏感,通道损耗随着介质损耗角正切值和金属表面粗糙度的增加而增加,级联金丝弧高和跨距对组件幅度和相位的影响较大。为提高微波组件的幅相特性,在电路基板制备前应对基板的介电常数和金属表面粗糙度进行一致性检测筛选,在组件装配过程中需要保持金丝弧高和跨距的一致性,并且级联金丝的弧高应小于0.20 mm,金丝跨距应小于0.30 mm。

以上仿真模型及结果可用于组件精细化仿真设计、智能工艺方案及制造文件自动生成,从而实现设计制造高效协同,提高微波组件的性能,并减少组件后续调试工作量,提高组件的一次设计成功率。