基于USB的高速串口的设计与实现

杨兆龙 苏兆兆 李瑞祥

(晋中信息学院 山西省晋中市 030800)

在工业领域,仍然有很多设备使用串口来通信。但是,速率较高的场景,诸如数据采集、等,常常采用USB、以太网等方式进行数据传输,而此类接口不论是硬件设计、软件设计,都非常复杂,其工作量都极大。而串口设计简单,只有收发两组线,其通信协议更是容易实现,还具备单比特检错能力,可以在较高速率的使用场景替代其他复杂的板间总线。同时,市场上常见的RS-485/422 收发器,如MAX22507E/MAX22508E,其最高速率可达50Mbps,而市场上能够买到的串口通信模块,最高仅能够达到12Mbps,并没有能够将收发器的性能全部发挥出来。所以,为串口这种使用简单方便的接口提升速率,扩展其使用场景,发挥收发器的潜能,非常必要。

1 总体设计

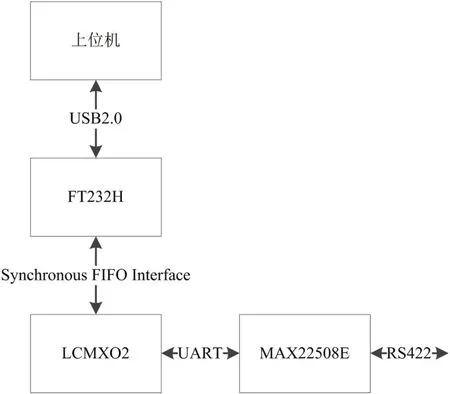

市场上常用的芯片串口最高支持的波特率为12Mbps,没有更高速率的解决方案,故本系统采用FPGA+USB2.0 芯片的方案来实现串口。其结构框图如图1 所示。本系统采用MAX22508E 实现RS-422 与UART 协议的电平转换,采用FT232H 单通道USB2.0-UART/FIFO 芯片将USB2.0 转换为同步FIFO 接口,采用LCMXO2 FPGA 实现UART 接口,并将收发数据通过同步FIFO 接口与FT232H 相连。

图1:系统总体设计

MAX22508E 是一款全双工的RS422 收发器,其最高速率支持50Mbps。可应用于现场总线、工业控制等场景。本设计最高速率为40Mbps,在其支持范围内。

FT232H 是一款功能非常强大的协议转换芯片,其可实现USB2.0 与UART、IIC、SPI、FIFO 接口等协议的转换。其驱动可支持从Windows XP 到Windows 10的所有版本系统,同时支持Mac OS 和Linux,具有很好的兼容性。

基于成本考虑,本系统FPGA 采用Lattice 的LCMXO2-640。该FPGA 具备小规模、低成本、低功耗、单一供电电压3.3V、内嵌flash 和时钟的特点,可以极大地简化设计电路,降低电路板的复杂程度。

上位机采用C#编写,通过调用FT232H 提供的接口函数,完成FT232H 的配置、FPGA 的配置、以及数据的收发。

2 FPGA设计

本设计采用的FPGA 具有640 个LUT,18kbit 的sram,1 个锁相环,40 个通用引脚,最大工作频率133MHz,能够满足本系统的需求。本设计采用外部晶振,工作频率为120MHz。

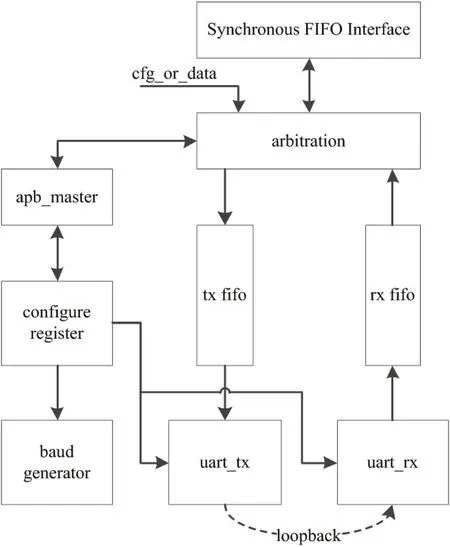

FPGA 总体结构如图2 所示,共分三部分介绍。

图2:FPGA 总体结构

2.1 同步FIFO接口

由于实现的串口收发的最高速率均是40Mbps,所以FT232H 与FPGA 之间的通信带宽应大于80Mbps,为了实现该通信带宽,二者之间通信采用同步FIFO 接口,其为8 位的同步并行口,在辅以控制信号,其时钟频率为60MHz,能够实现最大480Mbps 的通信速率。

读过程:CLK 为时钟信号,由FT232H 输出。RXF 为代表FT232H 中发送缓存的非空信号,低电平有效,由FT232H 输出。当RXF 信号由高拉低时,代表FT232H 中发送缓存中有数据可以读,而RXF 信号由高拉低时,代表FT232H 中发送缓存变空,没有数据可以被读。OE 为输出使能信号,由FPGA 输出,低电平有效。RD 为读使能信号,由FPGA 输出,低电平有效。当FPGA 收到RXF 拉低后,若FPGA 中的发送缓存也非满,则拉低OE 信号,然后拉低RD 信号,开始由FT232H 向FPGA 传输数据;若FT232H 中发送缓存非空和FPGA 中的发送缓存也非满有一条不满足时,则停止传输。

写过程:TXE 代表FT232H 中接收缓存的非满信号,低电平有效,有FT232H 输出。当TXE 由高拉低时,代表FT232H 的接收缓存中可以写入数据,而当TXE由低拉高时,代表FT232H 的接收缓存不能够再写入数据。WR 为写使能信号,由FPGA 输出,低电平有效。当FPGA 收到TXE 拉低后,若此时FPGA 中的接收缓存也非空,则拉低WR 信号,开始由FPGA 向FT232H传输数据;若FT232H 的接收缓存非满和FPGA 的接收缓存非空有一条不满足时,则停止传输。

为了保证收发两个方向的带宽均衡,设定最大突发为16 字节。当读了16 字节或者缓存不满足要求,必须切换到写过程;当写了16 字节或者缓存不满足写的要求,必须切换到读过程。

管脚cfg_or_data 切换当前是进行配置或是数据传输。默认状态为低电平,当其为高电平并且收到特殊的帧格式时,为FPGA 寄存器的配置。配置帧为6 字节,包括4 字节的帧定位和两个字节的配置数据,其格式为:0xF00FF00F+baud_rate+mode。FPGA 收到配置帧后,将baud_rate 和mode 写入到对应的寄存器中。

2.2 串口

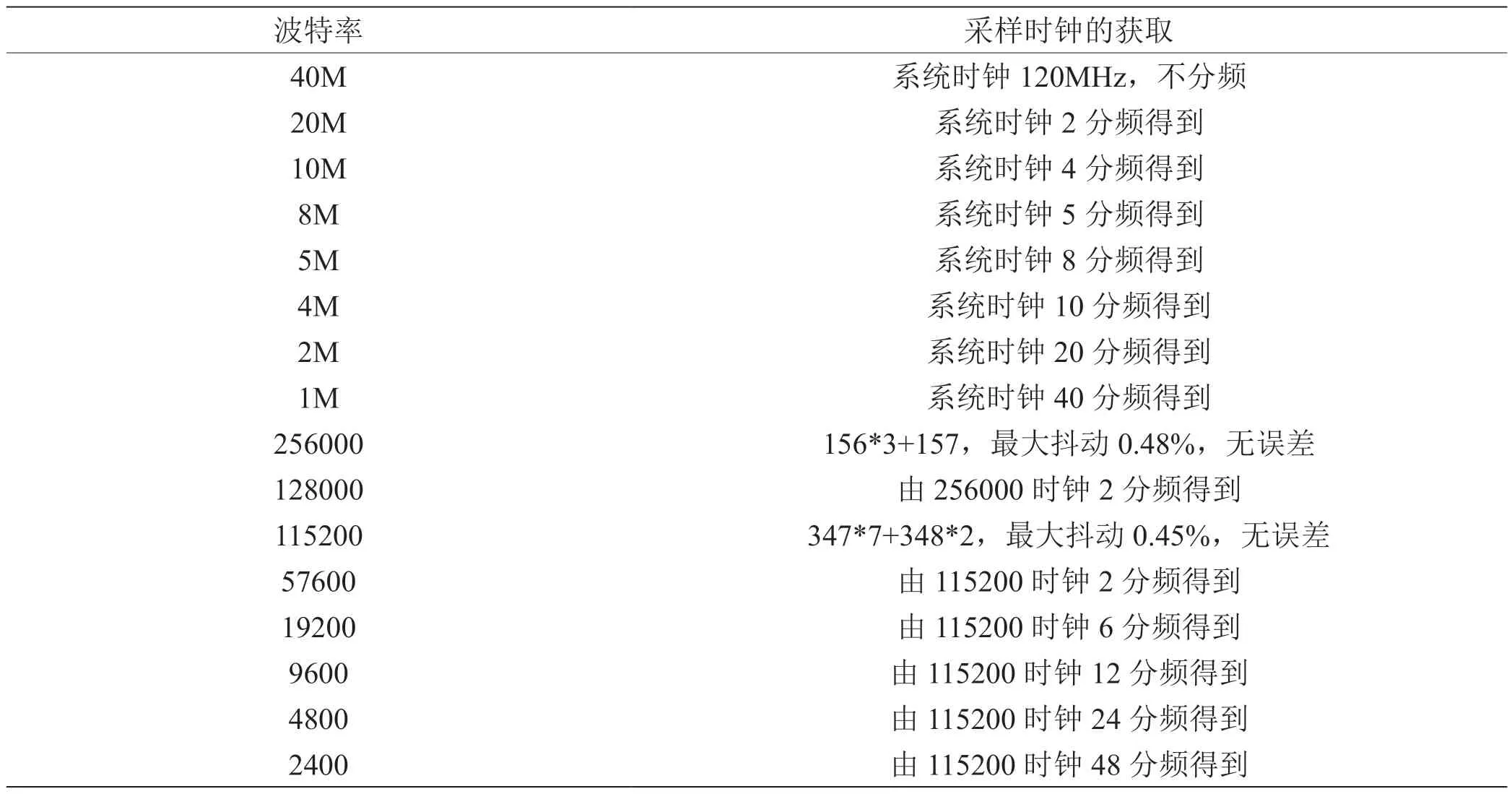

为了保证串口接收的正确率,应保证采样时钟远高于当前波特率,而太高的采样时钟,则对FPGA 的新能提出了更高的要求。为了在保证正确率的前提下控制成本,本设计采用三倍于波特率的时钟进行采样。

FPGA 的系统时钟为120MHz,在一些波特率下,能够经过分频正好得到三倍于波特率的时钟(在接收侧为与波特率相等的时钟,下同)。而在一些波特率下,无法得到三倍于波特率的时钟。这时,不得不采用小数分频。比如:当工作波特率是256000bps 时,其采样频率为768000Hz,其分频比为156.25,在本设计中,采用3 个156 分频加1 个157 分频来达到156.25 分频,会在小范围内带来一点抖动,但是该抖动不会累加产生频偏,保证了波特率的精度。表1 为采样时钟的分频比例:

表1:时钟分频比

当发送数据时,从发送缓存中读取数据,然后按照mode 寄存器中的配置,组好每次发送的数据,如发送数据为0x33,而mode 配置为0x10 时,那么发送数据帧根据配置,取0x33 的第5bits,即0b1001,需要增加1 位的起始位0,增加1 位的停止位1,其奇偶校验为奇校验,结果为1,所以最终发送的数据帧为0b01001111,然后将该数据帧按照发送时钟一位一位地发送出去。

接收数据,这是本设计的重点,也是容易出错的地方。以接收数据的上升沿和下降沿为依据,将cnt 信号清0,那么下一个周期的信号一定是正确的采样点,即cnt 为1 的位置采样。因为本设计为3 倍采样频率,所以采用0、1、2 三个数循环计数,在所有cnt 为1 的位置进行采样。而在上升沿和下降沿都将cnt 清零,也能保证积累的波特率误差不会造成大面积的误码。这时接收到的数据变成了比特流,需要对其进行帧定位。依据数据位宽、有无奇偶校验位可得到数据位宽,然后根据起始位为低电平,停止位为高电平,判断出帧边界。该方法不仅可用于间断数据,还可以用于大带宽下的连续数据。

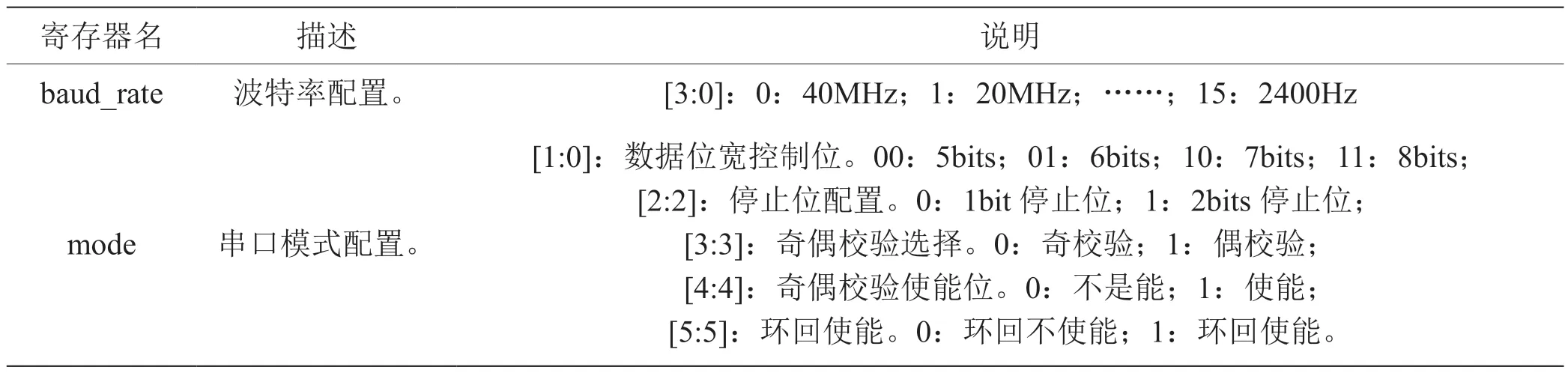

2.3 寄存器

本设计有两个配置寄存器,分别是baud_rate 和mode。寄存器baud_rate,共8bits,低4bits 有效,0-15分别代表表1 中提到的16 种速率。寄存器mode 用来配置串口工作模式,共8bits,低5bits 有效,其中,[1:0]用来控制发送数据的位宽,用来适配数据不是整字节的使用场景;[2:2]用来配置停止位的宽度,配置为0 代表停止位为1bit,配置为1 代表停止位为2bits;[3:3]用来配置奇校验还是偶校验,配置为0 代表奇校验,配置为1 代表偶校验;[4:4]用来配置是否使能奇偶校验,0 代表不使能,1 代表使能;[5:5]为测试功能,在串口处的换回使能,0 代表环回不开启,1 代表环回开启。以上这些配置使得本系统的可用性更好,扩大了本系统的使用范围。寄存器说明如表2 所示。

表2:寄存器说明

3 上位机设计

安装FT232H 驱动后,上位机调用驱动提供的接口函数来配置、控制FT232H,以及接收发送数据。

上位机需要具备使用简单、与各个不同版本的windows 系统都具有较好的兼容性的特点。所以本上位机采用C#为上位机的设计语言,在上位机的布局和功能构成上参考通用的串口工具。具备波特率、奇偶校验、停止位、数据位宽的配置。

固件配置:利用官方提供的EEPROM 配置软件,配置本系统独有的VID 及PID,将FT232H 配置为“245 FIFO 模式”,实现同步FIFO 接口;同时,配置31 号管脚为通用IO,用于实现cfg_or_data 的控制。

初始化:首先效用FT_Open 函数,打开设备。然后调用函数FT_SetLatencyTimer,配置延迟时间,当接收缓存的超时后,用来冲刷到所有剩余的数据,可配置为2ms 到255ms,本系统配置为16ms。调用函数FT_SetUSBParameters,配置USB 的缓冲大小,该值只能配置为64Bytes 的整数倍,本系统采用默认值4Kbytes。

串口配置:开启软件后,通过函数FT_GetVIDPID获取器件的VID 及PID,确认是本系统,当串口关闭时,上位机调用FT_SetBit 函数,将31 号管脚配置为高电平,即配置没事,每修改一次配置(包括波特率、停止位、奇偶校验、数据位宽),上位机都会向FPGA 发送一个配置帧,将当前上位机的配置同步给FPGA。

数据传输:当串口打开时,串口的配置将不能再修改。此时上位机调用FT_ResetBit 函数,将31 号管脚配置为低电平,也就是传输模式,此时,点击发送,上位机就会读取发送数据文本框中的数据,然后进行数据类型转换,并调用FT_GetStatus 函数,查看发送缓存的剩余空间,按照甚于空间的大小,调用FT_Write 函数,将该数据发送出去。上位机创建一个监听进程,每隔100ms,上位机会调用FT_GetStatus 函数,读取接收缓存的字节数,当接收缓存的字节数非0 时,调用函数FT_Read,读取接收数据,并将读回的数据进行格式转换,转换为十六进制,并显示再接收数据文本框中。

4 测试

误码率测试。测试环境:40MHz 波特率,收发器端双绞线环回,发送1MByte 文件,接收完成后,对比接收文件和发送文件,得到误码率。经过测试,在40MHz 波特率下,误码率0%。

5 总结

本设计完成了一个基于USB 的高速串口,系统采用FT232H 芯片作为USB 芯片,实现了USB 与同步并行接口的转换,采用FPGA 实现串口与同步并行接口的相互转换,并且具备串口基本的模式配置,可通过上位机控制串口接收和发送数据。实验证明,该系统可以实现40Mbps 的波特率,发送1MByte 的数据,误码率为0,能够满足如较低速数据采集等场景的使用。

此外,本设计通过设置burst 来提升传输效率的同时,能够均衡收发两个方向的带宽,亦可用于其他设计中。