近似计算新范式在深度学习加速系统中的应用及研究进展

龚 宇 王丽萍 王 佑 刘伟强

(南京航空航天大学电子信息工程学院/集成电路学院 南京 211106)

(空天集成电路与微系统工信部重点实验室 南京 211106)

1 引言

当前,深度学习(Deep Learning, DL),亦称人工神经网络(Artificial Neural Network, ANN),因其在语音/图像/视频分类等多个模式识别领域的成功,已经成为人工智能(Artificial Intelligence,AI)领域重要发展方向。2012年AlexNet[1]以高识别精度获得ImageNet冠军,开启了神经网络又一轮研究高潮。而随着算法的不断演进发展,ANN网络规模从兆字节(MB)已经发展到吉字节(GB)[2–5],海量参数使其计算量巨大,导致传统硬件难以满足网络高能效加速需求[6–8],迫切需要更大算力、更高能效的加速架构。

后摩尔时代,先进工艺制造价格昂贵、门槛高,使得神经网络加速架构能效的优化逐渐从工艺依赖向新型计算范式转型。当前主流新型计算范式有存内/近存计算[9,10]、随机计算[11–13]以及近似计算[14,15]等。存内/近存计算芯片仍面临着生产良率低、工艺难度大的问题,适用于计算位宽和精度较固定的场景;随机计算在高精度处理时硬件复杂度指数增长,且高昂随机性需求使其设计难度大;近似计算对工艺无额外需求且扩展性更强,相比之下更为经济、易于实现。文献[16]对当前模式识别、计算机视觉处理等12类重要应用场景进行了归纳,其中近83%的运算为可容错计算,对其而言,算得“足够好”比算得“非常准”更重要。可见,传统精确计算非当下系统必选项,在很多应用中算得快更为重要,而近似计算正逐渐广泛采用。

当前,国内外学者对于近似计算在深度学习加速系统中的研究集中在近似计算的单元结构设计、系统结构设计、系统设计方法等方向,据公开论文显示,国内主要研究机构集中在部分高校与科研院所,包括南京航空航天大学[17,18]、东南大学[19–21]、电子科技大学[22,23]、上海交通大学[24–26]、清华大学[27,28]、中国科学院计算所[29–31]等。在先进工艺演进代价越来越高、架构设计相对固定化的情况下,近似计算开始广泛应用于深度学习加速系统的多个设计层次中,以进一步提升系统能效。

本文结合目前深度学习加速系统设计的不同层次,从算法层、电路与架构层、系统层对近几年深度学习加速系统中的近似计算方案及设计方法进行了具体介绍,并为后续研究提供思路。

2 近似计算在深度学习算法中的应用

当前,深度学习在模式识别、自动控制及预测估计等领域获得了广泛应用,但是由于模型尺寸越来越大,其硬件实现更加复杂。为了降低深度学习模型的冗余度,近似计算在其模型简化中得到了深入的应用。本节首先介绍典型的3类计算模型,并进一步对其近似量化方案进行介绍。

2.1 典型神经网络模型

2.1.1 卷积神经网络

卷积神经网络(Convolutional Neural Network,CNN)是一种带有卷积结构的前馈神经网络,被广泛应用于具有网格结构的数据,如图像、音频及视频等目标识别领域。卷积层由2维/3维结构滤波器组成,1个滤波器可以看作由多个卷积核堆叠形成。这些滤波器在输入数据上滑动做卷积运算,从输入数据中提取特征。在多层神经网络中,上层节点的输出和下层节点的输入之间通过激活函数建立联系。

2.1.2 循环神经网络

循环神经网络(Recurrent Neural Networks,RNN)是专用于处理序列信息的神经网络,常用于处理序列数据,如长语音识别及长句语义分析等。相比于前馈神经网络,RNN的隐藏层自身也存在一个回路,以允许信息传递到下一步,因此RNN可以接收上一时间点的隐藏状态,由此具有“记忆”。

2.1.3 全连接神经网络

全连接神经网络(Fully Connected Neural Network, FCNN)是一种多层感知机。CNN, RNN,LSTM等深度学习网络都是基于全连接神经网络设计的。在全连接神经网络中,每一层网络的任一个节点都和下一层所有节点连接。其特征提取更为充分,可作用于大多数场景。但因其权重过多,计算量过大导致其单独应用较少,往往作为深度学习网络的最后几层,用于提取和输出分类结果。

2.2 深度学习模型的量化

在深度学习的硬件加速实现高能效方面,量化(Quantization)是最为有效和广泛使用的近似计算方法之一。量化可以大幅减少数据位宽,进而在硬件设计中可以使用更窄的线宽、更少位数的计算单元。

训练后量化算法即在完成神经网络训练后进行量化的算法。文献[32]和文献[33]分别提出了对称量化和(最小/最大)非对称量化算法实现高精度识别。文献[34]提出通过限制激活值范围减少截断误差、通过设置偏差校正修复量化误差,无需重训练保持识别高精度。文献[35]对网络进行逐层量化,以迭代方式动态调整激活值和权值量化步长。文献[36]通过评估不同位宽和数字格式,实现网络压缩率和精度平衡动态量化。

训练中量化算法即将量化过程融入到模型的训练流程中,前向传递时基于量化模型进行推理,而反向训练时仍采用浮点进行[37]。文献[38]提出了一种基于量化边界的训练算法,在每次训练中将小于阈值的数值进行量化操作,在整个网络模型精度损失可控的情况下实现极低位宽的权值和激活值量化。文献[39]表明,权值和激活值小于2 bit时,仍可以实现高精度的神经网络。文献[40]提出名为DoReFa的训练方法,对除第1层和最后一层外的其他所有隐藏层使用极低的数据位宽,同时在反向传播过程中对梯度也进行量化。

二值化/三值化量化:作为更激进的量化方法,极低功耗场景下出现了采用{0, 1}或{+1, –1}表达的神经网络。文献[41]以1 bit权值和激活值的二值神经网络实现了高精度的识别,能效提升超过25倍。文献[42]将CNN权重量化为1 bit,实现了极低计算功耗,同时计算精度损失在2%以内。文献[43]面向语音识别提出了将权重量化为1 bit位宽、数据8 bit位宽的压缩方式,相比16 bit位宽精度损失3%以内。

可以看出,网络量化在算法层面可大幅提高计算速度,对硬件设计有助于减少计算单元的能量、面积开销,减少片上数据传输带宽压力,为设计高能效深度学习加速系统提供了有力支撑。

3 近似计算在深度学习加速电路与架构的应用

近年来神经网络加速系统已经在FPGA, ASIC,GPU等计算架构中有了大量的实现案例,随着多位宽、高能效近似计算应用逐渐广泛,以新型计算范式优化架构成为后摩尔时代提升芯片能效主流方案之一。

3.1 近似加法器与近似乘法器

由于神经网络的规模越来越大,如何优化基础单元的功耗和面积,如加法器、乘法器,以及核心模块,如乘累加单元,成为提升神经网络加速架构能量以及面积效率的关键因素之一。采用合理的近似计算单元,可以在控制系统精度损失的同时,获取较大的能效、面积提升收益。

3.1.1 近似加法器

一般将加法器分为低延迟加法器(Low Latency Approximate Adder, LLAA)和低功耗加法器(Low Power Approximate Adder, LPAA)。LLAA一般是由多个异构的子加法器构成的并行结构,针对实时性和性能要求高的计算场景,常用的有通用精度可配置近似加法器(Generic Accuracy Configurable Adder, GeAr)[44]、面积-质量最佳低延迟近似加法器(Quality-area optimal Low-Latency approximate Adder, QuAd)[45]、容错加法器Ⅰ(Error-Tolerant Adder I, ETA-I)[46]、容错加法器Ⅱ(Error-Tolerant Adder II, ETA-II)[47]、近似镜像加法器(Approximate Mirror Adder, AMA)[48]等等;而LPAA一般则为链式的串行结构,面向功耗极为敏感的场景,如行波进位加法器(Ripple Carry Adder, RCA)、进位保存加法器(Carry Save Adder, CSA)[49,50]、超前进位加法器(Carry-Lookahead Adder, CLA)[51,52]等。

面向深度学习加速,尤其是其中对累加结构的大量应用,出现了大量近似加法结构。或门近似加法器通常用于提高硬件加速器的能效[53–55]。文献[54]将或门近似加法器替代低比特位的全加器,精确计算部分使用与门。文献[48]使用近似镜像加法器替代低位或门加法器,使用更多的晶体管实现系统识别精度提高。文献[56]提出了一种精度自适应近似加法器,其系统在不同信噪比下可根据配置信号使用不同近似位宽。

3.1.2 近似乘法器

传统的标准乘法器往往延迟高、功耗高,难以满足深度学习加速系统的低功耗、高能效要求。而近似乘法器具备了低功耗和低延迟的特点,根据近似产生的阶段不同,一般可分为在生成部分积时近似[57–59]、对部分积求和时近似[54,60,61]和近似对数乘法器[62,63],以下将分别进行介绍。

(1) 生成部分积时近似:文献[57]介绍了两种近似基4 Booth编码器的设计,提出了近似 Booth乘法器。文献[58]通过简化逻辑真值表提出了3种不同的简化方案。与标准乘法器相比,在功耗、延迟和面积方面均有显著降低。文献[59]提出了一种基于近似混合编码的基8 Booth编码近似乘法器。

(2) 对部分积求和时近似:文献[62]提出了一种低功耗乘法器,其中在部分积的求和数组中引入了垂直截断,使乘法器的总功耗降低了58%,但输出精度略有下降。文献[54]引入了水平截断,大大减小了电路面积和功耗。文献[60] 提出通过3个近似累加结构减少部分乘积的行数,但其电路实现相对比较复杂。

(3) 近似对数乘法器:为了提高对数近似乘法器的精度,文献[64]提出了使用截断二进制对数转换器和用于加法的集一加法器的近似对数乘法器。文献[65]中两个连续2次幂之间的输入操作数被分成多段,然后每段分析确定一个误差减少因子,并补偿到基础线性模型的结果。文献[66]通过随机删除精确设计中连接生成近似乘法电路,将多目标笛卡儿遗传规划算法应用于设计空间探索,获得关于MRED的最佳近似电路。

3.2 混合精度的深度学习近似加速系统

基于近似计算的混合精度神经网络处理器已经有了大量的工作发表,对精度的控制方式也出现了多种机制和方案。qcNPE[67]是一款基于近似计算的神经网络加速架构,通过在计算模块中增加精度控制电路进行实时精度重构,并和神经网络的结构相映射以实现高能效。Laika结构[68]在65 nm CMOS工艺下实现了5 μW低功耗永远在线的关键词语音识别芯片,采用了4 bit和8 bit动态切换的近似计算结构,可动态适应网络加速中不同步骤的不同位宽需求。Price等人[69]发表了基于计算宽度可变单元、存储结构可重配置的神经网络芯片,采用动态宽度控制实现不同网络层及不同负载下的资源重配置。

清华大学团队提出的Thinker系列集成了多种混合精度神经网络加速架构[70,71]。Thinker架构[70]中的计算单元可动态配置为不同位宽,重构后加速等不同网络层计算,Thinker-II[71]设计了基于多位宽、可配置加法树实现的位宽可变累加,这一结构可支持1~16 bit不同位宽的累加运算。中国科学院计算所团队设计了多款支持多位宽的智能计算处理器[72,73],实现了多种位宽下高能效加速和计算精度控制。三星公司在其先进SoC设计中集成了神经网络引擎[74],采用INT4/INT8/FP16混合的近似乘法器实现多精度MAC单元设计,实现了极高的能量、面积效率表现。南京航空航天大学和东南大学联合研发的面向语音识别的超低功耗近似计算芯片[43],采用了多种近似加法器、近似乘法器结构,实现了高能效、高精度的关键词语音识别。

4 深度学习中的近似计算协同设计

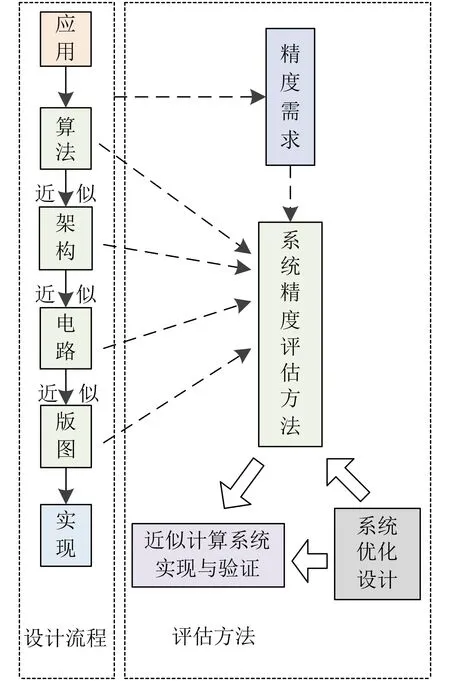

传统IC设计需要在整个设计流程中尽可能保持数值和变量的等价,即要求前一设计层次的计算结果和后一设计层次的计算结果是相同的,以保证最初的应用开发和最终的芯片输出结果一致。对于近似计算而言,其设计原则是只要计算精度满足系统需求,在IC设计的每个流程中都可以适当引入近似计算,如图1所示。近似计算的核心和关键在于,如何在计算精度和硬件能耗间获得一个较好的均衡,在能效提升同时,要确保最终的执行结果偏差在容忍范围内。近似计算以精度换取系统复杂度降低,但随着近似计算单元设计的不断演进和发展,需要跨越算法、电路、架构多个层次进行系统设计。如何建立跨层设计与系统精度的关联规律以完成近似系统精度和系统复杂度之间的设计取舍、如何协同计算-存储模块的设计以面向具体应用场景实现系统级高能效设计,成为近似系统能效提升的关键性问题。为了解决上述问题,针对近似计算的精度建模、精度评估手段不断出现,以提供快速部署的实现方案指导。

图1 近似计算设计流程与评估方法

4.1 单元误差分析与系统误差评估

4.1.1 近似加法器的误差分析

Mazahir等人[75]提出了针对一系列用于近似加法器均衡设计的概率误差模型,以评估LLAA近似加法器的计算精度。这一模型首先将近似加法器按比特拆分,基于进位出错概率建立子近似加法器精度模型,继而推导出整体误差模型。这一模型可以快速、精确地评估多类基于分块结构的近似加法器。 Hanif等人[45]提出了针对低延迟近似加法器精度和复杂度均衡评估的QuAd模型。作为面向设计精度、面积以及延迟均衡的解析表达精度模型,QuAd模型将近似加法器的不同设计参量作为模型变量,可将模型用于LLAA设计空间探索,大大加速了设计初期的参数设置及评估。针对LPAA近似加法器,Ayub等人[76]提出了精度和复杂度均衡的评估方法,通过只考虑正确结果概率进行了模型的压缩和解析简化,大大加速了评估效率。

4.1.2 近似乘法器的误差分析

近似乘法器的精度模型即可看作近似加法器模型的扩展。Zhu等人[77]提出了多分布概率误差模型和评估方法,可高精度预估近似Booth乘法器精度。该工作将近似Booth乘法器的概率误差模型分为编码模块、部分积阵列模块及压缩模块错误概率模型,3个子模型逐层关联,构成最终乘法器精度评估方法。Liu等人[78]提出面向近似计算累加器的精度评估方案,将累加模块作为整体划分计算流水,抽象为多计算阶段的加法器,最终可以在支持向量机算法上实现接近92%的评估精度以及1.5倍的性能提升。此外,面向神经网络算法中最为重要的乘累加和累加模块,当前基于PMF[77]的分析可以在低比特位宽时实现较高的精度预测。

4.1.3 近似计算的系统误差评估

MACACO模型[79]是较为系统的行为级精度评估方法,这一模型基于时序无关的等价电路结构,创新采用了虚拟误差电路,在特定输入数据或数据集下通过布朗分析、SAT分析、BDD分析等多种方式结合,以蒙卡数据拟合模型,实现了行为级精度评估。Venkataramani等人[67]提出了AxNN框架,专用于神经网络加速系统在近似计算系统中加速时精度、能效均衡设计的建模评估。AxNN在设计阶段增加精度可控制的计算单元进行精度调节,提高2.3倍系统性能时仅损失7.5%精度。Liu等人[80]设计了CONCRETE框架用于“算法-架构-电路”逐层地进行神经网络在近似计算系统中的均衡设计及评估,神经网络的结构参数、近似计算单元的位宽参数都纳入精度影响参量,可以评估最终精度,以此优化神经网络设计。Freno等人[81]提出了一套基于机器学习算法的近似计算误差统计模型,通过引入回归分析、随机噪声模型等,参量化并进行定向提取评估近似计算精度,提供优化近似计算系统设计的具体思路。文献[43]面向权重二值化神经网络加速系统,通过近似噪声的概念定义提出了一种系统级误差分析方法,可量化评估算法层、架构层、电路层等不同层次误差的扩散和影响,最终将评估结果用于近似计算的架构设计参数优化。

4.2 深度学习近似加速系统中的设计空间探索

除通用近似计算系统的评估建模,针对神经网络加速架构的设计空间探索也有大量的研究工作展开。面向神经网络的设计空间探索方法主要分为几类:一是朝着更复杂的结构进行探索,如引入近似计算[82–86]、引入新型电路结构[87]、增加存内计算电路[88];二是面向特定的应用范围,简化设计空间,从而提高设计空间探索的效率[83,84,89];三是对设计空间探索的收敛速度、优化算法进行研究[90–92]。面向具有海量计算资源的神经网络加速架构,要对多种不同设计方法进行融合,才能快速、准确、有效地实现设计收敛。

5 思考与展望

当前,在深度学习加速系统中近似计算已经有了广泛的研究和应用,但是其更大规模的应用和部署仍存在较为突出的一些挑战,主要集中在近似计算系统设计中的误差分析与管理、跨层设计与协同优化、近似系统的验证与测试、可靠性与安全性问题。

5.1 误差分析与管理

近似计算以误差为代价换取能效提升,但是系统误差仍是最重要的系统指标之一。由于误差分析必须要考虑具体应用场景,因此一般性的误差分析方法往往集中在小模块上,在系统层仍然缺少普适性的误差分析方法。同时,由于近似计算的设计方案多样,存在确定性误差和非确定性误差两大类。确定性误差可以较容易地确定其边界,而非确定性误差的分析、评估与控制更具有挑战性。

5.2 跨层设计与协同优化

当前,面向近似计算的设计优化多集中在单一的设计层次或设计阶段。而由于误差在系统中是不断传播的,因此,结合多层次的近似计算技术以进行软硬件协同设计,可以更为充分地挖掘近似计算的能效潜力。近似计算在算法层的优化方案如何与电路、架构层的设计有机结合、互相优化,仍需深入研究;同时,将近似计算硬件误差在算法设计中加以考虑、修正,也是提升近似计算系统精度、能效的有效方法。

5.3 近似系统的验证与测试

现有的EDA工具对近似计算系统的验证和测试支持有限,使得近似计算系统的误差范围难以控制在可接受范围之内。充分考虑近似计算的误差来源,重新审视测试向量的生成方法,并对影响误差程度更大的关键电路使用更合适的测试方式,是大幅提升近似系统验证测试效率的重要工具开发方向。

5.4 可靠性与安全性

在面对老化问题时,需要将近似计算引入的额外计算误差纳入系统设计考虑之中。与精确计算不同,近似计算利用了算法、电路、架构的特征,因此电路的可靠性存在着新的设计挑战。此外,安全性也是近似计算面临的重要挑战。由于设计本身引入了计算误差,如何区分硬件/软件木马所引入的误差成为系统的威胁之一。如果将这一技术应用于视频监控、安防、智能电网等业务领域,就必须充分考虑安全防护设计。

6 结束语

本文主要对近似计算在深度学习加速系统不同设计层次的应用进行了总结,包括算法层、电路与架构层和系统层。与传统计算范式相比,近似计算可以在同工艺节点下大幅提高能效,是后摩尔时代最具备潜力的研究方向之一。同时,从误差分析与管理、跨层设计与协同优化、近似系统的验证与测试、可靠性与安全性4个方面进行了思考与展望,以供学者在后续研究中作参考借鉴。另外,近似计算的设计流程目前仍不完整,难以直接产业应用,仍是其成为主流计算范式所面临的重大挑战和重要研究方向。