电源开关噪声耦合干扰高速信号的分析及优化方法研究*

贡 维,李 岩,许泗强,齐红玉

(1.浪潮(山东)计算机科技有限公司,山东 济南 250101;2.浪潮电子信息产业股份有限公司,山东 济南 250101)

1 引言

当今社会,电子信息已经和每个人的生活息息相关,电子产品的发展从摩尔定律提出之后就按照其规律突飞猛进,电子行业的竞争日益激烈,高速电路设计的要求也越来越严格。

在电子系统中,高速电路设计面临的问题,归根结底是噪声的问题。噪声对有用信号产生污染,给高速链路中的信号增加了不确定性,导致出现错误信息。随着系统频率的不断提升、系统电压的不断降低,电源开关噪声问题逐渐成为高速电路噪声问题研究的热点。高速电路系统的运行时刻伴随着电子元件状态的开关,器件的开关引起电流突变,由于系统中存在着众多的寄生电感,电感处产生变化的电压,即电源开关噪声[1]。电源开关噪声对信号完整性SI(Signal Integrity)和电源完整性PI(Power Integrity)都有很大的影响。

很多专家和电路设计工作者也对电源开关噪声开展了专项的研究,但大部分都只是提出一些噪声抑制的模型,着眼于如何在设计之初抑制电源噪声。然而,在实际的高速电路设计生产过程中,由于仿真模型的偏差、设计的不合理、PCB制板的偏差等因素造成的SI和PI问题往往缺乏专业且系统的分析介绍。本文主要着眼于在电源开关噪声对高速信号产生耦合干扰后如何进行分析和优化解决,针对某主板设计过程中存在的电源开关噪声耦合干扰高速信号的案例进行理论分析、测试分析、仿真分析及优化验证,为该类问题提供一个系统的分析解决方案。

2 SI和PI理论介绍

2.1 SI理论

SI代表了电路系统在信号传输时,对信号的时序和电压的保障能力[2]。比较轻的SI问题,可能会使传输数据出现偏差;严重者,会导致系统无法工作,直接瘫痪。SI问题一般是多种因素相互作用的结果,电路中元器件的布局、布线以及IC中晶体管的开关速率都会导致不同程度的SI问题。原因主要可以分为以下3种:信号的时序、系统内部与系统外部的噪声和电磁干扰EMI(ElectroMagnetic Interference)。主要表现为:延迟、反射、同时开关噪声、振荡、地弹和串扰等[3]。在高速电路设计中,电路板的层数、线宽、介质厚度、走线拓扑、互联结构、放置方式和布线时的距离等因素都会对SI有不同程度的影响。

SI仿真结果通常以眼图形式呈现,其中包括传输耦合噪声参数、接收端信号脉冲边沿抖动参数和设计裕量参数等。眼图由周期信号波形重叠组成,通过将“000”“001”“010”等8种码型叠加在同一周期内,得到一个形似眼睛的图像,简称眼图[4]。眼高和眼宽是眼图的2个重要参数,可以表征信号质量的好坏。影响眼高的SI问题有很多,其中最主要的是噪声和损耗。噪声问题使得眼图上下“眼皮”变宽,直接限制眼高;损耗问题[5],尤其是高频损耗,使信号跳变变缓,在高速传输系统中甚至存在跳变未完成就再次进行状态切换的情况,此时就算系统提供再高的工作电压,信号也无法识别。损耗问题相对容易发现和解决,而噪声问题由于其传递路径的隐蔽性和多源性,往往是设计管控的难点。

2.2 PI理论

高速电路的PI以SI为基础,又有所区别。一个理想的电源几乎是没有阻抗的,在这样一个电源平面上所有点的电位都等于电源的电压。而实际上理想的电源是不存在的,电源中不可避免地存在一些噪声干扰,严重的情况下甚至会对系统正常工作造成影响。PI主要是为系统中的所有信号提供一个完整的电流回路[6]。

在高速电路设计中,由于电流不断地从电源流入门电路、从门电路流出到达地平面,在这个过程中,会产生一个瞬态变化的电流,该电流在流经回路电感时会产生电压降,因此产生电源噪声,形成PI问题。

常用的PI的分析方法一般有频域、时域和直流3类[7]。频域分析方法常用于无源、线性和时不变系统的分析,它研究的是系统随频率变化的特性,与激励信号关系不大,常采用网络参数法进行分析;时域分析方法用于定量得到纹波电压,一般通过对芯片、封装、PCB协同仿真得到,IC厂商一般会提供芯片的电流模型,可以通过此模型仿真一段时间内芯片外部管脚的电流特性;直流分析随着电路单板功率和布线密度的提升,显得逐渐重要起来,它主要是分析电源分配网络中的直流压降和通流问题。

2.3 常用仿真工具

在高速电路设计中,仿真分析是加快开发周期、提高设计准确度的重要手段。仿真分析可以在硬件开发之前减少设计错误,节省人力、物力和时间成本,也可以在出现故障后帮助定位问题点。仿真工具各有千秋,工程师选取的时候主要考虑仿真时间、仿真精度等因素。目前,高速电路中常用的仿真软件主要有Cadence、Ansys、ADS(Advanced Design System)等软件,每个软件中有不同组件,针对不同信号和不同标准可以选用不同的组件。

Cadence是用于电子设计自动化EDA(Electronic Design Automation)的软件,其中主要用于电路仿真分析的组件有Sigxp/Sigrity等[8,9]。Ansys是大型通用有限元分析软件,其中主要用于电路仿真分析的组件有HFSS(High Frequency Simulator Structure)/SIwave(Signal Integrity wave)/Q3D Extractor等。ADS同样是一款EDA系统仿真软件,它有着强大的功能、较高的精确度和高速的仿真能力,在高频设计领域也非常受工程师的欢迎,其中主要用于电路仿真分析的组件有SIPro(Signal Integrity Pro)/PIPro(Power Integrity Pro)/Memory Designer。本文仿真所使用的主要是Cadence公司的POWERSI(POWER Signal Integrity)软件及Speed2000[10]。

3 实际案例分析

3.1 案例描述

工程师在进行某主板DDR4识别内存测试RMT(Recognition Memory Test)时,发现有一个内存通道结果显示有异常:N6.C0,这组的RxVLow信号和RxVHigh之间的数值差比较低,显示结果如图1所示,此处的RxDqLeft和RxDqRight之间的数值差指的是信号眼宽参数,RxVLow和RxVHigh之间的数值差指的是眼高参数。一般来讲眼高和眼宽值越大代表信号越好,反之较差。为了定位出对应的DDR4 I/O信号,详细查询图2中的RMT log文件,最终确定出问题的DDR4 I/O信号为DQ(数据I/O信号)0、DQ1、DQ4和DQ5。

Figure 1 RMT results of memory channels

Figure 2 Detailed log file of RMT

在定位出问题信号之后,首先检查主板的原理图设计,确保原理图设计无误后,对该部分信号的SI进行分析。该主板的PCB层叠设计共12层,出现问题的4个信号线均位于第8层,PCB的叠层设计如图3所示。

Figure 3 Design of PCB stack

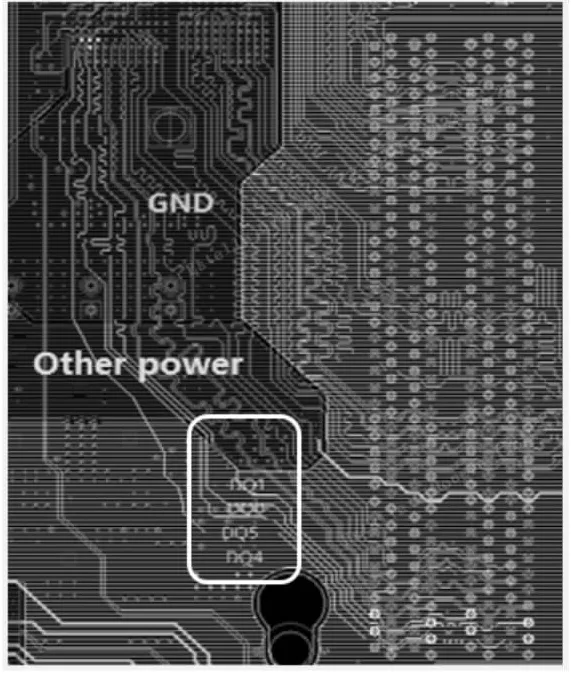

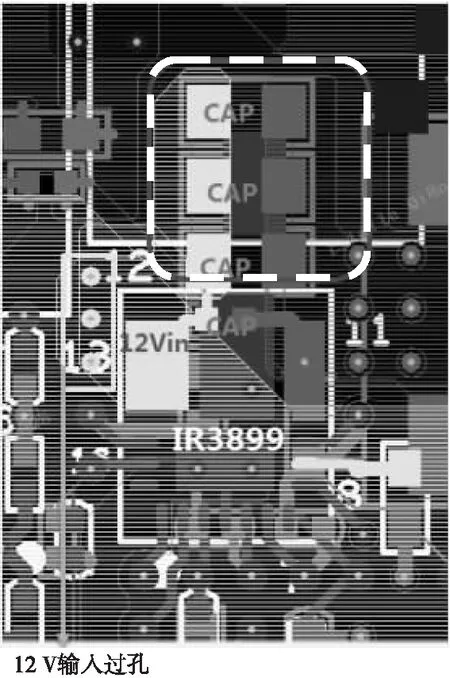

该PCB设计的层叠结构中,第8层信号层的参考层为第9层GND,邻近的第7层为Power层,包含12 V、GND和Other power共3个平面。出现问题的信号线在第8层中的位置如图4所示,白色框内由下到上依次为DQ4、DQ5、DQ0和DQ1。在该4条信号线的布线路径上,DQ4和DQ5之间有3个12 V的过孔,如图5所示。经测量,DQ4和12 V过孔的间距为33 mil,该部分的12 V过孔用于连接第7层的12 V平面和Top层的开关电源芯片IR3899(IR3899-开关电源控制芯片,将12 V转换成芯片所需的低电压)。此电源芯片附近的PCB布线设计如图6所示,该芯片的12 V输入滤波电容位于PCB背面,如图6中虚线框所示,这3个滤波电容距离芯片引脚较远,仅通过3个过孔相连。

Figure 4 Location of the faulty signal line in the 8th layer

Figure 5 Via between DQ4 and DQ5

Figure 6 PCB wiring design near power supply chip

由于出现问题的内存信号临近12 V电源层且临近12 V的3个过孔,因此初步怀疑12 V电源噪声对内存信号产生了干扰,为验证该猜想,对电源芯片IR3899的12 V以及4条DQ信号线进行测试。

3.2 测试分析

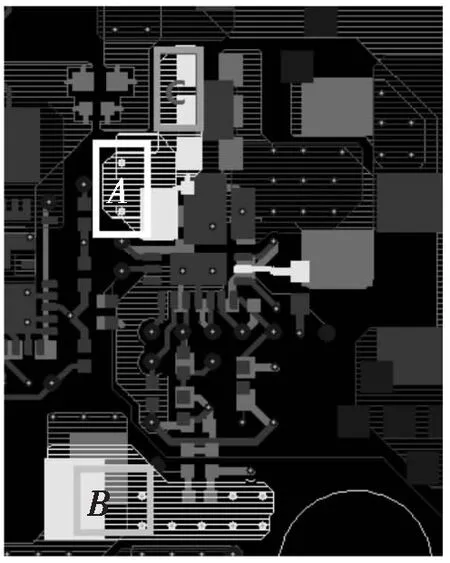

针对电源部分的测试点选择,主要设立了A、B、C3个点,如图7所示,其中A点是12 V输入的一个过孔,由于电源芯片IR3899位于PCB正面,输入滤波电容位于背面,两者通过过孔相连;B点是电源芯片附近的12 V铜箔,由于出现问题的信号与第7层12 V平面相邻,内层铜箔无法直接测量,因此选择表层近距离测量;C点是12 V输入的滤波电容,位于PCB背面。

Figure 7 Schematic diagram of the test points for power supply chip

使用示波器测量上述选取的位置和4条DQ信号线,得到如图8所示的波形图。可以观察到图8a所示的A点波形存在580 kHz左右毛刺,该主板上电源芯片IR3899设计的开关频率正好是580 kHz。图8b所示的B点位置的波形中,振荡的峰-峰值为1 V左右;图3c所示的C点位置的波形中,振荡的峰-峰值只有100 mV左右。因此,判断出12 V输入上的噪声是由电源芯片的开关噪声耦合进去的。

Figure 8 Waveform diagram of point A,point B,point C and 4 DQ signals

观察图8d中4个DQ信号的波形图可以发现,波形图中同样存在574 kHz左右的主噪声,因此怀疑4个DQ信号的报错是由电源芯片IR3899的开关噪声耦合引起的SI问题。

3.3 理论及仿真分析

3.3.1 理论分析

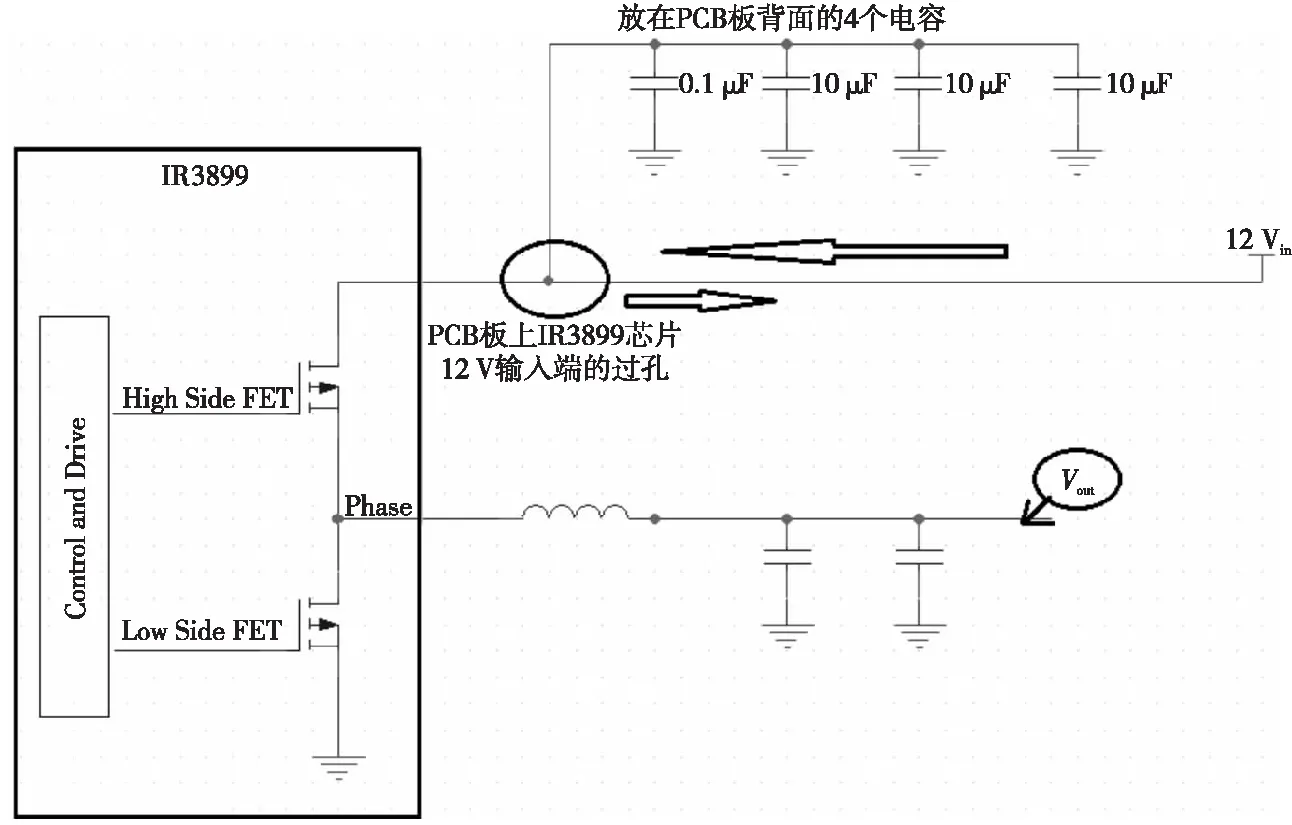

首先针对电源开关噪声对内存DQ信号的耦合路径进行理论分析。由于电源芯片IR3899属于Buck电源(DC/DC降压转化的拓扑结构),该Buck电源的原理示意图如图9所示。在Buck线路的上MOS管开启过程中,因MOS自身的寄生参数、PCB及外围元器件的影响,会在相位(Phase)上产生一定的振荡,振荡产生的过程中,上MOS管在可变电阻区工作,将振荡传输到12 V电源总线上,因此12 V电源总线上产生很强的开关噪声。由于12 V的滤波电容放在背面,仅通过3个过孔相连,相当于12 V输入的路径上没有直接的滤波电容,所以当振荡传输到12 V电源总线上时,该振荡噪声在正面的3个过孔处无法完全滤除。

Figure 9 Schematic diagram of Buck power supply

PCB设计中信号线一般以GND为参考面,有时候参考面也可以是电源,因为直流电源与GND之间有大量电容作为交流连接通路。但是,当参考平面上有较大的噪声电压和电流时,噪声就比较容易耦合到信号线上。同样当距离信号线较近的区域内有电源过孔时,也可影响传输线上的信号传输。在3.1节的PCB布局中已经提到,出现问题的信号线位于第8层,它们邻近的第7层有12 V的铜箔。由于电源芯片端没有滤波电容,滤波电容放置在背面,因此回传的噪声通过过孔下传,在第7层Power互连的铜箔上传播,影响邻层第8层的信号线,从而对内存的DQ信号产生干扰。电源开关噪声通过过孔耦合到电源平面进而耦合到信号线的示意图如图10所示。

Figure 10 Schematic diagram of power switch noise coupling interference high-speed signal

3.3.2 仿真分析

本节对4条内存DQ信号线进行噪声耦合仿真分析。使用Cadence Sigrity Speed2000软件进行时域仿真,首先新建仿真工程,导入待分析的PCB BRD文件,根据实际的叠层信息设置板厚、层数、板材和铜厚等关键参数,依据PCB过孔的实际信息设置焊盘参数,选择需要仿真的DDR 网络和电源网络并设置电源网络电压值,设置阻容件等关键器件模型,在12 V电源输入上添加一个噪声源,导入CPU和DDR IBIS模型,设置信号探针、信号I/O类型、信号Model、信号速率和仿真时长等仿真参数并开始仿真,得到如图11所示的仿真结果。从图11可以看到,DQ0、DQ1、DQ4和DQ5有明显的影响,与RMT的log文件的结果一致。

Figure 11 Simulation results of Cadence Sigrity Speed2000

信号质量受噪声、损耗等多种因素影响,很难对某个单一指标进行量化管控。以业内主流Intel®Whitley平台参考版设计为例,12 V电源噪声对DDR信号的影响约为5 mV,本例中的最大值已超过15 mV,存在潜在风险。从3.3.1节的理论分析可以发现,由于12 V电源输入的直接路径上没有电容,导致电源芯片的开关噪声耦合到了12 V输入上,通过3个过孔传输到第7层的Power平面上,进而影响了第8层的信号质量,因此直接的改善手段就是将12 V电源输入的滤波电容摆放在回流路径上,当噪声传输回12 V时,噪声会被滤波电容滤除,即便存在也是微弱的。

基于上述的改善方案,将电容摆放在输入路径上:即将滤除噪声的电容摆放在PCB正面,直接和电源芯片的12 V输入引脚相连,改善后的PCB布局如图12所示。再次使用Cadence Sigrity Speed2000软件进行时域仿真,得到的仿真结果如图13所示。可以发现,所有内存DQ信号受到的干扰明显减小,可控制在5 mV以内。

Figure 12 PCB layout after improvement

Figure 13 Simulation results after improvement

4 优化验证结果分析

基于上述分析及仿真结果,在该PCB板上进行返工(Rework)验证:在电源芯片IR3899的12 V引脚的过孔处与旁边GND之间增加1片0.1 μF电容(放置于PCB板的正面),并用16 GB内存进行2次RMT,1次通过,1次失败,结果已有所改善;在此基础上再增加一片0.01 μF电容,16 GB和32 GB内存的测试均通过;为了验证测试结果不是偶然的,对Rework后的单板使用16 GB和32 GB内存各测试3次,结果均是Pass。

根据Rework的验证结果,修改PCB设计并重新生产加工,用16 GB/32 GB的满配内存进行RMT,3次全部Pass,N6.C0通道RxVLow信号和RxVHigh信号的裕量结果已有明显改善,如图14所示。由此可以证明,将12 V电源输入的滤波电容摆放在回流路径上的改善手段是有效的。

Figure 14 RMT results after changing PCB board

5 结束语

本文主要针对某主板设计过程中存在的电源开关噪声耦合干扰高速信号的问题进行理论、测试、仿真分析及优化验证,为该类问题提供一个系统的分析解决方案。在检测到信号故障后,可以首先进行原理图和PCB设计分析,利用示波器等测试工具测试相应波形,并利用合适的仿真工具展开故障模拟、故障定位、优化验证仿真等过程,最后对优化方法进行改板验证,验证结果充分表明了本文优化手段的有效性。