基于CPLD的4通道存储测试系统设计

马佰振,原晓洁,范锦彪

(中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

0 引言

存储测试是指在对被测对象无影响或影响在允许范围之内的前提下,通过使用微型数据采集存储记录仪在被测信号处,实时实况完成信息的快速采集与记录,事后通过回收记录仪,由上位机处理和再现测试信息的一种测试技术。存储测试的主要技术特点是现场实时采集记录,事后回收记录仪器,通过处理将被测信息再现。

1 系统总体工作原理

4通道存储测试系统的原理框图如图1所示,4个通道的信号经信号选择器选择后,在CPLD的控制下经信号选择器轮流输入A/D转换器,经A/D转换后存入铁电存储器。系统对4个通道的信号轮流采样,依次存入存储器。CPLD控制着整个系统工作时序、触发通道、触发电平、采样点数等。采样结束后通过读数设备由上位机软件将数据读取到计算机存储、显示和处理。

图1 系统原理框图

2 系统硬件设计

整个系统以CPLD芯片XCR3064为中心控制器进行设计,系统采用LP5996作为电源管理芯片,A/D转换器选用AD7492,存储器选用FM22L16,通道选择器选用MAX4634。系统硬件电路原理图如图2所示。

2.1 电源管理和信号选择器电路设计

本测试系统采用了一款线性低压差电源管理芯片LP5996,其工作状态表如表1所示。

表1 LP5996工作状态表

如图2中所示,电源管理芯片LP5996的电源引脚接电池电压VCC,使能端EN1和EN2分别控制输出VOUT1和VOUT2,用来提供数字电源(VDD)、模拟电源(VEE)。其中EN1由上拉电阻置为“高”,使VDD始终输出3.3V电压,EN2的高低由CPLD控制,进而控制VEE的输出。该芯片在电池电压变化的情况下(3.3~6V之间),也能够输出稳定的3.3V电压,提高了测试系统的稳定性。

图2 硬件原理图

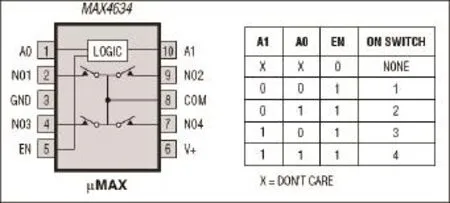

信号选择器选用MAXIM公司的MAX4634芯片, 其引脚定义及真值表如图3所示。NO1~NO4分别连接要采集的四组信号,A0、A1分别接铁电存储器的地址端A0、A1,在CPLD推地址的同时完成对4个通道的信号轮流导通和关断。4个通道的信号经MAX4634芯片轮流进入A/D转换器进行采样。

图3 MAX4634的引脚定义及真值表

2.2 A/D转换模块和存储模块电路设计

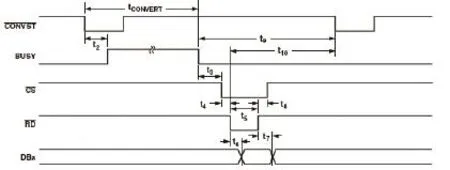

考虑到测试系统精度要求,同时也为了降低整个测试系统的功耗。本测试系统选用AD公司生产的12位A/D转换器AD7492。AD7492具有两种工作模式:高速采样模式和休眠模式。当AD7492工作在高速采样模式下,转换信号CONVST在转换完成时被拉高;当AD7492工作在休眠模式时可以实现低功耗,输入信号是在CONVST转换信号下降沿时开始被采样,经过10ns的保持时间,BUSY信号在转换开始时为高电平,当BUSY信号变为低电平时,数据转换结束。AD7492的工作时序如图4所示。

图4 AD7492的工作时序图

为了提高存储测试系统在高温、高压、高过载等恶劣环境下的可靠性,防止由于系统掉电引起的数据丢失,本测试系统采用Ramtron公司的基于FRAM技术的FM22L16芯片。 FM22L16与CPLD和A/D转换器的接口电路如图2所示,本测试系统用到AD7492为12位,故将FM22L16的D12~D15接地,D0~D11分别接AD7492的D0~D11。

3 软件设计

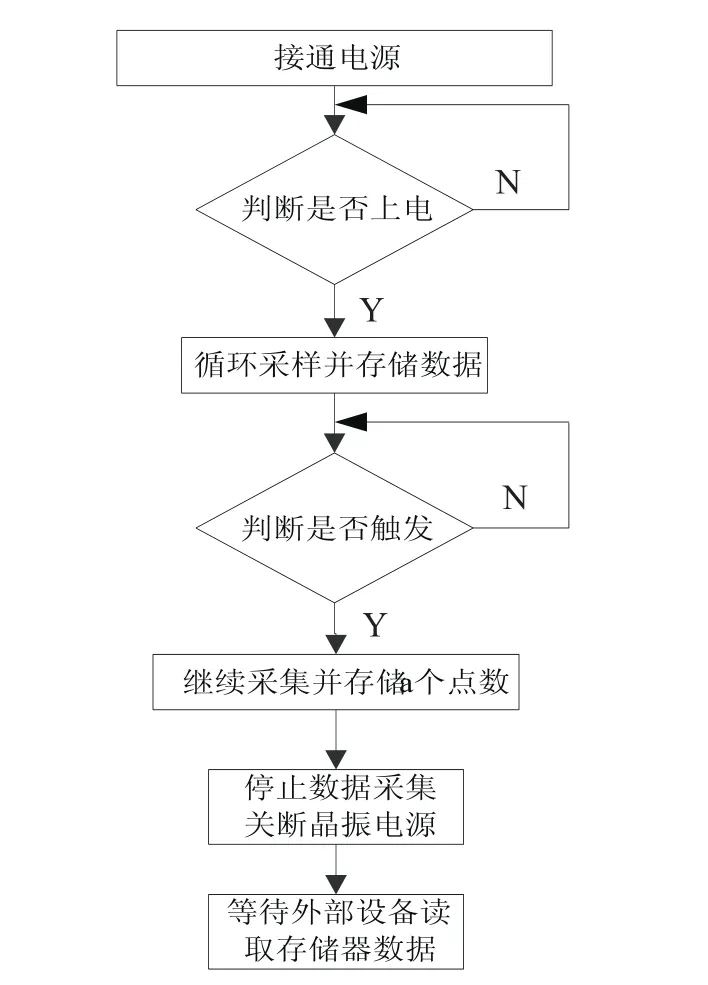

4通道存储测试系统软件由上电模块程序、触发模块程序、负延迟模块程序、读取数据模块程序四部分组成。四通道存储测试系统软件总框图如图5所示。

图5 系统软件总框图

触发模块程序实现了触发通道的设置、触发值设置等功能,通过编程可以指定四个通道中的任一通道为触发通道,触发方式为内触发,触发值为四位二进制码,和AD7492的高四位D11、D10、D9、D8作比较,当该值小于AD7492的高四位时即触发,比如将触发值设为1001,则触发通道输入电压大于(2-1+2-4)×2.5V=1.40625V时触发。

负延迟模块程序实现了地址的负延迟计数和结束数据采集功能,即触发后再采集a个点结束数据采集,a为负延迟的设定值。运用负延迟技术能够有效记录信号触发前和触发后的数据,本系统的存储器容量为256K,若负延迟设定值为a,那么可以记录触发前的(262144 –a)个数据点,触发后的a个数据点。数据采集结束后,CPLD将26管脚(ONB)置为低,关断VEE,切断晶振电源供给,并将ZZ置为低,使FM22L16工作在休眠状态。数据采集结束后,系统再次进入低功耗状态。

读取数据模块程序负责和外部读数设备通信,完成将数据传送到上位机。读取数据是从结束数据采集时的地址处读取存储器数据到上位机。

4 实验结果

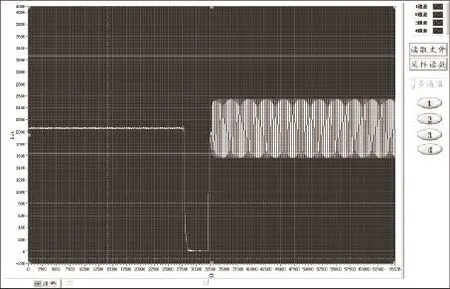

首先将触发通道设为1通道触发,触发值设为1001,将负延迟设为128K。2通道和3通道分别输入2V和1V的直流电压,4通道接地,1通道用信号发生器先输入偏移电压为1.25V,峰峰值为10mV的正弦波。给系统上电,系统将对4个通道的信号循环采样,将正弦波峰峰值调为400mV,此时系统触发,系统继续采样128K的数据点后结束采样。将存储器中的数据读取到上位机上显示如图6所示。

图6 上位机显示图

5 结 语

本文设计了一种基于CPLD的4通道存储测试系统,该测试系统是由硬件电路控制,并实时将4个通道的信号经AD转换后存储起来,进而读取到上位机中显示和处理。实际的应用表明,该系统能够准确地采集并存储4个通道的信号。

[1]张文栋.存储测试系统的设计理论及其应用[M].北京:高等教育出版社,2002:1-7.

[2]尚凤晗.基于可编程器件的存储测试系统设计[D].太原:中北大学,2009:45-47.

[3]刘海涛,裴东兴,范锦彪,王燕.高采样频率弹载加速度测试系统的设计[J].电子测试,2010(12):79-82.

[4]刘立军.多层复合介质侵彻测试技术研究[D].太原:中北大学,2010:24-26.

[5]朱仕永,祖静,范锦彪.基于CPLD的弹载加速度存储测试仪[J].探测与控制学报,2009(3):43-46.

[6]肖胜武,靳鸿,祖静.基于CPLD的存储测试系统的研究[J].电子测量与仪器学报,2008(Z2):626-629.

[7]祖静,申湘南,张文栋.存储测试技术[J].测试技术学报,1994(2):25-27.

[8]巩林萍,张凯,祖静,靳鸿.基于CPLD的可变频采样存储测试系统的设计[J].计量与测试技术,2009(11):38-40.