基于动态衬底电阻的自衬底触发ESD保护器件

吴晓鹏,杨银堂,董 刚

(西安电子科技大学微电子学院/宽禁带半导体材料与器件教育部重点实验室,陕西西安 710071)

为了改善集成电路的工作速度和性能,器件特征尺寸不断缩小,导致静电放电ESD(electrostatic discharge)损伤成为深亚微米CMOS IC面临的主要可靠性问题,因此需要在输入和输出电路及焊盘周围加入ESD保护器件来预防静电损伤[1-3]。通常保护器件的尺寸会设计得较大以保证能够达到预期的ESD鲁棒性,而出于成本与工艺兼容性的考虑,使用最广泛的是基于多叉指版图结构实现的栅接地NMOS GGNMOS(gate grounded NMOS)ESD保护器件。由于多叉指GGNMOS器件中的每个叉指均存在寄生横向晶体管LNPN(lateral NPN),且中间叉指距离器件周围的P+保护环最远导致其寄生衬底电阻最大。当ESD应力施加到保护器件漏极时,中间叉指的寄生LNPN基极电压能够最快达到导通阈值,使得中间叉指将会早于其他叉指导通。一旦中间叉指NMOS被触发,ESD应力电压将会被箝位到其保持电压,则ESD电流只能通过中间叉指局部区域泄放,即出现不均匀导通现象[4-5]。最终在其他叉指尚未导通前保护器件就已被损毁,使得保护器件鲁棒性大大降低。

针对多叉指GGNMOS保护器件不均匀导通现象提出了许多解决的方法,包括使用栅耦合NMOS GCNMOS(gate coupled NMOS)[6]、衬底触发NMOSSTGGNMOS(substratetriggerGGNMOS)[7]等保护器件。GCNMOS通过栅极连接的电阻、电容将适当的电压耦合到栅上实现保护器件的均匀导通,但较高的栅偏置会引入更多沟道电流和较高电场破坏保护器件的薄栅氧,出现“过栅驱动”效应,导致ESD水平突然衰减。衬底触发NMOS通过利用保护器件与接到电源的横向二极管所构成的纵向PNP管实现衬底触发,达到增强ESD鲁棒性以及降低触发电压的目的。但是,该器件需要额外的RC监测电路,对设计水平要求较高且占用面积较大。本文基于0.18μm salicide浅沟槽隔离CMOS工艺提出了一种基于动态衬底电阻的自衬底触发GGNMOS SSTGGNMOS(self substrate triggered)器件,该结构不需要额外的监测电路和新工艺条件就可实现保护器件的均匀触发和低触发电压,达到改善保护器件性能的目的。

1 基于动态衬底电阻的SSTGGNMOS

1.1 SSTGGNMOS

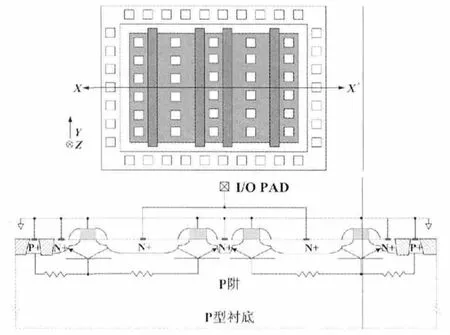

传统多叉指GGNMOS器件的版图形式和剖面图结构如图1所示,这种结构在ESD应力下存在不均匀导通现象的主要原因是中间叉指的寄生LNPN由于距离衬底接触保护环较远,所以其基极电阻即衬底电阻值最大,这使得中间叉指NMOS会先于其他叉指触发。在此过程中保护器件发生的骤回特性使最早导通的中间叉指单独承受了ESD应力,导致保护器件远没有发挥其全部性能而过早击穿失效。

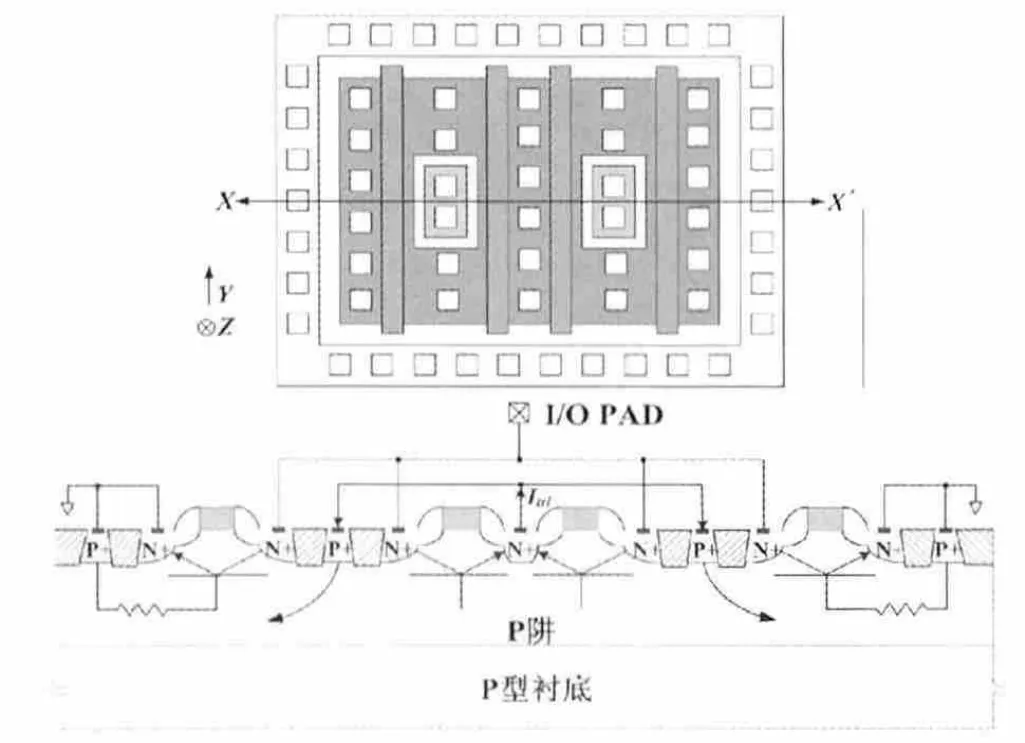

SSTGGNMOS保护结构利用上述传统GGNMOS中最早导通的中间叉指电流作为衬底触发电流来改善叉指间的不均匀导通[8]。其基本原理是在每个NMOS叉指的漏极插入P+扩散作为衬底触发节点,并且连接到中间叉指的源端。当中间叉指在ESD应力下由于具有较大的寄生LNPN基极电阻而较早开启时,其从源极传导的泄放电流将流入其他叉指的衬底触发节点,使其他叉指的寄生LNPN基极电压升高,达到使保护器件均匀开启、改善ESD保护性能的目的。图2所示为SSTGGNMOS结构的版图和剖面图结构。

图1 传统多叉指GGNMOS保护器件Fig.1 Traditional multiple finger GGNMOS protection device

图2 SSTGGNMOS保护器件Fig.2 SSTGGNMOS protection device

然而当自衬底触发结构的中间叉指被触发,且其叉指电流流过衬底电阻触发其他叉指后,中间叉指寄生LNPN的基极和发射极间电压将变得近似为0。也就是说只要其他叉指被触发,则中间叉指将被抑制直到关断。因此,自衬底触发结构虽然能够改善保护器件的均匀开启,但其鲁棒性性能并未达到应有水平。

1.2 基于动态衬底电阻的SSTGGNMOS

由于工艺尺寸和电源电压的不断减小,器件的栅氧保护对于保障电路的可靠性显得尤为重要,这要求ESD保护器件具有较低的触发电压和较高的失效电流。现有研究表明,采用工艺注入法[9]、有源电路法[10]和动态衬底电阻技术[11]可实现减小保护器件触发电压的目的。前两种方法通过增大衬底电流来降低寄生LNPN开启所需的触发电压,但它们均存在增加版图面积和工艺成本的问题。动态衬底电阻技术则通过在GGNMOS保护器件源极与P+衬底接触扩散之间插入N阱,并将其与保护器件漏极一起连接到IO焊盘,实现调节保护器件衬底电阻最终降低触发电压的目的。

图3所示为本文提出的结合了动态衬底电阻的SSTGGNMOS保护器件版图与剖面图。在正向ESD脉冲施加到I/O焊盘上时N阱电位为高,则N阱与P型衬底所构成的PN结处于反偏状态,且耗尽层宽度在P型衬底一侧较宽。源自SSTGGNMOS中间叉指源极的触发电流从漏极中间的P+接触注入衬底,并由于上述反偏PN结耗尽层的存在使得电流传输路径增长,间接增大了保护器件衬底电阻。因此该结构可有效减小保护器件触发电压,同时保证电流分布的均匀性。

图3 基于动态衬底电阻的SSTGGNMOS保护器件Fig.3 SSTGGNMOS protection device with dynamic substrate resistance

2 器件仿真分析

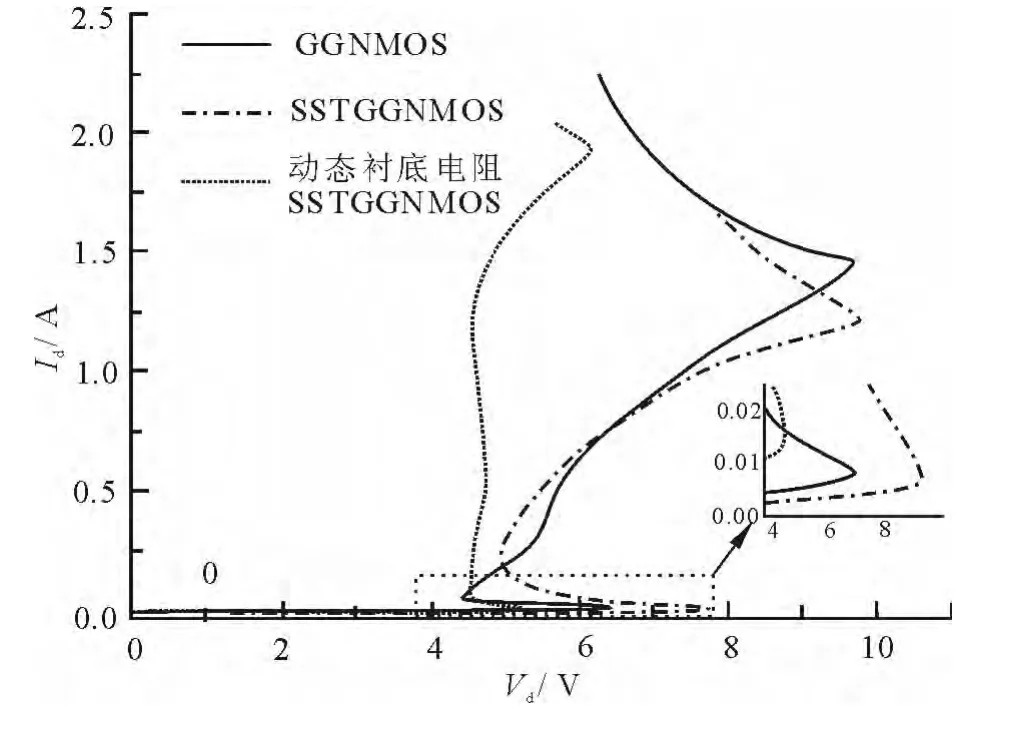

为了考察动态衬底电阻SSTGGNMOS的保护能力,对基于0.18μm salicide浅沟槽隔离CMOS工艺的上述3种保护器件结构利用ISE TCAD器件仿真软件进行了仿真分析。保护器件单个叉指宽度为50μm,沟道长度为0.8μm,叉指数为4。图4所示为对传统GGNMOS,SSTGGNMOS和动态衬底电阻SSTGGNMOS进行击穿特性仿真得到的I-V曲线。

图4 保护器件击穿特性仿真曲线Fig.4 The breakdown characteristic simulation curve of the protection device

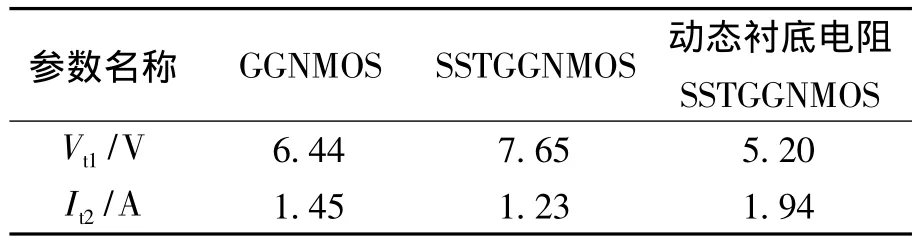

从图4的I-V特性曲线提取3种保护结构的二次击穿电流与触发电压值列于表1中,对比可见传统GGNMOS与SSTGGNMOS的触发电压Vt1值分别为6.44V和7.65V。而动态衬底电阻SSTGGNMOS的触发电压仅为5.2V,与SSTGGNMOS相比触发电压降低了约32%。同时与栅氧瞬态击穿电压(约8V)相比,显然本文结构具有更大的设计余量能保障保护器件的可靠性水平。

表1 3种保护结构的二次击穿电流与触发电压仿真值Tab.1 The simulation results of second breakdown current for three protection structures

从二次击穿电流It2水平来看,SSTGGNMOS的失效电流是3种结构中最低的,约为1.23A,传统GGNMOS结构的失效电流约为1.5A。而动态衬底电阻SSTGGNMOS的失效电流值最大约为1.94A(即9.7mA/μm),完全满足常规深亚微米保护器件5mA/μm的指标要求[12]。根据之前的分析,由于SSTGGNMOS保护器件的中间叉指在触发周围叉指后就处于截止状态,因此其泄放能力受到限制,并导致其失效电流水平与传统GGNMOS相比没有优势。但是,若保护器件叉指数更多,即多叉指不均匀导通现象严重时,SSTGGNMOS相比传统GGNMOS在改善器件均匀导通性以及失效电流水平方面的优势将会体现出来。而动态衬底电阻SSTGGNMOS结构由于具有较低的触发电压,在受到ESD应力时能够较早触发进入骤回状态,且N阱的引入使得保护器件叉指的寄生LNPN导通面积更宽,热量更加容易散发来泄放更多的ESD电流,因此本文所提的新结构既有较低触发电压和均匀导通的优点,同时相比SSTGGNMOS具有更好的ESD鲁棒性水平。这一点可以由图5所示的人体模式HBM(human body mode)仿真得到的平均温度曲线得到验证。从图中曲线可以看出,由于动态衬底电阻SSTGGNMOS具有良好的均匀导通性,因此在施加ESD应力期间其平均温度保持在较低水平,所以能够承受较高的失效电流水平,从而具有优于其他两种结构的保护性能。

图5 3种保护结构进行HBM仿真得到的平均温度曲线Fig.5 The average temperature curves get from the HBM simulation of the three protection structures

3 结语

为了改进多叉指GGNMOS保护器件的导通均匀性以及降低触发电压,本文提出了一种基于动态衬底电阻的SSTGGNMOS保护器件结构,并基于0.18μm salicide浅沟槽隔离CMOS工艺进行了I-V特性和温度特性仿真分析,结果表明,动态衬底电阻 SSTGGNMOS具有9.7mA/μm的良好失效电流水平,其触发电压也降低了约32%。本文利用版图方法实现了保护器件的性能改善,为提高深亚微米ICs中的保护器件性能提供了一定方法依据。

[1]YEH C T,KER M D.Resistor-less design of powerrail ESD clamp circuit in nanoscale CMOS technology[J].IEEE Transactions on Electron Devices,2012,59(12):3456-3463.

[2]WON J I,JUNG J W,YANG I S,et al.Design of ESD protection device using body floating technique in 65nm CMOS process[J].Electronics Letters,2011,47(19):1072-1073.

[3]DUVVURY C,BOSELLI G.ESD and latch-up reliability for nanometer CMOS technologies[C].Proc of International Electron Devices Meeting,San Francisco:IEEE,2004:933-936.

[4]KWANG-HOON Oh,DUVVURY C,BANERJEE K,et al.Analysis of nonuniform ESD current distribution in deep submicron NMOS transistors[J].IEEE Transactions on Electron Devices,2002,49(12):2171-2182.

[5]VASHCHENKO V A,CONCANNON A,TER BEEK M,et al.Physical limitation of the cascaded snapback NMOS ESD protection capability due to the non-uniform turn-off[J].IEEE Transactions on Device and Materials Reliability,2004,4(2):281-291.

[6]WANG Y,JIA S,CHEN Z J,et al.A design model of gate-coupling NMOS ESD protection circuit[C].Proc of International Conference on Solid-State and Integrated Circuits Technology,Beijing:IEEE,2004:1637-1640.

[7]YONG-SEO K,KWI-DONG K,JONG-KEE K.ESD protection circuit with low triggering voltage and fast turn-on using substrate-triggered technique[J].IEICE Electronics Express,2009,6(8):467-471.

[8]KER M D,CHEN J H.Self-substrate-triggered technique to enhance turn-on uniformity of multi-finger ESD protection devices[J].IEEE Journal of Solid-State Circuits,2006,41(11):2601-2609.

[9]CHATTY K,ALVAREZ D,GAUTHIER R,et al.Process and design optimization of a protection scheme based on NMOSFETs with ESD Implant in 65nm and 45nm CMOS technologies[C].Proc of Electrical Overstress/Electrostatic Discharge Symposium,Anaheim:IEEE,2007:7A.2-1-7A.2-10.

[10]KER M D,CHEN T Y.Substrate-triggered technique for on-chip ESD protection design in a 0.18-μm salicided CMOS process[J].IEEE Transactions on Electron Devices,2003,50(4):1050-1057.

[11]VASSILEV V,GROESENEKEN G,STEYAERT M,et al.Dynamic substrate resistance snapback triggering of ESD protection devices[C].Proc of International Reliability Physics Symposium,Dallas:IEEE,2003:256-260.

[12]DUVVURY C,RAMASWAMY S,AMERASEKERA A,et al.Substrate pump NMOS for ESD protection applications[C].Proc of Electrical Overstress/Electrostatic Discharge Symposium,Anaheim:IEEE,2000:1A.2-1-1A.2-11.