基于FPGA的信号发生器在分频器检测上的应用

王婳懿 董 欣 张成林

(上海航天设备制造总厂,上海 200245)

运载火箭测量系统分频器用于实现火箭上三级发动机涡轮泵转速的测量和变换,将发动机转速降低到适合中心程序单元采集的频率范围内,具有极其重要的作用。在之前的分频器调试中,使用信号发生器模拟发动机涡轮泵产生的转速信号作为分频器的激励信号,当同时进行多台分频器的高/低温试验时,需要多台信号发生器提供激励信号,在信号发生器数量有限的情况下,严重影响了生产进度。 笔者采用直接数字频率合成技术[1],以MSP430为控制系统、 FPGA为核心,设计了一台信号发生器,可同时给8台分频器提供正弦波激励信号。该信号发生器在0~9 999Hz频段内频率可选,波形光滑,系统杂散小。

1 信号发生器系统总体设计①

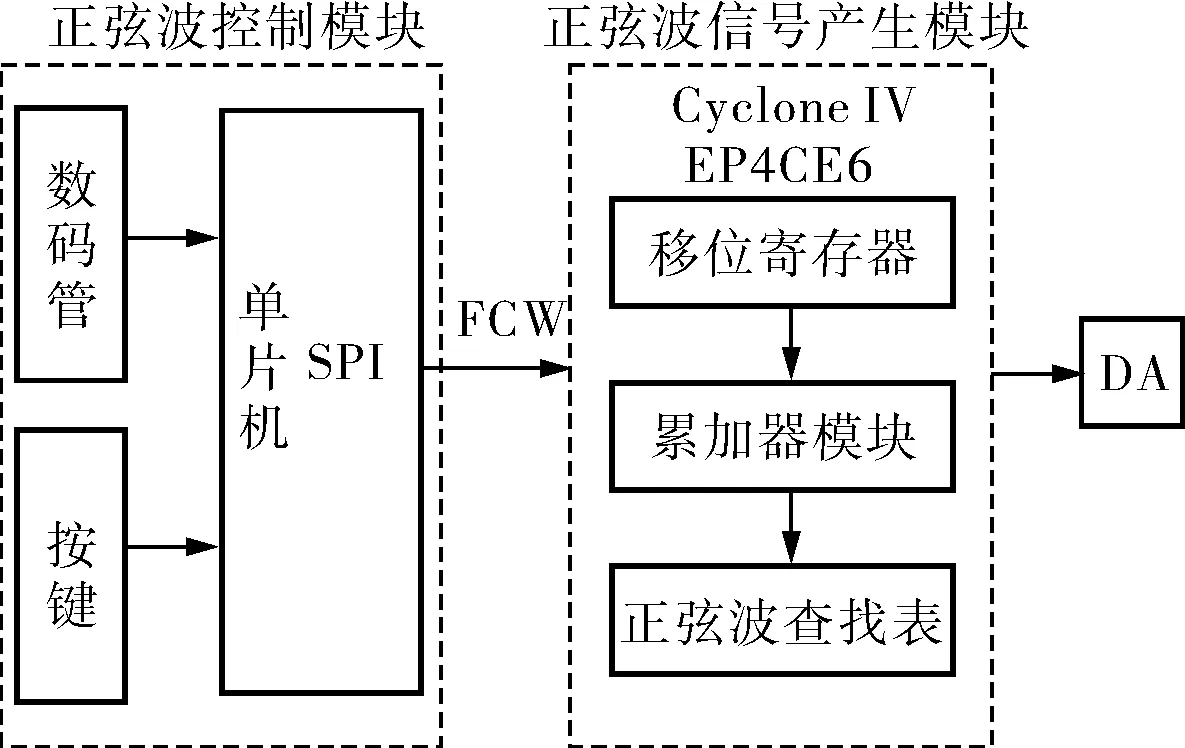

直接数字频率合成器是基于奈奎斯特采样定理,将已知信号取样、量化、编码,形成可查数表存于ROM中,通过频率控制字的改变,输出所需波形的一种波形合成技术。笔者设计的利用其产生正弦波的信号发生器系统如图1所示。

图1 正弦波信号发生器系统框图

由图1可知,系统由正弦波控制模块和正弦波信号产生模块两部分组成。正弦波控制模块由MSP430F149和外围按键、数码管构成。系统通过单片机产生频率控制字,设Fcw为频率控制字,即累加器模块每次累加的步进值;fc为外部参考时钟信号的频率;N为相位累加器位数,当累加器位数为N时,可以读取2N个存储单元中的数据,此时一个正弦波的一个周期最多可以划分成2N个抽样点。FPGA输出的正弦波频率f=Fcw×fc/2N,根据此公式可计算出所需频率正弦波的频率控制字大小、按键显示所选正弦波频率和数码管显示正弦波频率。

正弦波信号产生模块由移位寄存器、累加器模块和正弦波查找模块构成。通过正弦波产生模块产生正弦波的数字量,再经过AD转换得到所需的正弦波。

2 正弦波控制模块设计

正弦波控制模块以MSP430F149为核心控制单元,外接按键和数码管。当用户按下选频数字按键0~9后,再按下确认按键,MSP430f149接收按键的数据,产生一个频率控制字,将频率控制字发送给FPGA,产生用户所选频率的正弦波。为了直观地显示按键设定的当前正弦波的频率值,设置4个七段LED数码管显示当前正弦波的频率。在按数字按键时,按键值采用BCD编码方式,再通过计算将BCD转换成二进制码作为真正的频率控制字来控制频率,为防止溢出,要求BCD码向N位宽的二进制码转换时,N≥[M·log210],其中N为累加器位宽,M为最大频率控制字十进制位数。正弦波控制模块的软件控制流程如图2所示。由图2可知,系统循环检测扫描按键值,当有键值按下后,系统通过中断进入循环体。

图2 正弦波控制模块的软件控制流程

单片机采用硬件SPI的方式将频率控制字发送给FPGA。SPI节约了芯片管脚,较并行总线通信而言很大程度上节省了PCB的布局空间。该设计中通过MSP430F149单片机的CLR、SIMO0、UCLK0口接入FPGA的IO口,UCLK0作为移位寄存器的时钟信号,32位数据通过SIMO0口送入FPGA的移位寄存器数据输入口,CLR信号经过非门后作为移位寄存器的复位信号,把频率控制字按照先低位再高位的方式进行发送。

3 正弦波信号产生模块设计

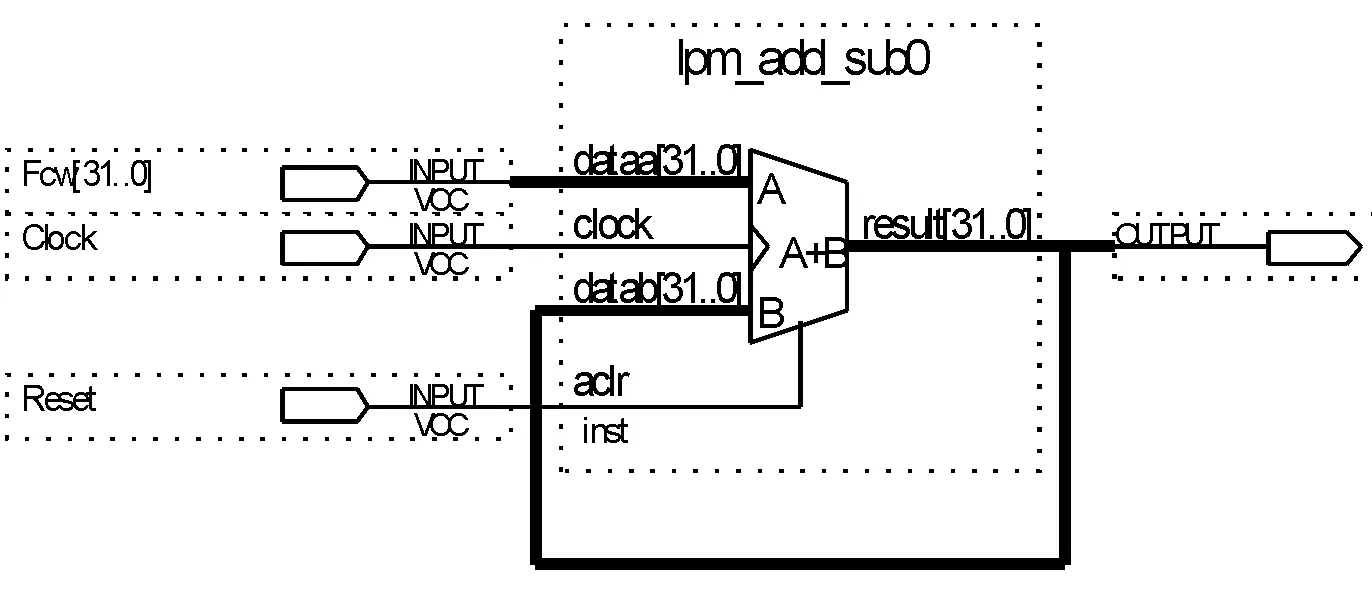

正弦波信号产生模块由移位寄存器、累加器模块和正弦波查找模块3部分组成[2]。移位寄存器选择串入并出的32位移位寄存器,移位寄存器将SPI发送的32位串行数据经过移位后并行发送给累加器模块。累加器模块(图3)把频率控制字每一次累加后得到的数据作为正弦查找表的存储单元的地址[3],将前一次累加的和作为后一次累加时的累加值之一。

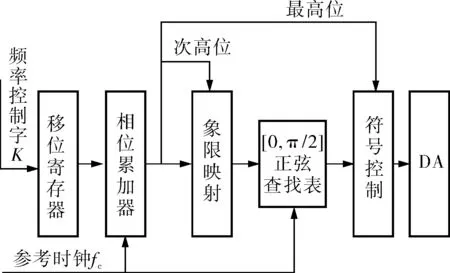

图3 累加器模块

在该系统中,把10MHz时钟信号作为外部参考时钟,最小频率分辨率为10×106/2N,为实现最小频率分辨率1Hz,选取的N至少大于24,笔者选取N=32。在直接数字频率合成中,一般相位累加器的位数M大于ROM的寻址位数N,因此累加器的输出寻址低位M-N位必须舍去,表现在输出频谱上就是杂散分量。为了降低相位截断误差,需要增加存储正弦波幅度量化值的ROM的地址位数,但是寻址位数增加一位,ROM的存储容量就增加一倍,为减少正弦查找表的数据量,根据正弦函数的对称性采取压缩存储的办法,在ROM中只储存0~π/2的数据,截取相位累加器的高15位作为ROM寻址的位数,相位的高两位用来确定波形的象限,其余13位用来查找正弦表,生成ROM地址。利用最高位和次高位两位确定当前相位值属于哪个象限,象限确定法见表1。

表1 象限确定法

整个正弦波信号产生模块流程如图4所示。按照图4所示进行Verilog编程[3],得到所需的符合要求的正弦波信号发生器。

图4 正弦波信号产生模块流程

4 波形仿真

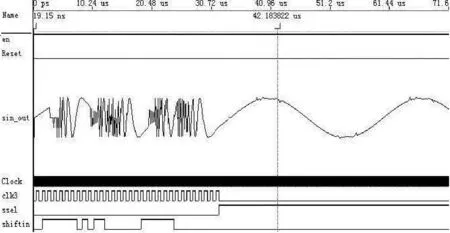

对产生的波形进行仿真,结果如图5所示,当频率控制字为十六进制数FC0D7E时,正弦波频率为38 460Hz,正弦波每个周期约为26μs。图5所示即为频率为38 460Hz正弦波的仿真波形。

在初始位置处,波形存在一定的杂乱,这是因为当按键选择频率后,单片机产生一个频率控制字,通过单片机的SPI口把频率控制字传输给FPGA,FPGA收到频率控制字后,先需要清除已有的频率控制字,并开始把新的频率控制字传给32位的移位寄存器,移位寄存器在32个时钟到达后,才把32位串行数据完整转移,当时钟周期超过32位时,Fcw为固定值,得到光滑的正弦波波形。

图5 软件仿真波形

实际中,为取得较多抽样点,提高正弦波的精度,降低波形失真度,只取10kHz以下的频率。试验证明在10kHz频段下产生的正弦波比图5的仿真波形更加光滑。

5 结束语

笔者设计基于MSP430和Cyclone IV FPGA设计了在0~9 999Hz频段范围内,频率分辨率为1Hz,频率可选的正弦波信号发生器。发生器系统采用直接频率合成法,采取压缩存储法进行查表,降低了相位截断误差,得到的正弦波波形光滑,杂散影响小。经测试证明,产品性能可靠,在某运载火箭分频器检测系统上使用,极大地提高了生产效率。