基于FPGA的动态自重构系统原理与实现

徐彦峰,张丽娟,谢文虎

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.无锡华普微电子有限公司,江苏无锡214035)

基于FPGA的动态自重构系统原理与实现

徐彦峰1,张丽娟2,谢文虎1

(1.中国电子科技集团公司第五十八研究所,江苏无锡214072;2.无锡华普微电子有限公司,江苏无锡214035)

现场可编程门阵列(Field Programmable Gate Array,FPGA)提供了强大的可编程接口,支持灵活的现场可编程能力。动态可重构设计方法可以在尺寸、重量、功率和成本等方面优化传统的FPGA应用。目前控制、存储和接口组成的动态可重构实现系统,虽然可以实现对FPGA的动态可重构,但需要额外增加多个器件,反而使FPGA应用系统更加复杂。基于动态可重构原理,提出了一种动态自重构系统的原理和实现方法。该方法通过在静态逻辑中添加自重构模块,对自身可重构分区进行功能修改,从而实现对自身的动态重构。设计了两种LED灯的闪烁方式模块,实验结果证明:通过自重构技术,可以实现这两种闪烁方式的切换,证明了自重构技术的可行性。

FPGA;动态可重构;动态自重构

1 引言

目前,FPGA技术日益成熟,在为用户提供大量高性能可编程资源的同时,也提供了强大的可编程接口,支持灵活的现场可编程能力[1]。动态可重构进一步提高了FPGA的灵活性,成为目前应用研究的热点[2]。

动态可重构类似于时分多路复用,将时间轴上不重叠的功能隔离并实现为可重新配置的模块。该方法是:在完整的BIT文件配置FPGA之后,根据系统的需求加载局部资源的配置文件,修改FPGA中可重构区域的功能,实现不同功能的灵活切换,且不影响未重新配置(静态逻辑)区域功能的正常运行。动态可重构设计方法可以在尺寸、重量、功率和成本等方面优化传统的FPGA应用[4]。典型的应用如网络交换机:为了确保交换机支持多种接口协议,通常针对每个接口协议要求分别实现相应的物理接口,从接口协议利用率的角度分析,该设计方法的效率比较低,因为每个端口同一时间只能使用一个接口协议。如果每个端口的接口协议设计为可重构模块,每次只将需要的接口协议模块加载到可重构模块中,便可实现更高效的设计。这也大量削减了将多个协议引擎连接到一个端口时占用的逻辑资源。

传统的动态可重构实现方法是通过CPU等控制器读取配置文件,并决定何时对FPGA进行重构;存储器负责存储需要的配置文件;此外还需要CPLD之类的控制芯片,负责将CPU传输的配置比特流进行时序转换,产生满足FPGA配置时序的信号,从而实现对FPGA的重新加载[3~4]。这种控制、存储和接口的组合适合绝大部分系统,但缺点在于需要额外增加存储器、CPU等多个器件,无形中增加了硬件的尺寸、重量、功率和成本。

本文基于目前的动态可重构原理,提出改进型的硬件实现方案,即FPGA动态自重构。该方法的原理是,通过在FPGA静态逻辑块中添加动态重构的控制逻辑,在需要重构时自动加载相应局部资源的码流文件,最终实现FPGA对自身的局部重构。该方法的优点在于可以在实现可重构的前提下不增加额外的硬件开销,有利于降低产品的成本、功率和重量。

2 FPGA动态可重构配置文件生成方法

常规SRAM工艺的FPGA都可以实现功能重配置,但并非都能实现动态可重构。目前支持动态可重构的器件主要为Xilinx公司的FPGA芯片。Xilinx公司FPGA芯片的配置文件格式主要有.mcs、.bin、.bit等,Xilinx公司的FPGA开发软件直接生成的FPGA配置文件格式为.bit文件,然后可通过相应的工具将.bit文件转换成.bin、.mcs等其他格式。

动态可重构.bit配置文件生成流程如图1所示,包含功能分区,各分区不同功能模块综合生成网表,各功能模块实现并生成可重构.bit文件。下面将结合图1,介绍FPGA动态可重构配置文件的生成方法。

图1 动态可重构.bit配置文件生成流程

实现动态可重构的FPGA设计类似于实现共享公共逻辑的多个非可重构逻辑设计[2]。具体设计分为以下几步。

2.1 整体功能划分

首先需要完成对整体功能的分区,将FPGA运行过程中不需要更改的逻辑划分到静态逻辑模块,将需要更改的逻辑划分到可重构逻辑模块中,并获得可重构模块A、可重构模块B等可重构模块。分区用于确保多个设计之间的静态逻辑相同。

2.2 生成各个功能块网表文件

完成分区后,需要使用专用综合软件将分区中的各个可重构模块综合并生成网表文件(文件格式为EDIF或者NGC)。完成以上操作后便获得了静态逻辑网表和可重构模块网表。

2.3 向可重构分区导入网表

在ISE工具中PlanAhead建立综合后工程(post-synthesis Project)并注意勾选使能部分可重构(Enable Partial Reconfiguration)。完成功能建立后导入顶层静态网表和静态网表约束文件。通过选择已经在顶层静态逻辑中例化的可重构模块并使用“设置分区”(Set Partition)对话框菜单命令来导入可重构分区的网表内容。如该分区还需要加入其他网表,则在导入完第一个网表后,使用“加入可重构模块”(Add Reconfigurable Module)对话框菜单来导入该可重构分区的其他网表内容。此外还可以在该分区导入“黑盒子模块”(Black Box Modules),只需在进入导入界面后选择“将此可重配置模块添加为不带网表的黑盒”(Add this Reconfigurable Module as a black box without anetlist)选项即可。

2.4 定义可重构区域

在PlanAhead软件中导入了所有可重配置分区的所有可重构模块网表后,下一步就是定义设计的物理布局。从主PlanAhead工具栏中,选择“布局规划模式”(Floorplanning mode)打开FPGA的物理约束选项卡和平面图视图,选择Set PBlock Size命令并在FPGA的Device视图中绘制一个矩形区域,要求该区域内包含的资源数目略大于可重构模块所需资源的最大值。完成所有分区的设置后需运行DRC检查,以保证设计合乎规则。

2.5 创建配置并生成.bit文件

将所有模块的网表文件导入相应分区并设置了各分区大小后,系统会自动生成名为config_1的配置实现,该配置实现中默认选择每个可重构分区中导入的第一个可重构模块。为了生成各分区中其他功能模块的可重构配置文件,需要建立多个配置实现,并根据需要选择每个分区包含的可重构模块。但是,无论创建多少个配置实现文件,都先运行一个配置实现,实现后选择Promote Partitions选项,产生可导入的静态逻辑。创建其他配置实现时,静态逻辑(static logic)部分选择“导入”(Import),其他可重构模块可选择“实现”(Implement)或“导入”(Import)。

所有需要的配置实现建成后,分别运行各个配置实现并生成.bit文件,生成的文件包含一个完整的.bit配置文件(图1中的Full_1.bit、Full_2.bit等)和这个配置实现中选择的模块的可重构.bit文件(图1中的RMA.bit、RMB.bit等)。如果有多个分区,则会产生多个可重构.bit文件(可根据需要转换成.mcs等其他形式)。

3 FPGA动态自重构的实现

3.1 FPGA动态自重构的实现方法

基于上述FPGA动态可重构的实现过程,本文提出了一种FPGA动态自重构方法。该方法的原理是,在FPGA的静态逻辑中加入对存储配置文件的控制模块,并由FPGA根据外部控制器或内部控制逻辑选择需要重构的分区,并将该分区的文件写入FPGA,实现FPGA自己对自己的重构。其功能示意图如图2所示。

图2 动态自重构系统原理

在图2中,存储器内部保存了所有的可重构配置文件、存储器的地址、读写控制信号以及存储器的数据输出端口连接FPGA的专用配置引脚。

FPGA芯片在上电初始化完成后通过BPI模式将完整的配置文件写入FPGA,完整的配置文件里除包含静态逻辑外(静态逻辑中已经包含动态自重构功能模块),还包含各分区被选择的可重构模块。在完整配置文件完成对FPGA的配置后,FPGA便可以根据静态逻辑中的自重构功能,读取配置文件并完成对自身的动态重构。

3.2 FPGA动态自重构方案的验证

根据以上原理,本文采用AMD公司型号为Am29LV640M的NOR FLASH芯片存储可重构文件和完整配置文件,动态自重构的目标FPGA器件选用Xilinx公司Virtex-5系列的XC5VSX95T。动态自重构方案的验证硬件示意图如图3所示。

FPGA设置为Master BPI-UP模式,其连接方式与正常配置FPGA连接方式相同,Am29LV640M的数据端口连接FPGA的配置端口,需要1路普通I/O连接FPGA的CCLK以保证在对自身进行自重构时存在能够接受数据的CCLK时钟输入。

图3 动态自重构方案的验证电路

在上电且储存器和FPGA完成初始化后,FPGA通过Master BPI-UP模式配置完整的配置文件。当FPGA需要自重构时,只需读取预存在Am29LV640M的可重构配置文件即可,由于FPGA是在CCLK的上升沿采集数据,所以配置数据流需要在CCLK的下降沿更新,以保证配置数据流满足建立保持时间。

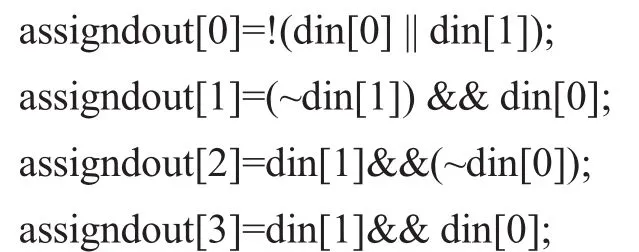

根据以上验证方案的硬件电路,本文设计了一个动态自重构的演示工程。其中,该工程包含一个2输入、4输出的分区和实现自重构功能的静态逻辑;该分区含有2个可重构模块,每个模块根据当前的2个输入din[1:0],产生不同形式的4个输出dout[3:0]。第一个模块为一个2位4位译码器,其输出逻辑表达式为:

第二个模块dout[0]输出恒定为高,其他值的输出表达式为:

静态逻辑为每隔5.37 s读取Am29LV640M数据对可重构分区进行自重构,两个可重构模块配置文件交替被读取;此外,静态逻辑还包含向可重构分区提供输入值的功能,该功能为每隔0.34 s更新一次输入数据,依次为2’b00,2’b01,2’b10,2’b11,周而复始。使用逻辑分析仪获得的4个输出数据如图4所示。

在图4中,通道A2(4~7)分别对应dout[0~4]; FPGA芯片在约5.8 s完成完整配置文件的配置,完整配置文件中只有能够实现自重构和向可重构分区提供输入的静态逻辑,可重构分区被例化为黑盒,所以此时dout的输出为固定电平。在5.37 s后完成可重构分区第一个模块的自重构,其输出结果与设定的逻辑相符。再经过5.37 s,完成可重构分区第二个模块的自重构,输出结果与设定的逻辑也相同。

图4 动态自重构系统输出波形

4 结论

本文在动态可重构的原理基础上,提出一种动态自重构系统的原理和硬件实现方法。实验结果证明:只需要将动态局部重构的控制逻辑作为静态逻辑分配到FPGA的逻辑资源中,可以非常简单地实现FPGA对自身的动态重构。本系统对航空航天、网络等领域的系统应用具有较大的参考价值,可以在实现FPGA动态可重构的前提下,降低系统的复杂程度和整体功耗。

[1]周盛雨,孙辉先,陈晓敏,等.基于FPGA的动态可重构系统实现[J].电子器件,2007,30(2):646-649.

[2]Xilinx Company.UG702 Partial Reconfiguration User Guide(v14.5)[EB/OL].https://www.xilinx.com/support/documentation/sw_manuals/xilinx14_7/ug702.pdf,2017-04-26.

[3]卢振钧,肖扬灿.基于FPGA部分动态可重构的信号解调系统的实现[J].电子设计工程,2012,20(10):155-157.

[4]南希,龚龙庆,田卫,等.基于FPGA的动态可重构系统设计与实现[J].电路设计,2009,6:4-6,11.

Principle and Implementation of Dynamic Self-Reconfiguration System Based on FPGA

XU Yanfeng1,ZHANG Lijuan2,XIE Wenhu1

(1.China Electronic Technology Group Corporation No.58 Research Institute,Wuxi 214072,China;2.Wuxi Hope Microelectronics Co.,Ltd.,Wuxi 214035,China)

FPGA provides a powerful programmable interface that supports flexible field-programmable capabilities.Dynamic reconfigurable design methods can optimize traditional FPGA applications in terms of size,weight,power,and cost.The dynamic reconfigurable implementation system,which is composed of control,storage and interface,can realize dynamic reconfiguration of FPGA,but it needs to add more devices,make FPGA application system become more complicated.Based on the current dynamic reconfigurable principle,this paper proposes the principle and implementation method of dynamic self-reconfiguration system. This method can modify the self-reconfigurable partition by adding self-reconfiguration module to the static logic,so as to realize the dynamic self-reconfiguration of itself.This paper designs two kinds of LED lights flashing mode module,the experimental results show that:through self-reconstruction technology,you can achieve these twoflashmode switching.Andprovesthe feasibilityofself-reconfigurationtechnology.

FPGA;dynamic reconfiguration;dynamic self-reconfiguration

TN402

:A

:1681-1070(2017)09-0015-04

2017-7-11

徐彦峰(1977—),男,辽宁朝阳人,高级工程师,从事集成电路设计工作,主要研究方向为FPGA架构及内部模块的设计。