基于NoC的网络接口设计

王胜,屈凌翔

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

基于NoC的网络接口设计

王胜,屈凌翔

(中国电子科技集团公司第五十八研究所,江苏无锡214072)

与总线架构相比,片上网络具有支持并行通信、良好的可扩展性、规则的结构、可重用性等优点。网络接口是片上网络中处理器核与路由节点之间的接口,网络接口的数据转化和传输效率影响整个片上网络的工作效率。研究的NoC系统采用3×3二维mesh的结构,DSP核采用AMBA总线结构,路由节点采用包交换方式,为了实现二者之间的数据转换与交换,设计了网络接口。为了提升传输效率,网络接口设计支持数据批传输,批传输不需DSP核参与,节省处理器资源。在完成网络接口的RTL设计后,进行了仿真验证,保证了网络接口的功能正确性。

片上网络;网络接口;路由节点;数据包

1 引言

随着片上可集成的晶体管数目越来越庞大,设计者可以在一个单片上集成越来越多的处理器核及配套的复杂系统。但是随着处理器核数量的增加,传统基于总线架构的SoC显现出局限性:带宽限制、可扩展性差、设计复杂等,于是片上网络[1]架构应运而生。NoC[2]架构由瑞典皇家技术学院率先提出,随后斯坦福大学提出了包交换技术代替连线结构的思想[3]。国内参与NoC研究的高校也越来越多,如西安电子科技大学在路由算法[4~5]方面的研究,南京大学、哈尔滨工业大学、合肥工业大学等都在NoC领域有所建树。针对NoC架构系统规模大、功耗相对较高的问题,合肥工业大学提出采用总线翻转(BI)编码算法和格雷码编码组成联合编码的方法来降低功耗[6]。经过十几年的发展与论证,对于NoC架构的研究也趋于成熟。

片上网络的关键技术研究大致可以分为三个方向:拓扑结构,路由器和网络接口(Network Interface)。从结构上来说,不管什么形式的片上网络都是由路由模块和网络接口模块所构成的[7]。网络接口是NoC系统的重要组成部分,是本地子系统(处理器核)和路由节点之间的转接口,网络接口的数据转化和传输效率影响整个片上网络的工作效率。

网络接口的主要作用是:(1)让处理器核承担最小的通讯服务任务;(2)将处理器核与网络通信部分分离,即计算和通讯间的分离,使计算资源对网络透明,从而实现处理器资源间的互连,且能提高设计的重用性。网络接口在处理器一侧实现了总线接口,在网络一侧实现了网络接口。网络接口主要考虑地址信号、数据的打包、解包、编码、同步等问题。本文设计的网络接口主要功能包括:对AHB总线上的数据和路由节点(Router)上的数据包(Packet)进行数据格式转化和交换;实现本地内核到其他核存储空间的数据读写;实现本地存储空间和其他核存储空间之间的大批量数据传输。数据批传输主要负责大规模的数据传输,由网络接口控制,不需要处理器核参与,处理器核可以继续处理其他程序,极大地提高了处理器的效率。

2 网络接口设计

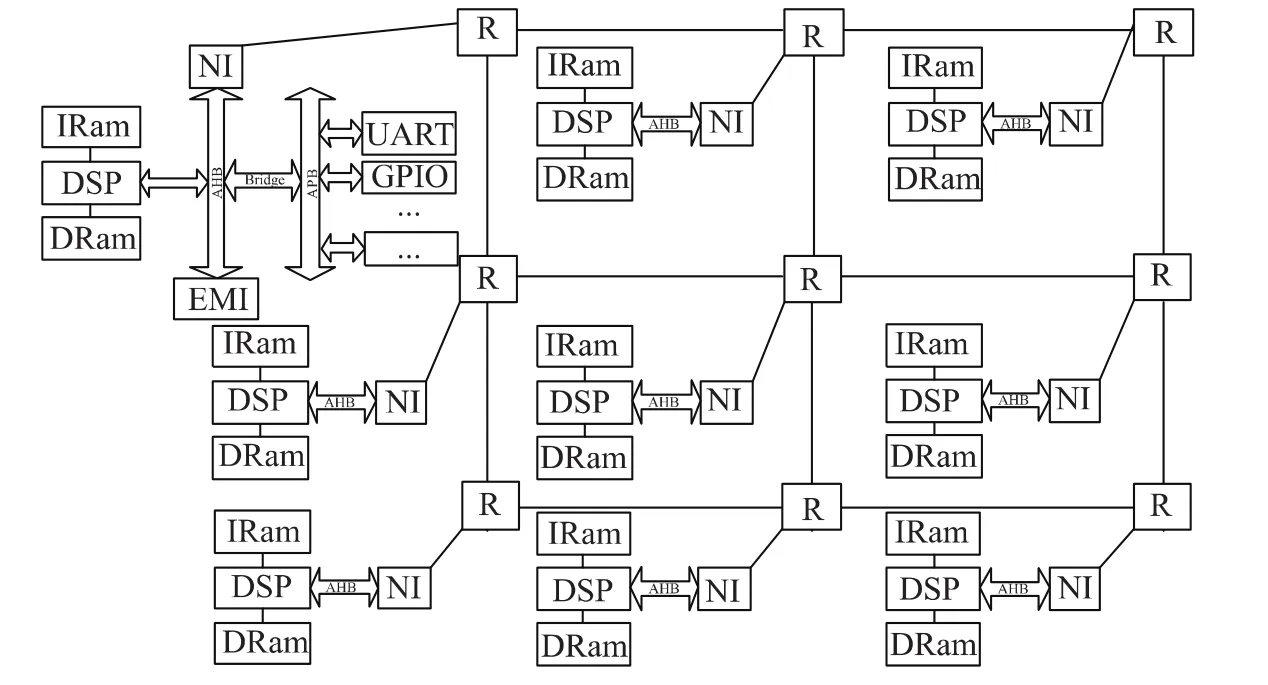

本文设计的网络接口集成在一个3×3二位mesh结构的NoC中,如图1所示,NoC系统中包含9个DSP核。网络接口(NI)连接本地DSP系统和路由节点,负责两者之间的数据交换。网络接口负责把本地DSP系统发过来的数据打包后发送到相连的路由节点中,数据包通过路由网络传送到目的路由节点,再通过目的地的网络接口解析后,取出传输的有效数据存入目的存储空间中。本文设计的网络接口支持三种数据传输模式:

(1)本地DSP写异地存储器:由本地DSP发起写数据请求,数据通过网络接口打包后发送到异地存储器;

(2)本地网络接口搬运本地存储器的数据到异地存储器:由本地DSP配置本地网络接口的控制寄存器,本地网络接口根据相关配置读入本地存储器的数据,打包后传输到指定的异地存储器中,支持数据批传输,传输过程中不需要DSP参与;

(3)本地DSP读异地存储器:由本地DSP配置异地网络接口,异地网络接口根据相关配置,搬运异地存储器的数据到本地存储器中,支持数据批传输。

图1 NoC系统框图

如图2所示,网络接口包括控制寄存器组、数据打包模块、数据包解析模块、输入输出FIFO、数据选择判定模块等。其中,控制寄存器组包含目的地址寄存器、源地址寄存器、搬运控制寄存器、写控制寄存器、中断状态寄存器、中断使能寄存器、中断屏蔽寄存器,主要负责生成数据传输地址、传输控制信息、中断信息、数据包信息。写打包模块主要负责把本地DSP直接往异地存储器写的数据打包,其接收本地DSP直接发过来的目的地址、包个数信息、待传输数据,分别打包生成头包和中间包,然后发送到输出FIFO。搬运打包模块主要根据控制寄存器组生成的相关控制信息,从本地存储器中读入待传输数据,打包后发送到输出FIFO,支持数据批传输,传输过程中不需要本地DSP参与。输出数据缓冲、输入数据缓冲是数据FIFO,主要负责数据发送和接收时的缓冲。数据包解析模块包括VC0解析模块和VC1解析模块,主要接收输入FIFO送过来的数据包,VC0解析模块接收来自虚拟通道0的数据包,VC1解析模块接收来自虚拟通道1的数据包,数据解析模块对接收到的数据包进行解析后,根据数据包中的目的地址信息,把数据写入本地存储器的对应地址中,并根据数据包中的中断信息更新中断状态寄存器,产生相应的中断给本地DSP。数据选择判定模块根据数据解析模块生成的控制信号,把来自虚拟通道0和虚拟通道1的数据存入各自的目的地址。

图2 网络接口结构框图

2.1 数据包结构

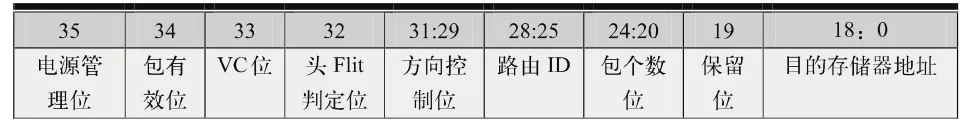

本地处理器系统中的数据通过AHB总线传输,而片上网络中的数据以数据包的形式传输,数据的打包与数据包的解析由网络接口完成。网络接口将AHB总线的数据和地址格式转化为Router能识别的数据包格式。数据包中包含头Flit和数据Flit,两种Flit结构分别如图3、图4所示。头Flit主要包含标志位、控制信息和目的存储器地址信息,数据Flit主要用来存储需要传输的数据。

隧洞地处祁吕贺兰山字型构造东翼前弧,华北地台之山西台背斜与鄂尔多斯台向斜的过渡带、相对稳定区。地质构造变动微弱、构造形迹有小型褶皱和断裂构造等。加里东造山运动影响整个华北区域地壳垂直整体隆起,致使本区缺失奥陶系上统-石炭系下统的地层,后又经历多次间隙性垂直升降运动,当进入燕山运动以后,构成东西构造有别,河谷下切侵蚀与堆积交替完成,黄河河流阶地发育。调查分析河曲县历史上地震情况,未发生过较大破坏性地震,考虑周边地震影响,本区地震基本烈度Ⅵ度。本区地震动峰值加速度为0.05 g,地震反应谱特征周期为0.45 s。

图3 头Flit结构

图4 数据Flit结构

2.2 数据发送逻辑

根据功能,网络接口主要划分为以下几个部分:AHB数据输出到Router的数据发送逻辑;Router数据包输入到AHB的数据接收逻辑;网络接口直接读存储器并发送数据到Router的数据搬运逻辑。数据发送逻辑负责把数据打包后发送到路由节点,主要通过以下三个步骤实现数据发送:

(1)配置写目的地址寄存器;

(2)配置写控制寄存器;

(3)DSP核通过AHB总线发送数据给网络接口。

数据发送逻辑整体结构如图5所示。MUX根据读使能信号选择将Core发送的数据或者网络接口读自MEM的数据发送到数据打包模块中。只要网络接口有读请求,则输入数据选择AHB RD DATA,否则选择AHB WR DATA。数据打包模块主要负责将接收的数据打包成Router能识别的数据包,数据包控制位有电源管理位、有效位、VC位、头Flit位、目的地址位、方向位等。打包模块将数据包发送到深度为16的输出FIFO中,该FIFO只有在不空且Router能接收数据包时才能进行RD操作,将数据包发送到路由。与Router的握手控制模块由Router输入的flow_ctrl_in信号控制,该模块中设计了一个计数器,计数器计数范围等于Router输入端口FIFO深度,网络接口每发送一个数据到Router,Router的flow_ctrl_in信号就进行一次反馈,计数器自动计数,若Router的FIFO已满,则网络接口不能发送数据,直到Router能再次接收数据。

图5 数据发送逻辑

2.3 数据接收逻辑

如图6所示,数据接收逻辑主要负责接收Router发送过来的数据并进行数据包解析,将有效数据通过AHB总线发送到本地存储器。路由数据包有VC0和VC1两种类型,根据数据包VC位(即bit34)判定数据包来自哪个虚拟通道,输入FIFO接收来自不同虚拟通道的数据,并根据虚拟通道位的值分别发送到VC0和VC1的解码逻辑中解码,把有效数据发送到总线。

图6 数据接收逻辑

输入FIFO存入Router数据后,只有当网络接口不对本地存储器进行RD操作时,才会根据数据输出选择逻辑的data_sel信号,选择是输出VC1还是VC0的数据,该数据位宽是36位,与Router数据位宽相同。VC1和VC0数据分别有自己的数据解析模块,该模块主要工作原理如下:若接收的Flit是头Flit,即数据[32]位为“1”,则记录该数据包的bit[31:0]位到寄存器中,这32位数据作为该数据包的目的地址基址;若接收数据不是头Flit,表示该数据包内数据是需要存入本地存储器的数据,数据解析逻辑将其中的bit[31: 0]位提出并存入寄存器;并且目的地址自动增加偏移地址。根据data_sel信号,选择输出VC0还是VC1的数据和地址。

有一种特殊情况,数据地址是网络接口搬运控制寄存器(地址寄存器、源地址寄存器)的地址,那么该数据将会存入指定寄存器中。当数据搬运寄存器组配置完成后会启动数据搬运操作,也就是异地核读本地存储器操作。

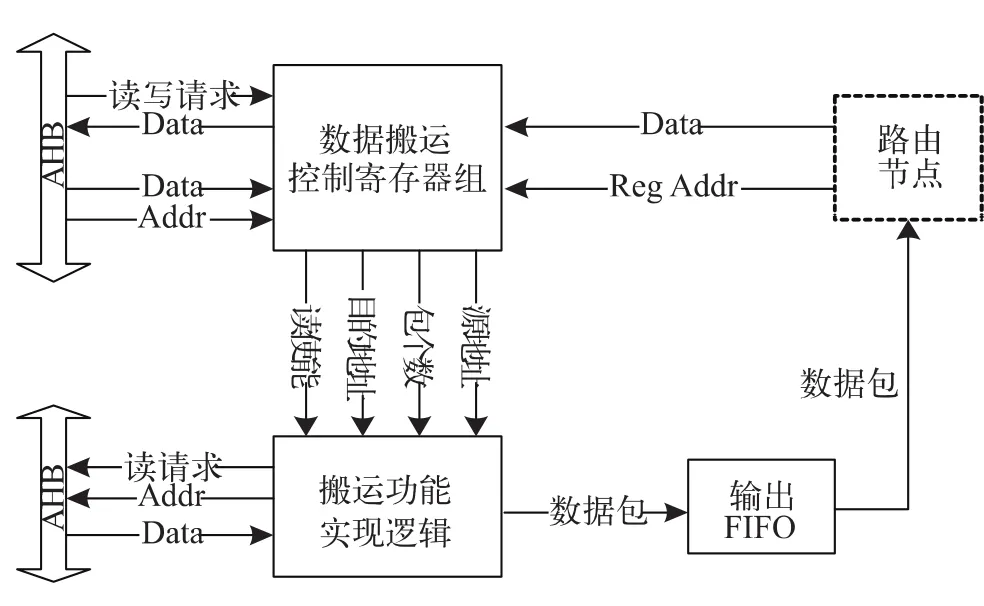

2.4 数据搬运逻辑

(1)配置数据搬运源地址寄存器,该寄存器中存的地址是本地存储器的本地地址;

(2)配置数据搬运目的地址寄存器,该寄存器中存的地址是全局地址;

(3)配置数据搬运控制寄存器,该寄存器由两部分组成,bit[31]是使能位,bit[9:0]是数据Flit个数位。

图7 数据搬运逻辑

整个数据搬运逻辑工作原理如下:本地DSP核通过AHB总线或者其他核通过路由传输数据,给数据搬运控制寄存器配置读取请求信息,使得网络接口作为Master通过AHB总线对本地存储器进行读操作。网络接口读取本地存储器中对应地址的数据,并将读取的数据发送到读功能实现逻辑,进行数据打包等一系列工作,并将数据包发送给FIFO,由其发送给路由。网络接口搬运过程中使用的FIFO和本地核写操作使用的FIFO是同一个,但是网络接口读操作优先级更高,如果网络接口正在进行读操作,Core数据写入操作将暂停,直到网络接口读操作完成才继续执行。

2.5 中断系统

网络接口完成数据传输任务后,通过中断系统通知本地DSP核,由DSP核产生相关响应。网络接口中包含中断信息输入寄存器、中断信息输出寄存器、中断使能寄存器、中断屏蔽寄存器、中断状态寄存器等寄存器。在网络接口进行数据传输前,需要预先配置好中断信息输入寄存器,中断使能寄存器和中断屏蔽寄存器。

网络接口发送数据后,会自动发送一个中断信息包,该包中含中断信息输入寄存器的内容。接收端网络接口根据中断信息包的内容及中断使能情况决定是否产生中断。

3 仿真验证

网络接口在完成RTL设计及模块级仿真后,集成到3×3二维mesh结构的NoC中,并完成系统级仿真验证。网络接口在NoC中主要负责本地系统和router之间的数据转换和传输,因此在系统仿真中主要测试在各核进行数据传输时,网络接口的数据转换和交换是否正常,包括其三种传输模式。表1是部分数据传输的testcase列表。

表1 testcase列表

以core0子系统向core4子系统进行数据批传输为例,这类操作需要本地DSP配置搬运源地址、目的地址以及搬运控制寄存器。配置完成后,使能网络接口开始数据传输,传输过程中DSP核不再参与。搬运操作使能后,将控制寄存器中的搬运Flit个数、搬运数据源地址基址、目的地址基址读出并存入读打包控制逻辑。打包控制逻辑会产生AHB读请求信号~hwrite_o和地址信号haddr_o,读取本地存储器数据;之后会根据目的地址信息,读取数据个数信息等在打包控制逻辑中生成路由能识别的Packet。数据打包完成后会通过FIFO16发送到Router0中。网络接口读取本地存储器的值并打包发送到router的波形如图8所示。

图8 网络接口传输数据

根据路由算法,Router0接收到网络接口发送过来的数据包后,解析数据包中的路由地址,把数据包发送到Router1中,Router1解析路由地址后,把数据包发送到Router4中。数据在各路由节点之间传输的波形如图9所示。Router4接收到数据包后,把数据通过其连接的网络接口传输到core4子系统中,该过程与网络接口的数据接收过程相同。

通过对比core0子系统和core4子系统中相关存储器中的值,可发现数据传输成功完成。

图9 Router之间数据传输

4 结论

本文所设计的网络接口支持单周期完成数据打包工作,并把数据包传输到路由节点中,只要路由节点中的FIFO不满,数据包就可以连续传输,保证了数据的传输效率。同时网络接口设计支持数据批传输,在需要大批量的数据传输时,由网络接口本身完成,不需要处理器参与,节省了处理器资源,提升了整个系统的处理效率。网络接口设计完成后,集成到整个NoC系统中并通过了系统仿真,确保了功能的正确性。

[1]段宜宾,王晓东,唐磊.片上网络关键技术及仿真方法研究[J].通信技术,2009,42(12).

[2]J Axel,T Hannu.Networks on chip[M].Kluwer Academie Publishers,2003:3-18.

[3]W J Dally,B Towles.Route packets,not wires:On-chip interconnection networks[C].In Design Automation Conf, 2001.

[4]朱小兵.片上网络路由算法研究[D].西安:西安电子科技大学硕士学位论文,2009.

[5]张香香.片上网络虚通道分配算法研究[D].西安:西安电子科技大学硕士学位论文,2012.

[6]杜高明,李向阳.基于多路径路由片上网络的低功耗联合编码电路设计[J].微电子学与计算机,2017,34.

[7]王璐.基于OCP-IP协议的片上网络接口设计[D].西安:西安理工大学硕士学位论文,2013.

Design of Network Interface Based on NoC

WANG Sheng,QU Lingxiang

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214072,China)

Compared with the bus architecture,Network-on-Chip has the advantages of supporting parallel communication,great scalability,regular structure,reusability and so on.The network interface of which the data conversion and transmission efficiency affect the work efficiency of the whole Network-on-Chip,is between processor cores and routing nodes on Network-on-Chip.This paper focuses on the structure of Network-on-Chip and elaborates the design and verification of a network interface.The NoC system studied in this paper adopts the structure of 3×3 two-dimensional mesh.The DSP core adopts AMBA bus structure.The router adopts packet switching mode.In order to realize the data conversion and exchange between the dsp and router,the network interface is designed.In order to improve the transmission efficiency,the network interface design supports data batch transmission.The batch transmission does not need the DSP core.That saves the processor resources.After the RTL design of the network interface,the simulation is carried out to ensure the correctnessofthe networkinterface.

Network-on-Chip;Networkinterface;router;packet

TN402

:A

:1681-1070(2017)09-0023-05

2017-6-19

王胜(1979—),男,江苏无锡人,硕士学历,主要研究领域为集成电路与系统设计。