基于TIADC架构的20 GSPS数字示波器研究

黄科文,刘益民,洪远泉

(韶关学院 物理与机电工程学院,广东 韶关512005)

数字示波器是随着数字集成电路技术的发展而出现的新型智能化示波器,已经成为电子测量领域的基础测量仪器.随着新技术、新器件的发展,它正向带宽化、模块化、多功能和网络化的方向发展.数字示波器的技术基础是数据采集,其设计技术可以应用于更广泛的数据采集产品中.但数字示波器本身存在失真比较大的缺点.由于数字示波器是通过对波形采样来显示,采样点数越少失真越大,通常在水平方向有512个采样点,受到最大采样速率的限制,在最快扫描速度及其附近采样点更少,因此高速时失真更大;测量复杂信号能力差,由于数字示波器的采样点数有限以及没有亮度的变化,使得很多波形细节信息无法显示出来,虽然有些可能具有两个或多个亮度层次,但这只是相对意义上的区别,再加上示波器有限的显示分辨率,使它仍然不能重现模拟显示的效果.

电子系统的飞速发展带动了信号频率的增加以及信号变得更加复杂,为了更好地检测此类复杂信号,宽带高采样率数字示波器便成为必须的一种仪器[1-2].另外,当代的电子系统中偶发信号更加普及,而且这类信号通常情况下会成为系统调试的关键因素,因此快速准确的获取此类型的偶发信号,提高测试的效率亦将成为数字示波器必须解决的问题[3].而解决这类问题的关键点在于在高采样率基础上对高速数据进行实时处理.TIADC(Time Interleaved Analog to Digital Converter)是指时分交替模数转换.采用TIADC构架便可以使高采样率得以实现[4].为了完成目前对复杂宽带信号的实时捕获及处理,本文设计了基于TIADC架构的20 GSPS(20 G高采样率)数字示波器系统.

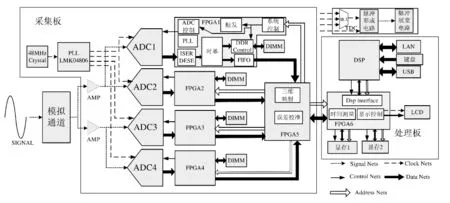

1 系统总体架构

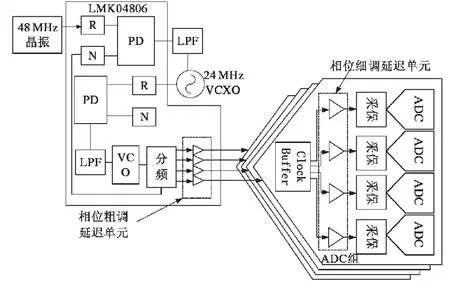

系统的硬件设计方案见图1,系统主体结构主要包括:调整通道、ADC(4片),FPGA1-FPGA4(用于采集接收到的数据并将采集到的数据进行存储)、FPGA5(用于波形的三维映射以及TIADC的误差校准)、DSP(Digital Single Processor,用于调控系统的运行同时会对数据进行后处理)、FPGA6(用于测量并显示时间)以及TDC(测量时间的电路).另外,DSP芯片上还外挂有USB、LAN、键盘以及外设电路.

进行调整后的信号会被分别送到4个ADC中,各个ADC采集到的数据分别送到对应的单独的FPGA,当数据输入到FPGA中后要先通过ISERDESE串进行转换并进行减速,这样高速数据的接收也就完成了,数据接收完成后数据在输入到时基电路中进行相应的抽取以及插值操作,然后这些数据将会被存储到FIFO[5-6],这时数据将会通过总线的形式输送进FPGA5对数据后处理以及波形三维映射,当数据转化为图形后将被写进FPGA6,这时波形将由显示与控制模块呈现到屏幕上.

图1 系统硬件原理图

获取多个FPGA的同步时钟相位关系后可以使得系统的并行FPGA采样数据实现准确的重组以及合并,这样把FPGA1~FPGA4的时钟输送到TDC电路[7-8],这样附属FPGA时钟同主FPGA时钟将会形成窄脉冲信号,然后信号会输送到时间展宽电路,然后信号将会被输送到FPGA的时间测量电路中进行计数,这样便可以得到同步时钟的相位关系.

2 采样时钟电路设计

系统采样率是20 GSPS,所以设计可产生低于50 ps延迟步进的锁相环.择取ADC为采样率是5 GSPS的 EV10AQ190[9],其输入的采样时钟频率为 2.5 GHz.

采样时钟抖动对信噪比SNR[10]的扰动:

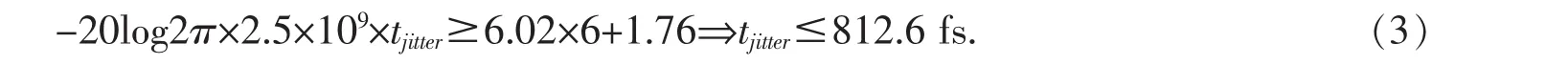

式中,fin及tjitter分别代表输入频率及抖动时间.

根据公式(1)能够获知,输入信号频率越高,SNR越小,采样时钟抖动越大,SNR越小.该设计系统输入信号频率区间是0~2.5 GHz,设计目标为低于500 MHz以及正弦输入时其有效位数ENOB[11]分别是6.5 bit左右以及高于6 bit.

要完成2.5 GHz正弦信号输入时ENOB高于6 bit,其采样时钟的抖动务必要符合:

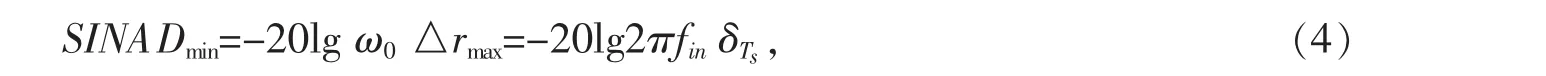

信纳比 SINAD[12]:

式中,ω0代表数字角频率,△rmax及δTs分别代表最大相对时间误差以及绝对误差.

当系统谐波失真相对来说很小时SINAD几乎等于SNR,所以时间误差要符合:

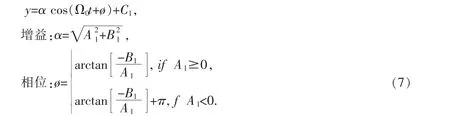

根据公式(5),系统运用的ADC要能够细调采样时钟延迟,步进是30 fs.综上所述,运用PLL完成倍频生成多路的2.5 GHz采样时钟,同时运用其内部的延迟以及ADC内部的采样时钟相位调节性能分别完成其采样延迟的粗略以及精细调整,其采样时钟原理图,见图2.

图2 采样时钟原理图

LMK 04806是能够把系统时钟的抖动缩减至最小的双环组成[13].PLL1及PLL2分别输入48 MHz晶振以及24 MHz的VCXO,同时PLL2的VCO生成的高频时钟通过分频模块获得4路2.5 GHz时钟,然后输送至延迟单元,4路时钟分别进行延迟后输送至4个ADC.2.5 GHz时钟进至ADC之后运用时钟BUFFER生成4路1.25 GHz的采样时钟,随之运用相位精细调整后再输送至4个ADC核.

3 算法设计

3.1 基于正弦的误差校准算法

设定正弦信号:

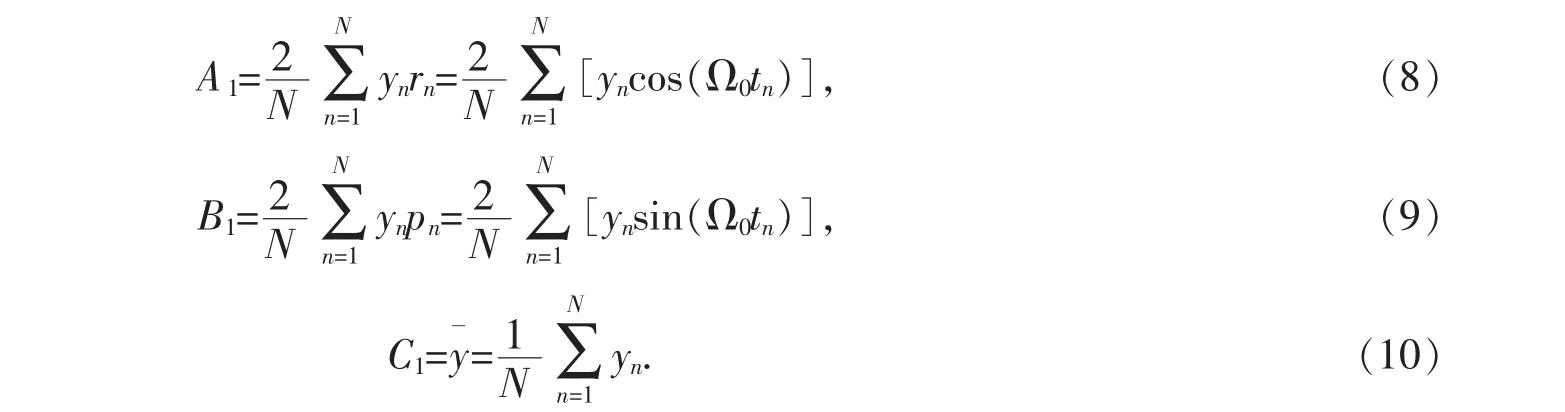

式中,Ω0代表正弦信号的角频率,同时为已知量,A1、B1及C1为系数.

将其转换成标准正弦信号:

设y1,y2,...,yN表示输入正弦信号时分别在t1,t2,…,tN时刻得到的N个实际采样点,则:

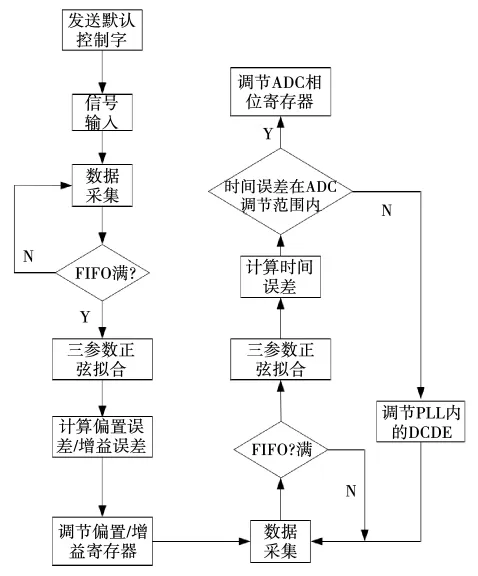

当处于校准模式时,输入正弦信号,随之系统开始采集,当检测到FPGA中的FIFO存储器溢出时表示完成一次采集.DSP顺次读取每个通道的采集数据,运用公式(8)~(10)运算获得参数A1、B1及C1.随之运用公式(7)运算获得全部通道的增益及相位,进而获得增益、偏置以及时间误差.运用ADC自带的模拟校准及PLL中的相位调节单元完成对误差的校正,其流程图见图3.

3.2 数据同步算法设计

为了确保数据同步,于完成ADC、PLL复位时以及FIFO写能开始时,恒定每个通道延迟Dk的差值,最终完成对数据的延迟以消除Dk的差值.假定两个FPGA因保存产生的延迟分别是D1及D2:

图3 基于正弦拟合的误差校准流程图

如果△D>0,那么表示FPGA2因保存产生的延迟低于小于FPGA1,进而需要完成对FPGA2的数据延迟△D.

完成数据延迟后,FPGA1及FPGA2因保存致使的总延迟一致,进而就能够完成对数据的重组.要得到每个FPGA之间的保存延迟,需完成复位状况筛选及延迟测量.

(1)复位状况筛选

复位状况关键呈现于ADC_PCLK间相位关系的改变,故需测量各ADC_RCLK间相位的时间间隔[14],把3个从FPGA中的ADC_RCLK输送至选择器,择取其中一个输送至脉冲形成电路和主FPGA的ADC_RCLK构成一个窄脉冲,随之把其进行展宽操作输送至FPGA6中的时间测量电路完成计数,最后依照计数值获得相位关系.

完成对ADC以及PLL复位后,运用TDC电路测量ADC_RCLK之间的相位,若其相位等于设定值,则复位成功,否则再一次发送ADC以及PLL复位指令直至相位等于设定值.

(2)延迟测量

保存延迟的测量需输入快沿信号[15],于DSP中完成每个通道采样数据上升沿间相位差△D检测:第一步搜索每个ADC采样数据经过上升沿中心的采样点位置,随之运算其位置差,各采样点是200 ps,则相位差:

式中,n表示位置差.

4 实验分析

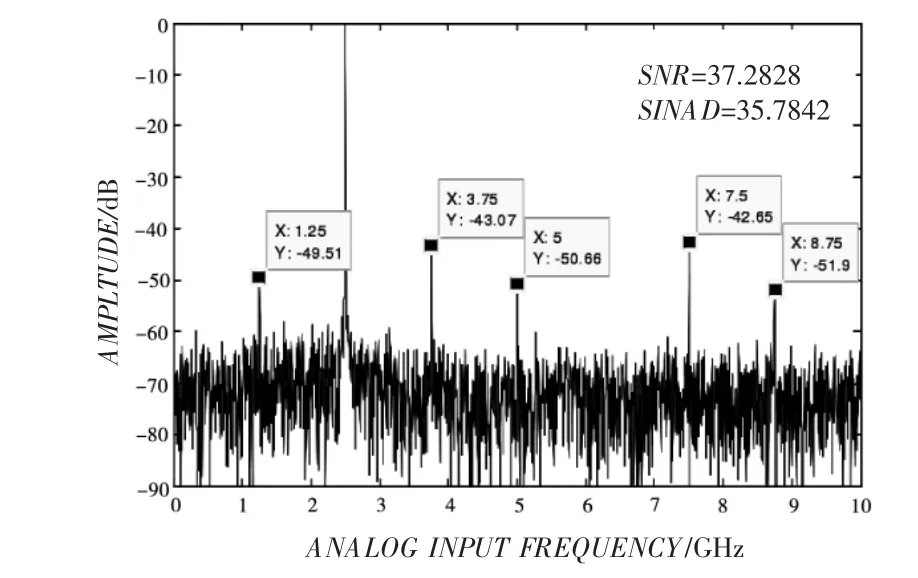

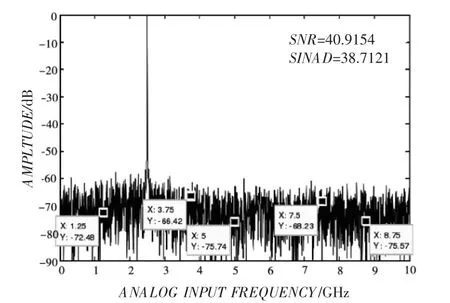

设计的20 GSPS数字示波器系统经过全方位的测试,验证了误差校准算法运用到实际的系统中可以实现的性能.设置采集板包括ADC(4个)和FPGA(5个).两对SMA连线将模拟信号传输进采集板,模拟信号通过一分二的模拟驱动电路转化成四路模拟信号分别输入到4个ADC中.DSP控制系统的运行,DSP控制总线以及数据总线通过连接器连接.另外,采集板上还拥有进行采样的时钟电路以及用于数据同步的TDC电路.运用正弦拟合算法来实现校准,进行校准前后的频谱图分别见图4和图5.

图4 校准前频谱图

图5 校准后频谱图

依照图5能够获知,校准后失真很大程度上得到削减,频谱失真也基本清除.校准前SNR为37.282 8 dB,校准之后SNR到达4 039 154 dB.SINAD也从35.784 2 dB相应的变成37.712 1 dB.

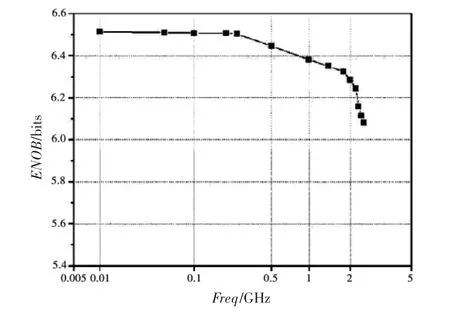

ENOB随频率改变的测试结果见图6.根据图6能够获知,信号频率低于500 MHz时,ENOB是6.5 bits左右,其关键是受到系统噪声的限制,500 MHz以及2.5 GHz位置时分别减小至6.446 bits以及6.285 bits,2 GHz至2.5 GHz频段ENOB减小的速度相对很快,关键是受到系统时钟抖动及校准精度的限制.总之在低于500 MHz以及500 MHz~2.5 GHz正弦输入时其有效位数ENOB分别是6.5 bit左右以及高于6 bit,符合设计目标.

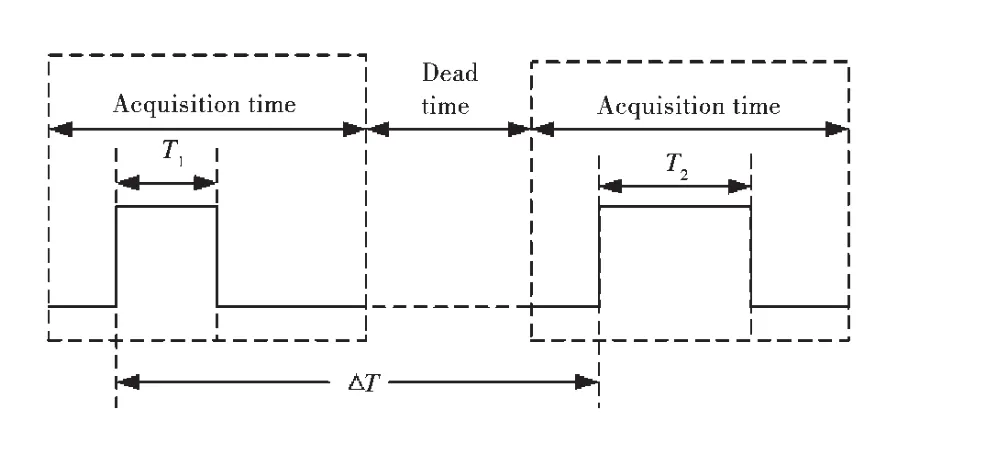

运用双脉冲法以完成对系统捕获能力的评估见图7.

图6 系统ENOB随频率改变曲线

图7 双脉冲法原理

确保脉冲宽度T1及T2全部展现于示波器屏幕,调整触发电平至可引起正常触发的合适位置,输出一次双脉冲.若两个脉冲都可以被捕获,那么缩减减其间隔△T直至第二个脉冲无法被捕获,进而得到两个脉冲的最小时间间隔△Tmin,则最高捕获率WCR:

经过测试该系统能够得到的△Tmin是0.16μs,WCR=6.25×106wfms/s,满足要求.

5 结语

基于TIADC架构设计了20 GSPS的数字示波器,完成了对低抖动、相位可调的采样时钟设计、多片ADC间采样数据保存同步以及误差校准算法设计.最后对系统进行实验分析,其结果表明:校准后频谱失真基本得以消除,校准前后SNR及SINAD分别从37.282 8 dB、35.784 2 dB提升至40.915 4 dB及38.712 1 dB,另外在低于500 MHz以及500 MHz~2.5 GHz正弦输入时其ENOB分别是6.5 bit左右以及高于6 bit,符合设计目标其表现出良好的性能.不足之处是TIADC系统存在的误差可能会影响系统的整体性能.