薄层高阻硅外延制备工艺研究

傅颖洁,李明达

(中国电子科技集团公司第四十六研究所 天津300220)

0 引言

轻掺硅外延层/重掺衬底结构作为现代电力电子器件的关键支撑材料,通过外延生长可以改善原始衬底的晶体质量,显著提升电参数的一致性,用作有源器件的核心工作区[1]。重掺态衬底至轻掺态外延层的结构,电阻率数值需爬升至少2个数量级。基于器件耐压、漏电等因素考虑,常规外延层厚度的数值通常会比电阻率数值高至少1个数量级[2]。因此,随外延层的沉积,电阻率有足够的时间从重掺态上升到稳定的轻掺态,工艺实现相对容易。但在特殊应用领域,迫切需要研发电阻率数值接近甚至大于厚度数值的轻掺硅外延层/重掺衬底结构,即薄层高阻硅外延层。由于所需外延厚度较薄,反应时间被严重缩短,此时采用常规外延工艺获得的电阻率在有限的反应时间内难以稳定上升到预设值,极易受到自掺杂的严重影响,结构难以实现分布平坦化,工艺稳定性较差,最终导致国内技术指标迟迟无法达到器件设计要求,与国外同类产品存在显著差距[3]。

基于外延生长因素的分析,解决薄层高阻外延生长工艺参数均匀性及稳定性的难题,尤为关键的是生长过程中对各类自掺杂扰动因素的有效抑制,需要在短时间迅速提升外延层生长过程中电阻率的爬升速率,保证有效的外延层厚度。本文通过重点研究生长温度、本征层覆盖等关键工艺条件对外延层自掺杂扰动的作用机制,设计低温生长、本征层覆盖、氢气高温烘焙等工艺手段,实现了良好的薄层高阻外延层均匀性等综合指标的控制能力,材料产出水平可以满足设计和使用要求。

1 实验设备

实验采用常压平板式外延系统,由石英钟罩、圆盘状石墨基座、高频加热线圈等组成。石墨基座表面设置8个片坑,每个片坑内可放置直径150 mm 的硅单晶抛光片,在外延层沉积过程中基座保持顺时针转动,使各片生长的流场条件保持均匀。外延炉腔体顶部安装有测温探头,可以实时监控硅片在整个工艺过程中的温度。

2 外延生长原材料

所用硅单晶抛光片规格为N 型<100>晶向,厚度为(625±15)μm,电阻率为0.01~0.02 Ω·cm,衬底背面包覆4500 Å 的SiO2背封层。所制硅外延层目标厚度为(12±2%)μm,电阻率为(28±2%)Ω·cm,其特征电阻率的数值已经超过厚度数值2倍的薄层高阻外延,片内距边缘6 mm 的厚度不均匀性要求低于2%,电阻率不均匀性要求低于2%。

薄层高阻硅外延层因自身参数特征,均匀性和生长质量的要求控制更为困难,反应过程中对各类杂质的扰动更为敏感,气源纯度要求更高。实验采用纯度高于4 N 的SiHCl3作为硅外延层的生长原料,采用纯度高于6 N 的H2作为反应气体,生产过程中工艺载气携带生长原料和磷烷掺杂气源从生长腔体的一端通入,在化学反应中将SiHCl3还原为Si原子后进行外延层的沉积。

3 外延材料性能表征

硅外延层制备完成后需要立即进行厚度和电阻率参数的测试,其中外延层的厚度由Nicolet IS10型傅里叶变换红外光谱测试仪表征。外延层电阻率通过MCV-530L 型自动汞探针电容-电压测试系统表征。厚度和电阻率采用标准的5点测试法,即分别取中心点和2条垂直直径距边缘6 mm 的位置。测试结果以硅片主参考面位置为上点,采用标准偏差(STD%)表征均匀性的管控水平。

4 结果与分析

4.1 厚度均匀性控制研究

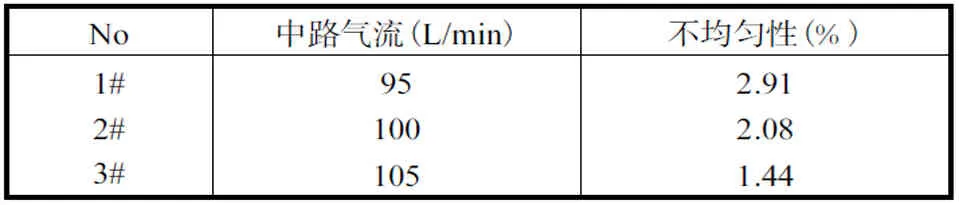

H2作为硅外延反应的反应气体和原料运输载气,外延层厚度均匀性主要由H2的流量和流速分配方式决定,对于本实验所用的PE-3061D平板式外延系统,腔体左侧设有3路气体输运通道,即中心区域设置气体通道,左右两侧再设置2路气体通道。通过调节进气流量阀的开合度,改变进气流量和流速的分配比,从而对外延流场状态进行控制。实验以中间气路通道的流量为设定变量,此时两侧的气流量可自动变更为(总工艺气流量-中路气流量)/2。本文对中间气路通道的H2流量与外延层厚度均匀性的作用关系如表1所示。

H2流量在各个进气口的分配组合影响SiHCl3在反应室内的分压,进而影响了片内各局域地区生长速率的分布。表1结果显示出随着中路进气流量的持续增大,外延层厚度在片内的分布特征为:片内5点厚度不均匀处对应呈现出先减小后增大的趋势。此外,当中心区域进气流量增长至105 slm(L/min,标准状况)时,所得外延层厚度不均匀性<1.5%,已经可以实现均匀的流场反应结构。

表1气流分布特征与外延薄膜厚度均匀性的关系Tab.1 Relationship between flow distribution and epitaxial film thickness uniformity

4.2 电阻率均匀性控制研究

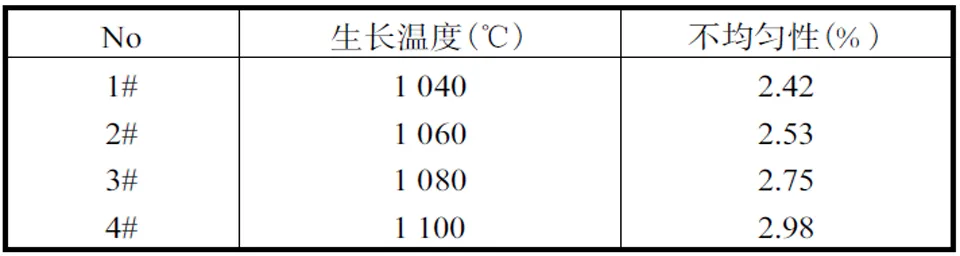

对于薄层高阻外延层,其与衬底的电阻率相差至少2个数量级,在较短的反应时间内易受各类自掺杂扰动影响,相较常规外延层规格更加难以控制均匀性,其中生长温度直接与吸附于石墨基座、石英腔体系统以及重掺衬底内所含杂质的挥发状态相关。实验中首先将生长温度设定为1040~1100℃,对应的电阻率均匀性结果如表2所示。实验结果表明随工艺温度的逐渐升高,外延层电阻率也逐渐升高,并伴随着均匀性逐渐变差的趋势,这可归因于高温下主动掺杂掺入效率降低,硅外延层中心区域的阻值因而升高,但同时边缘位置受杂质的自挥发效应进一步加强,高温下挥发杂质滞留于反应气氛中而无法带出腔体,随后在外延层生长过程中重新随硅原子掺入,从而增加了额外掺杂效率,造成外延层边缘电阻率的分布不均,均匀性明显变差。因此,在保证外延层表面质量的前提下,需要采用外延低温生长工艺。基于实验结果,最终选用1040℃的生长温度,可兼顾表面质量和减弱边缘区域自掺杂效应的工艺实验设计 目标。

表2 生长温度对薄层高阻外延电阻率均匀性的影响Tab.2 Effect of growth temperature on epitaxial resistivity uniformity

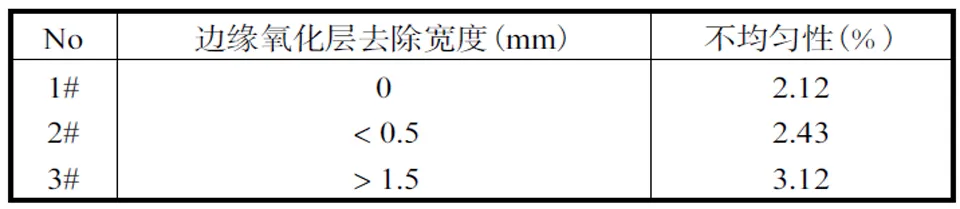

表3的实验结果表明,衬底背面的SiO2背封层边缘氧化层去除宽度直接影响衬底边缘裸硅位置杂质的挥发效果,进而影响外延薄膜电阻率均匀性。最初采用的硅衬底片边缘氧化层的去除宽度>1.5 mm,边缘裸露的硅受热挥发现象影响,导致外延薄膜边缘位置电阻率数值偏低,电阻率不均匀性>3%;改为边缘氧化层全部保留的衬底后,杂质自挥发程度明显减轻,但是,边缘倒角面残留的SiO2氧化膜因外延过程Si置换作用出现多晶颗粒并随沉积作用而逐渐长大,在后续器件工艺过程中极易自行掉落,难以满足流片要求。综合以上2种措施,确定采用背面边缘氧化层去除宽度<0.5 mm 的硅衬底片,缓解了杂质自挥发效应,可以兼顾衬底自掺杂抑制及保证边缘光滑度的要求。

表3衬底背封层边缘去除宽度对应的外延薄膜电阻率均匀性Tab.3 Uniformity of epitaxial film resistivity corresponding to removal width of backside edge oxide

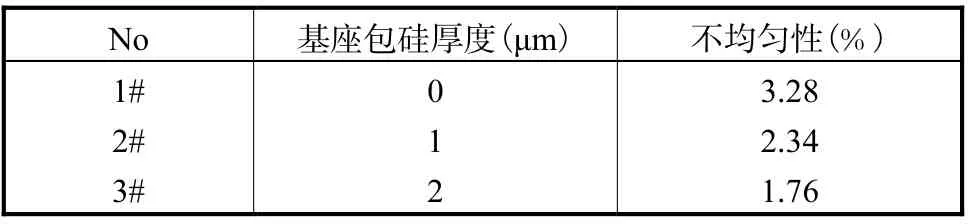

石墨基座作为硅外延薄膜的生长载体,若在反应过程中释放杂质将留存于滞留层中,后续在外延生长过程中混入生长气氛将直接影响硅外延薄膜边缘位置的电阻率均匀性。本文在衬底装片前预先采用高纯度高流量SiHCl3给基座表面包覆一定厚度的无掺杂多晶硅,对表面杂质实施掩蔽,但是一旦包硅厚度过度,将容易使衬底片背面吸附过多的硅颗粒,并导致背面平整度变差。实验中设计采用0~2 μm 的基座包硅厚度,其对外延电阻率均匀性的影响效果如表4所示。

采用无包硅条件生长的外延薄膜受自掺杂影响非常严重,片内边缘电阻率严重偏低造成不均匀性高于3%。当包硅厚度设计为2 μm 时,在掩蔽基座杂质的同时,基座上沉积的多晶硅层通过质量转移效应封闭衬底边缘的裸露硅层,显著减缓了杂质逸出,使边缘均匀性得到改善,获得的外延薄膜电阻率不均匀性在2%以下。

表4 基座不同预包硅厚度对应的外延电阻率均匀性Tab.4 Uniformity of epitaxial resistivity with different thicknesses of pre-coa ting silicon on substrate

5 结论

本文在常规外延工艺的基础上,根据重掺衬底薄层高阻硅外延片参数控制的特点,综合运用低温本征、基座包硅等工艺,成功完成了对外延形貌、厚度及电阻率均匀性参数的优化控制。采用改进后的外延工艺方法,外延层的厚度片内一致性指标均优于1.5%,电阻率片内一致性指标均优于2%,达到了一致性指标的要求。