一种大带宽多通道信号处理模块设计与实现

万相宏,肖国尧,全英汇

(西安电子科技大学 电子工程学院,陕西 西安 710071)

0 引言

近年来,随着雷达技术的快速发展,多通道高速信号处理的应用在雷达信号处理领域越来越广泛。无论是对于MIMO(Multiple Input Multiple Output)雷达,还是相控阵和数字阵列雷达,都需要多个发射和接收通道进行信号传输和处理。为了满足雷达信号处理过程中的相关功能,信号处理机多采用FPGA,DSP,FPGA+DSP,FPGA+CPU以及FPGA+ARM等架构进行开发设计[1]。文献[2-4]讨论了基于DSP的多通道雷达信号处理机设计和实现方法,采用多核通信、多核同步的方法对雷达信号处理。文献[5-6]分别讨论了基于FPGA的雷达阵列信号处理机的设计和雷达信号采集系统设计方案。文献[7-8]提出了基于FPGA+DSP的雷达信号处理机的设计方案和系统实现。文献[9]提出了一种数字阵列信号处理单元的设计方案。

针对不同的应用场景,大多采用分立的模拟数字转换器(Analog to Digital Converter,ADC)、数字模拟转换器(Digital to Analog Converter,DAC)以及射频前端相关器件进行雷达信号的发射和接收,相关器件大多只能满足特定功能和技术的使用,且当信号通道数增多时,分立器件所占用的空间变大、在印制板上走线引出难度增大,同时还需要考虑通道间的串扰问题,因此整个系统的体积也会相应增大。此外,当不同的系统所需要的通道数和工作频带不同时,需要对系统进行重新设计或对原系统进行相应的修改变动。面对当前日新月异的应用场景和信号处理新技术,通用化和规范化的信号处理设备无疑可以缩短新技术的研发验证周期,确保更快地进行技术验证或投入实际应用。

在雷达信号处理的应用场景中,无论何种架构设计,都在不断致力于将信号处理功能向标准化、小型化、低功耗、高集成的方向发展。

针对上述问题,面向雷达信号处理应用领域,特别是MIMO、数字阵和相控阵的信号处理应用,研制一种低功耗、低延迟、灵活可配置且具有标准化、通用化、可扩展能力的多通道数字信号处理机具有重要意义。本文提出了一种多通道通用信号处理机设计与实现的方案,以Xilinx公司的Zynq UltraScale+ RFSoC作为核心芯片,采用3U VPX标准架构与模块化设计,覆盖DC-6 GHz工作频带,同时支持软硬件动态配置功能,该模块适用于数字阵列雷达、相控阵和MIMO雷达等不同体制雷达的信号处理系统。

1 硬件架构设计

多通道信号处理机架构如图1所示。系统主要由Zynq UltraScale+ RFSoC芯片、时钟芯片、晶振、电源芯片、存储器芯片、射频接口、以太网芯片及VPX接口等构成。并采用3U VPX的标准设计架构,模块采用导冷结构,同时兼容风冷散热,模块使用灵活、便捷。

图1 多通道信号处理机架构Fig.1 Multi-channel signal processor architecture

硬件系统实物设计的正反面如图2所示,实际使用时去除工艺边即为标准的3U板卡。

(a) 板卡正面

(b) 板卡背面图2 板卡实物Fig.2 Board picture

传统的射频收发系统主要有超外差接收、零中频接收和低中频接收3种架构,随着ADC和DAC性能和工艺的提升,数字信号已经可以直接采样成射频信号进行发射接收。Zynq UltraScale+RFSoC系列是Xilinx公司采用16 nm工艺的片上射频系统,SoC中集成了高性能的ADC和DAC,芯片集成了具有直接RF采样能力的数据转换器,在片内集成高速数据传输链路,芯片可支持采样率高达5 GS/s的14位ADC和10 GS/s的14位DAC进行直接RF采样,模拟输入/输出带宽高达6 GHz[10-12]。信号发射时,由ZYNQ的PL(Programmable Logic)部分驱动片上集成的DAC,产生中低频的基带信号,然后配置片上射频前端组件,经过一级或者多级变频处理通过天线发射出去。信号接收时,信号经过一级或者多级的变频处理,传输到片上集成的ADC进行采集,再传输到ZYNQ的PL端进行数据的处理。

芯片还集成数字下变频(Digital Down Conversion,DDC)、数字上变频(Digital Up Conversion,DUC)等功能,使用方便、灵活,且与传统的分立芯片系统设计相比,采用该芯片设计的系统,许多模拟组件可以由数字部分进行替代,可实现50%~75%的功耗、尺寸削减,可大幅降低硬件成本,从而实现更小型化的射频信号处理系统。外部输入的高速信号经过片上ADC和DAC数据转换器的处理,使得ZYNQ的PL端可在中低速时钟情况下,实现对高采样率的ADC和DAC的数据处理。相比传统的射频收发系统,省去了许多模拟组件,在系统设计时只需考虑片上ADC和DAC的通道间的信号完整性与隔离度以及时钟和各个通道间的隔离度,极大地降低了芯片已覆盖频段的射频系统的硬件设计难度,减小了系统的工作量,缩短了整体系统的研发周期。

使用RFSoC芯片进行射频直接采样,系统频段覆盖广,可在0~6 GHz灵活可配置,可针对具体需求选择相应的频段进行搭配选择,8个通道可配置不同的频段独立使用,每个通道所配置频段,可根据实际应用同时接收或者分时接收。

射频接口采用IPEX封装接口引出发射和接收通道信号,射频部分采用机械盲埋孔设计,增加走线空间,减小了PCB的体积,控制通道间的信号串扰和隔离度。由于射频系统的高度集成化,不用考虑RFSoC芯片内部的通道隔离度,只需将PCB上的各个收发通道间隔离度控制在合理范围内,即可反映系统的各个通道的隔离度。

如图3所示,为本文所述系统的时钟网络结构,系统的时钟部分采用LMK04828芯片和GMD946芯片,LMK04828时钟芯片可实现超低噪声,且符合JESD204B标准。GMD946时钟芯片是超快型时钟扇出缓冲器,输出时钟低抖动。使用LMK04828芯片为系统提供参考时钟,并且预留同步时钟输入输出端口,支持多板间同步,提高了系统的可拓展能力。LMK04828时钟电路同时支持本地板载晶振时钟输入,也支持外部接入差分或者单端时钟输入。GMD946芯片为RFSoC的高速串行总线以及PL端提供参考时钟输入。

图3 时钟网络结构Fig.3 Clock network structure

系统的电源部分主要采用开关模式降压型 DC/DC稳压器LTM4644和LTM4630。2款芯片内置了开关控制器、功率场效应管和电感器等元件。使用LTM4644和LTM4630给RFSoC的各个部分进行供电,通过LTM电源芯片的EN和PGOOD管脚信号,对特定电源上电顺序进行控制。

在RFSoC的PL端和PS端分别挂载一片存储器芯片。为了实现模块的小型化,满足高存储容量需求,硬件设计中采用的存储器芯片为大容量DDR3存储器芯片,单片DDR3芯片的存储容量为512 Mb×72 bit,等效9片512 Mb×8 bit DDR3的存储容量,读写速率高达1 866 Mb/s,支持ECC校验,同时内部集成了ODT终端电阻、参考电压电路等。在保证存储容量的情况下大大减小了体积,提高了系统集成度。

通过VPX连接器引出符合VITA46标准的对外信号引线,包括高速串行总线、LVDS信号线、PS_MIO、PL_IO以及LMK04828的时钟相关信号线。其中高速串行总线的每个通道的线速率高达16 Gb/s,解决了高速数据传输问题。多块板卡或不同板卡可以通过高速串行总线进行数据交互,同时可以通过VPX进行拓展板卡功能。

系统整体的布局设计,按照模块功能、信号速率以及信号类型进行布局规划,硬件架构框图基本依据实际布局进行绘制。首先对各个模块电路进行布局,然后根据信号类型和信号速率进行模块放置。RFSoC芯片位于板卡中心;电源模块靠近VPX供电引脚进行放置;存储器芯片靠近主控芯片,放置在主控芯片上方;LMK04828和芯片参考钟的晶振放置在板卡右上方;以太网模块放置在左上方;射频收发通道部分放置在芯片的右侧进行正反贴。对于射频收发通道,划定模拟区域与数字区域进行隔离,严格分离模拟和数字信号。对于LMK04828芯片,布局完成后周围留一定余量空间做包地处理,用于减小时钟信号的串扰。

系统板卡PCB如图4所示,为了降低干扰,在PCB设计时适当增加了中间层来进行屏蔽,降低信号间的交叉干扰。最终设计的PCB板共24层,第1,3,5,7,9,14,16,20,22层为信号层,第2,4,6,8,9,10~13,15,17,19,21,23层为电源或地层,采用对称设计。板厚为2.85 mm,为满足高速PCB的传输需求,选用M6G的高速板材加工设计,M6G板材损耗因子为0.005。

图4 系统板卡PCBFig.4 System board PCB

2 关键信号设计与仿真

对于高速信号,特别是高速数模混合信号,信号完整性、隔离度一直是设计的重点。本系统中高速信号的设计与处理,参考相关文献的设计和改进方法对高速信号进行设计。文献[13-14]介绍了高速PCB设计中信号完整性分析和硬件系统设计中的应用分析。文献[15]介绍了射频通道隔离度的影响因素,并提出了2种改进措施。文献[16]从板材、铜箔等方面介绍了高速PCB设计的优化方法。

射频的发射和接收通道设计是系统PCB设计中需要重点关注的部分。将射频收发通道放置在靠近RFSoC片上ADC和DAC的一侧,尽量缩短射频收发通道的布线长度。同时,为了保证通道间的隔离度,降低各个通道间的串扰,将ADC和DAC进行隔离处理,对于ADC和DAC各个通道的射频接口也进行隔离处理,图5为射频收发通道的PCB处理,图5左边正反表贴的8个通道为射频接收ADC通道,右边正反表贴的8个通道射频发射DAC通道。

图5 射频收发通道PCBFig.5 RF transceiver channel PCB

布线设计时使用圆弧走线,同时在射频接口的周围增加地孔隔离,并进行盲埋孔设计,可以在一定程度上改善串扰。经过仿真测试,对顶层的射频收发通道增加L1~L9层的盲埋孔,对改善串扰的效果最优;对底层的射频收发通道增加L14~L24层的盲埋孔,对改善串扰的效果最优。为了保证发射和接收各个通道的一致性,使用蛇形走线和圆弧布线的方式,确保高速信号的传输线等长。

差分信号大多采用45°转角布线的方式,以满足等长等距的要求。对时钟信号、高速总线信号和LVDS信号等信号提供专门的布线层,以保证其最小的回路面积。该设计中,ADC和DAC的时钟信号线在2个布线层进行布线设计,高速串行总线信号和LVDS信号与ADC时钟信号共用一个布线层。同时,时钟线和高速信号线用地线进行包围,并在地线周围打地孔减少分布电容,从而减少串扰。

此外,在PCB设计时检查多余焊盘并将其删除,可以减小信号反射。布线时,保证线间距不小于走线的线宽,并尽可能增大了走线之间的距离,可以减小串扰。同时为保证高速信号质量,减小过孔多余残桩对高速信号的影响,设计时对高速信号的过孔进行背钻处理。

完成系统的PCB设计后,对系统的ADC和DAC通道信号之间的串扰及隔离度进行仿真;对系统的时钟与ADC和DAC之间的串扰及隔离度进行仿真,并简要分析仿真结果。

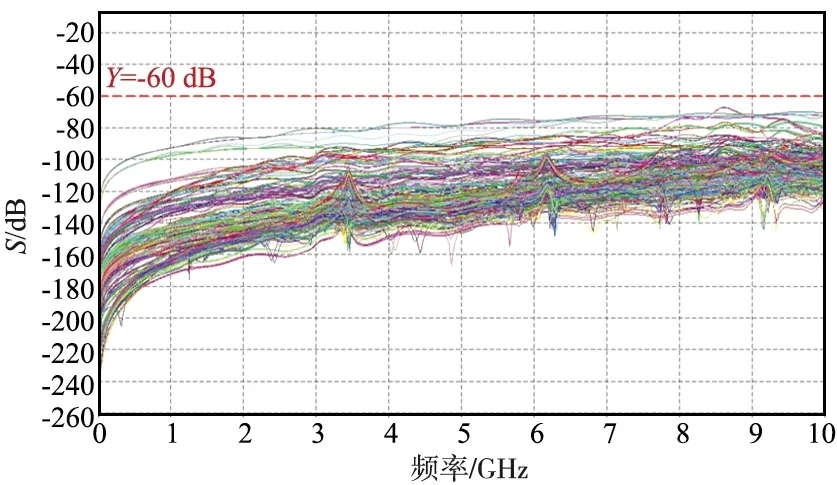

对ADC输入通道和DAC输出通道的串扰和隔离度进行仿真,选择ADC某一通道输入信号或者DAC的某一通道输出信号,信号带宽9 GHz,测试其他通道的隔离度情况。ADC各个通道之间的隔离度结果如图6(a)所示,DAC输出各个通道之间的隔离度结果如图6(b)所示。

对时钟与ADC通道和DAC通道之间的串扰及隔离度进行仿真。将时钟信号输入,测试ADC各个通道间和DAC各个通道间的隔离度情况。时钟对ADC之间的隔离度仿真结果如图6(c)所示,时钟对DAC之间的隔离度仿真结果如图6(d)所示。

(a) ADC通道隔离度仿真

(b) DAC隔离度通道仿真

(c) 时钟与ADC隔离度仿真

(d) 时钟与DAC隔离度仿真图6 隔离度仿真Fig.6 Isolation simulation

从仿真分析图中可以看出,在9 GHz带宽范围内仿真输入信号,ADC和DAC的各个通道之间的串扰均小于-60 dB;将时钟输入,ADC和DAC的各个通道之间的串扰均小于-60 dB。满足了系统设计预期的通道隔离度和串扰要求,保证了ADC和DAC多个通道同时工作时的信号质量。

经过对关键信号的PCB设计以及相关优化,并由仿真测试结果可知,当前设计满足期望的串扰和隔离度目标范围,即ADC和DAC各个通道之间的串扰均小于-60 dB;时钟与ADC和DAC各个通道之间的串扰均小于-60 dB。

3 关键指标测试

本节首先对系统进行ADC和DAC的串扰和隔离度测试,然后对ADC和DAC性能进行测试,并分析该系统的ADC和DAC通道的性能。

对系统中的ADC和DAC进行串扰和隔离度的测试,测试方法和仿真设计时保持一致,选择ADC某一通道输入信号或者DAC的某一通道输出信号,测试其他通道的隔离度情况。测试结果如表1所示。测试结果显示,DAC各个通道之间的串扰均小于-70 dB,ADC各个通道之间的串扰均小于-60 dB。达到预期的仿真设计效果,通道间的隔离度良好。

表1 通道隔离度测试Tab.1 Channel isolation test

根据文献[17-18]介绍的高速ADC性能参数的测试相关方法,进行ADC和DAC性能测试。ADC的主要指标分为静态指标和动态指标,同时随着半导体工艺的发展,晶体管最大频率越来越高,相比传统的ADC指标,噪声频谱密度(Noise Spectral Density,NSD)、三阶互调失真(Third-Order Intermodulation Distortion,IM3)、相邻信道泄漏比(Adjacent Channel Leakage Ratio,ACLR)更能表征射频采样数据转换器的性能。根据现有的测试环境,主要对系统中ADC的动态指标的相关参数和噪声频谱密度(NSD)进行测试。

ADC的采样频率设置为4.8 GS/s,不做抽取处理,计算点频信号100,500,1 000,1 420 MHz的无杂散动态范围(Spurious Free Dynamic Range,SFDR)、信噪比(Signal to Noise Ratio,SNR)、信噪失真比(Signal-Noise Distortion Ratio,SNDR)、有效位数(Effective Number of Bits,ENOB)以及NSD,测试结果如表2所示。

表2 ADC通道性能测试Tab.2 ADC channel performance test

表2中的数据是将ADC采集后的数据导入到Matlab中,进行相关参数计算分析得出,图7为ADC采集的信号频谱测试图。

(a) 100 MHz信号频谱图

(b) 500 MHz信号频谱图

(c) 1 000 MHz信号频谱图

(d) 1 420 MHz信号频谱图图7 ADC信号频谱图Fig.7 ADC signal spectrogram

使用该系统的ADC采集信号源输出的100,500,1 000,1 420 MHz信号,测试使用的信号源谐波较大,信号源的谐波会影响ADC性能参数的测试结果,对相关参数测试的影响较大,实际性能要优于本文测试环境下的相关测试指标。

对DAC的各个通道进行性能测试,主要测试DAC的SFDR和线性调频信号的平坦度。DAC的采样频率设置为9.6 GS/s,不做插值处理,输出6个点频信号,将信号接入频谱仪中,进行频谱分析并计算相关性能指标,测试结果如表3所示。

图8为DAC输出信号频率为1 GHz和1.5 GHz的信号频谱测试图,从测试图中可看出,谐波的大小影响了DAC的SFDR等关键指标,在实际应用中,可根据具体的应用需求,在需要的频带周围使用带通滤波器,进一步提升DAC的工作性能,从而更好地适配实际的应用环境。

(a) 1 GHz信号频谱图

(b) 1.5 GHz信号频谱图图8 DAC信号频谱图(1)Fig.8 DAC signal spectrogram (1)

使用DAC输出线性调频信号,将输出信号接入频谱仪,进行线性调频信号的平坦度分析和计算。在当前测试环境下,线型调频信号在0-3Fs/4的频带范围平坦度均小于±2 dB,其中在0-Fs/4的频带范围输出信号的平坦度小于±1.5 dB。图9为DAC输出的带宽500 MHz、中心频率1 GHz和带宽1 GHz、中心频率为3.6 GHz的线型调频信号。经测试分析和计算,带宽500 MHz、中心频率1 GHz的线型调频波信号平坦度小于±0.8 dB,带宽1 GHz、中心频率3.6 GHz的线型调频波信号平坦度小于±1.5 dB。

(a) 带宽500 MHz信号频谱图

(b) 带宽1 GHz信号频谱图图9 DAC信号频谱图(2)Fig.9 DAC signal spectrogram (2)

经过测试分析,该系统的DAC和ADC串扰、隔离度符合预期的设计效果,能正常满足RFSoC的工作需求;RFSoC内部集成的DAC和ADC的性能良好,可满足多种复杂的雷达信号处理的应用需求。

4 应用场景测试

该系统的应用广泛,可以满足多种雷达信号处理的应用需求。本节结合实际项目的应用背景,使用该系统进行多通道模拟间歇采样转发干扰的测试。

使用该处理机的两路ADC和四路DAC进行两路模拟间歇采样转发干扰的应用。系统测试环境如图10所示,使用电源用于板卡供电,示波器、频谱仪和信号发生器等仪器用于测试板卡的相关数据,笔记本电脑用于程序烧写和板卡状态监视。

图10 系统测试环境Fig.10 System test environment

使用两路DAC进行发射模拟的雷达信号,两路ADC进行切片采样,再通过两路DAC将间歇采样后的信号进行转发,并将间歇采样前后的信号进行脉冲压缩处理,进行对比分析。

对ADC和DAC采集转发干扰进行延迟分析,使用Matlab程序产生一个雷达信号波形数据,将波形数据存储在ROM中,通过DAC输出信号。并将该信号接入ADC通道,把采集到的数据保存,进行延时分析。实验测试得出两路ADC和DAC进行采集转发的延时均在110 ns以下。

将测得的数据导入Matlab进行分析,信号产生和采集延迟分析如图11所示。分析可知,系统中相应通道的ADC采集到DAC输出的信号延时为105.5 ns。

图11 模拟雷达信号产生和采集延时分析Fig.11 Analysis of the generation and acquisition delay of analog radar signals

对其中一路DAC模拟的雷达信号以及切片采样后转发的雷达信号进行分析,将DAC模拟产生的雷达信号和ADC间歇采样处理后的雷达信号接入示波器,并在软件中抓取相应的DAC通道数据导入Matlab中进行时频分析。

DAC的时频分析如图12所示,图12(a)表示模拟雷达信号产生和间歇采样后的雷达信号的时域图,图12(b)和图12(c)表示模拟雷达信号产生和间歇采样后的雷达信号的频域图。在该模拟间歇采样转发测试中,对DAC输出的模拟雷达信号进行间歇采样,每个脉冲采样4次,采样后进行信号转发。

(a) 间歇采样前后时域图

(b) 原始信号频域图

(c) 间歇采样后频域图图12 间歇采样时频分析Fig.12 Time-frequency analysis of intermittent sampling

图13为其中一路信号的经过间歇采样前后的信号脉冲压缩结果,图13(a)为模拟雷达信号在未进行间歇采样处理的脉冲压缩结果;图13(b)为模拟雷达信号在经过间歇采样处理后的脉冲压缩结果。

(a) 原始信号脉冲压缩图

(b) 切片转发后脉冲压缩图图13 转发输出的雷达信号脉冲压缩结果Fig.13 Radar signal pulse compression result of forwarding output

经过切片采样的模拟雷达信号,转发输出之后可以使信号产生径向对称的假目标信号,假目标的功率由对称中心向两边衰减,且衰减速度较快。从上述测试可知,该系统可以很好地对模拟雷达信号进行间歇采样处理,并且切片采样处理后的信号能较好地产生关于主峰对称的假目标信号。

5 结束语

本文提出的一种多通道通用信号处理机设计与实现的设计方案,提高了系统的集成度,采用3U VPX标准架构设计,提高了模块的通用性和实用性,可满足多种雷达的信号处理系统。通过对硬件的仿真测试以及板卡性能的相关指标测试,验证了本模块设计具有优越的性能。通过举例多通道间歇采样转发的应用实例,验证了系统在多通道信号处理应用的可行性。上述测试和应用实例综合验证了本文的多通道通用信号处理机设计的可靠性和可行性。

本文介绍的多通道信号处理机不止局限于上述应用实例,在数字阵列雷达、相控阵和MIMO雷达等不同体制雷达的信号处理系统都有很强的使用价值。可以快速部署多通道的信号处理系统,降低系统方案的设计成本,缩短系统验证的开发周期;并且系统采用标准化的硬件架构设计,可以满足在雷达信号处理系统中通用性、规范性、低功耗和可灵活配置的应用需求。对比同类信号处理机,该架构设计在提高性能的同时,可大大降低系统的体积和功耗。

——信号处理