GaN基增强型HEMT器件的研究进展*

黄火林,孙楠

(大连理工大学光电工程与仪器科学学院,辽宁 大连 116024)

1 引言

近年来,全球变暖,环境污染加剧,全球能源危机日益严重,为了缓解节能减排的压力,工业界要求尽可能减小电能转化过程中的损耗。当下的中美贸易争端以及发达国家对我国的技术封锁迫使我国需尽快发展自有的半导体技术,这也是《中国制造2025》、“十四五”规划和2035年远景目标纲要等国家战略规划的核心内容之一。这些时代背景为具有高效节能特点的第三代半导体材料提供了快速发展的良机。

从材料选择角度来看,以第一代半导体材料硅(Si)为代表的绝缘栅双极晶体管(IGBT)和超结器件的发展已经接近其材料极限,这就要求寻找具有更宽带隙等特性的新一代半导体材料。目前,在第三代半导体材料中,氮化镓(GaN)和碳化硅(SiC)的发展较为成熟,且材料本身具有大的临界击穿电场、耐高温和抗辐照等特点,所以更适合制作电力电子器件[1-3]。目前,SiC在高压(高于1200 V)市场占据明显优势,但在功率转换和高频工作方面,GaN具有更加明显的优势。GaN转换器的低损耗归因于其低的开关损耗,这是由于GaN相比于SiC具有更好的电子传输能力。沿Ga面方向外延生长的结构存在较强的自发极化和压电极化效应,这会导致在GaN材料的异质结结构(典型如AlGaN/GaN)界面处产生高浓度的二维电子气(2DEG),因此GaN器件具有更低的导通电阻。通过对比Si、砷化镓(GaAs)、SiC、GaN半导体材料的综合性能(即约翰逊优值),可以发现GaN材料的整体性能相对较高。因此,在相同耐压等级下,GaN材料更适合制作高效的电力电子器件,特别是横向结构的高电子迁移率晶体管(HEMT),其导通电阻比Si器件的导通电阻低1~2个数量级,与同为第三代半导体材料的SiC器件相比,其导通电阻减小1/2~1/3[4-5]。

从器件结构看,GaN器件分为纵向和横向结构。纵向结构的器件需要用到GaN自支撑衬底,而目前来看,GaN自支撑外延片的成本较高,且GaN自支撑衬底的外延片尺寸较小,这就使得单个器件的成本更高。同时GaN纵向结构的器件并没有利用到GaN材料最大的优势——2DEG,而横向结构的器件则能很好地利用到这一特点。横向器件从开关类型看,分为耗尽型(常开型,D-mode)和增强型(常关型,E-mode)器件。由于AlGaN/GaN界面会产生高电子浓度(约1013cm-2·eV-1)、高迁移率[约2000 cm2/(V·s)]的2DEG,传统的GaN HEMT是耗尽型的,即器件栅极在零偏压下沟道中仍然存在高浓度的2DEG,使器件处于开启状态。而增强型器件在栅极零偏压时可以耗尽栅下沟道中的2DEG,使器件处于关断状态。增强型器件也因此具有安全、节能和能简化电路设计等方面的优势,是未来功率器件的重要发展方向。

从市场应用角度来看,以耐受电压600~1200 V为界,低于600 V的市场以GaN为主,主要面向消费类电子领域,这是目前GaN材料切入市场的最主要突破口。600~1200 V这一区间是GaN与SiC共存的领域,其主要应用在电动汽车(EV)与混合动力汽车(HEV)的转换器以及可再生能源的逆变器中。高于1200 V的市场以SiC为主,未来GaN材料的晶体质量若能进一步提高,体材料的缺陷密度进一步减小,或纵向结构的GaN器件技术成熟度提高,其也会在高电压市场中展现出更强大的竞争力。到目前为止,GaN材料通常通过金属有机化学气相沉积(MOCVD)法在Si、蓝宝石或SiC的衬底上生长。对于电力电子领域的应用,在Si衬底上制造的GaN HEMT最为常见,这是由于其具有成本效益较高的大尺寸晶圆和良好的导电性能。因此从成本角度考虑,大面积Si基GaN材料更具优势。此外,Si基GaN器件还可以与成熟的Si金属氧化物半导体(MOS)工艺流程兼容,以进一步降低大规模生产的加工成本。GaN HEMT作为平面器件,制作工艺相对简单,原材料和基础工艺可以依托我国现有庞大的发光二极管(LED)照明产业,因此更容易实现大规模产业化。实际上,Si基GaN器件目前已在消费类电子、车载电子市场中异军突起。

综上所述,从材料、器件结构、市场几个方面考虑,GaN增强型HEMT器件具有重要的战略研究意义。从基础科研到产业化,有若干个重要指标可以评估GaN增强型HEMT器件的性能,典型的有击穿电压VB、阈值电压Vth、开态电阻Ron、饱和电流密度IDS、栅耐压、阈值电压滞回等。本文回顾了一系列增强型器件的实现方案,着重介绍了基于栅凹槽结构的功率器件技术方案以及若干重要工艺,并提出了未来可能的技术方案。

2 GaN基HEMT功率器件的技术方案与进展

以AlGaN/GaN异质结材料为基础的HEMT自20世纪90年代末期就受到了研究者们的青睐,到了21世纪初期,该类型晶体管已经在射频器件领域得到应用,并且在当下5G通讯领域中被广泛使用。国内高校自2010年起掀起GaN基功率器件的研究热潮。近年来,随着国内外多家企业推出200 V/600 V/650 V的GaN产品,GaN功率器件的研发也进入了快速发展阶段。

2.1 耗尽型HEMT器件

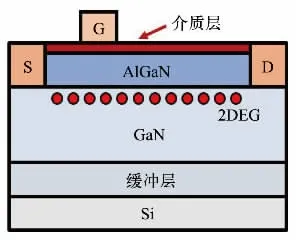

由于耗尽型HEMT器件的栅极无需复杂的特殊加工工艺,所以器件技术成熟较早,随着制作工艺的不断完善,器件的导通电流、击穿电压、特征电阻等关键参数已经取得较为理想的结果,GaN D-mode HEMT器件结构如图1所示。目前,耗尽型GaN HEMT在产业界面临的可靠性问题主要有电流崩塌、硬开关模式下阈值电压的漂移等,这些可靠性问题与场板的设计、栅介质层的选择、GaN缓冲层的设计和钝化层材料的选择等有关,需要对器件的制作工艺细节进一步优化,以提高器件的可靠性。

图1 GaN D-mode HEMT器件结构

耗尽型与增强型器件的区别在于器件的阈值电压是否大于0 V,这主要与AlGaN/GaN异质结界面产生的高电子浓度、高迁移率的2DEG有关。由于耗尽型器件在实际应用中的静态功耗与安全问题,增强型器件更适用于功率电子领域,而器件的栅极工艺与结构的设计是HEMT器件能否实现增强型操作的关键。

2.2 增强型HEMT器件

实现增强型GaN HEMT器件操作的方法有几种,主要是基于耗尽/减弱AlGaN/GaN异质结界面处的极化电荷来实现的。几种实现增强型操作的主流方案包括凹栅结构、氟化栅结构和p-GaN插入层结构。除此之外,共源共栅级联(cascode)结构、薄势垒结构(UTB)和纵向短沟道结构(VG-HEMT)也可以实现器件的增强型操作。几种实现增强型操作的器件结构如图2所示。

图2 几种实现增强型操作的器件结构

2.2.1 基于凹栅结构的增强型HEMT器件

凹栅结构的增强型HEMT器件的特点在于栅区势垒层的刻蚀,一般采用干法刻蚀或湿法腐蚀技术将栅极区域的AlGaN势垒层刻蚀掉,通过减弱异质结的极化效应,使得栅区下方沟道中的2DEG浓度降低到一定值,使得在栅极电压为0 V时沟道被夹断。一般情况下,在栅极金属与AlGaN势垒层之间会生长一层绝缘的介质层来确保栅极泄漏电流在器件工作时可以维持在相对较低的范围内,同时还可以提高器件栅极耐压,使器件栅极驱动电压范围变大。该结构器件的优势在于其栅极驱动电路较为简单,并且可以通过调整栅介质层的厚度来调节器件的栅耐压。基于凹栅结构器件阈值电压的提升与导通电阻的降低存在相互制约的关系,如何平衡2个参数之间的关系是该结构器件所关注的重点问题之一。

栅区势垒层的刻蚀往往会引入界面态,对器件性能造成不良影响,同时刻蚀精度的控制也会影响器件的阈值电压和导通电阻。为解决这一问题,国内外的研究者们提出了很多的方案。LIN等人使用650℃高温热氧化技术将栅区势垒层表面的AlGaN全部氧化,然后将样品浸泡在KOH溶液中,腐蚀掉被氧化的AlGaN层[6]。该技术利用了GaN和AlGaN易氧化的特性,其优势在于可以确保刚好将AlGaN势垒层刻蚀完全而不会过度刻蚀,且栅区界面的损伤较小,其缺点在于速率较慢且不适合应用于大规模生产。北京大学的研究者使用先氧化再湿法腐蚀的方案制作了具有凹栅结构的增强型HEMT器件,由于栅区沟道的刻蚀损伤小,器件的导通电阻很低,同时器件的阈值电压达到2 V以上,耐压超过1000 V[7-8]。日本福井大学的研究者报道了一种先刻蚀势垒层、再二次生长AlGaN的技术,采用该方案的器件阈值电压高达2.3 V,饱和电流达425 mA/mm,并且展现出比较大的潜力[9]。中山大学的研究者在栅区外二次生长AlGaN势垒层,制作了增强型HEMT器件,由于该技术沟道损伤小,器件获得了3.5 V的阈值电压和550 mA/mm的饱和电流[10-11]。韩国的IM等人提出了利用四甲基氢氧化铵做栅区腐蚀溶液的技术方案,获得的器件阈值电压可达3.5 V[12]。美国弗州理工大学的MA等人采用栅区分区域刻蚀的技术,使栅区形成多孔Tri-gate结构,在实现增强型器件的基础上减少了栅区的刻蚀面积,同时栅区的刻蚀区域还能对非刻蚀区域进行耗尽,在保证输出电流的情况下减少栅极边缘高电场的分布区域,在栅极零偏置的情况下达到2000 V的击穿电压[13]。大连理工大学HUANG团队在GaN凹栅增强型HEMT器件工艺和可靠性研究方面同样开展了大量的工作,研制的6英寸Si基GaN器件获得了2.5 V的阈值电压和600~900 V的耐压,并且从理论和实验层面揭示了器件缺陷态分布、应力下的电学参数模型和演变规律。

凹栅结构一般都会使用金属-绝缘体-半导体(MIS)/金属-氧化物-半导体(MOS)结构,这能够使器件栅极具有更大的安全工作范围和更低的泄漏电流。然而MIS/MOS结构的器件阈值电压的稳定性较差,这主要是由介质层/半导体界面的电荷和陷阱引起的。有报道称在氧化物/三族氮化物界面处的界面陷阱密度Dit较高,这会导致栅泄漏电流的增加和阈值电压的不稳定。因此,为追求高性能的GaN HEMT器件,栅槽的界面态与介质层的质量是重要的指标。

在栅区势垒层的减薄过程中,虽然对减薄工艺的优化可以减少对界面的损伤,但仍不可避免地会引入界面态,这对器件阈值电压和2DEG的迁移率都会造成不良的影响,在栅槽形成后引入界面处理工艺可以降低界面态。为降低界面态,对界面的处理方案主要分为氧化和氮化2种。西安电子科技大学的研究者使用N2O氧化栅区刻蚀后的界面,得到的器件阈值电压为1.5 V、亚阈值摆幅(SS)为70 mV/dec[14]。北京大学的研究者报道了在通过低压化学气相沉积(LPCVD)法生长氮化硅(Si3N4)之前使用N2O处理栅区刻蚀后的界面,抑制在LPCVD生长过程中的高温退化,制作的器件界面态降低,其饱和输出电流提高了3倍,达到607 mA/mm,在输出电流为0.1 mA/mm处提取的阈值电压为1.2 V,器件击穿电压达到1348 V[15]。香港科技大学的研究者使用等离子体增强化学气相沉积(PECVD)法制作Si3N4和LPCVD-Si3N4的组合,利用PECVD生长温度较低的特性将高可靠性的LPCVDSi3N4与凹栅结构相结合,制作出了高稳定性和高可靠性的增强型器件,制备的器件阈值电压为2.37 V,同时器件具有高的热稳定性、长时间依赖的栅介质层击穿寿命[16]。南方科技大学的研究者将凹栅结构的GaN(禁带宽度Eg约为3.4 eV)沟道转换为晶体GaON(Eg≈4.1 eV)层,来提高器件反向偏压应力下阈值电压的稳定性和栅可靠性。结晶的GaON是通过将刻蚀后的栅槽进行氧化、然后在LPCVD腔体中进行780℃NH3氛围的原位退火形成的。GaON晶体与GaN之间的价带偏移量大约为0.6 eV,这会在栅周围形成一个由空穴组成的势垒,该势垒能够阻止空穴向栅极一侧流动,从而降低空穴诱导的栅介质层的退化[17-18]。香港科技大学的研究者使用低损伤的NH3-Ar-N2原位等离子体预处理(RPP),得到了高质量的Al2O3(AlN)/GaN界面,使用C-V表征技术提取到低的Dit(1012~1013cm-2·eV-1)。此方案中NH3-Ar等离子体预处理的目的是去除表面氧化物,N2等离子体预处理的目的是在GaN表面形成氮化层[19]。

2.2.2 基于p-GaN插入层结构的增强型HEMT器件

p-GaN插入层结构同样是一种实现HEMT器件增强型操作的方案,这种结构的优势在于可以排除栅介质层对器件的影响,而其典型劣势源于p-GaN和下方AlGaN形成的p-n结,该p-n结在栅极施加正电压超过某一阈值时会正向开启,进而导致栅极电流增加,造成器件失效。因此需要对该结构的栅极驱动电路设计额外的保护电路,防止栅极电流过大。此外,目前p-GaN层仍然需要通过向GaN中掺入Mg来实现p型掺杂,其本身需要很高的激活温度,但激活率很低,晶格损伤极为严重。在后续的器件工艺加工中,一旦器件暴露在高温(高于500℃)的空气中,Mg原子会和空气中的H原子形成Mg—H键,降低p-GaN层的空穴浓度,从而影响器件的阈值电压。此外,栅极区域外的p-GaN需要被刻蚀掉,因此其他区域的AlGaN势垒层上表面可能会引入刻蚀损伤,降低2DEG浓度,同时栅区下方p-GaN的侧壁也可能成为漏电途径。

p-GaN HEMT的发展已经超过十年。2007年,UEMOTO等人首次提出了p型栅极HEMT的概念,并且制作出阈值电压为1.0 V、导通电流约为200 mA/mm的晶体管[20]。该技术的势垒层厚度一直是研究者们关注的重点。一方面,该类器件需要一定厚度的AlGaN势垒层去维持2DEG的浓度;另一方面,AlGaN势垒层太厚又会拉低器件的阈值电压。从近些年的研究成果来看,AlGaN势垒层厚度一般需要维持在10~15 nm,Al组分维持在15%~20%,这样易于形成增强型器件。此外,EFTHYMIOU等人进一步研究发现,p-GaN层的掺杂浓度在超过1018cm-3后才可以有效地对栅区进行耗尽。另一个值得关注的点是栅极金属功函数和器件阈值电压之间的关系,使用肖特基结制作栅极更易于获得更高的阈值电压和更低的栅极漏电流。GRECO等人发现,使用传统低功函数的Ti/Al金属叠层作为栅极电极材料,其阈值电压可以达到1.5 V,但随着器件在不同温度下的退火,其肖特基势垒高度在逐步降低,并且会出现阈值电压负漂、栅极泄漏电流增大等现象。为了避免栅极势垒高度的退化,应该在器件后续的加工工艺中避免高温环境[21]。POSTHUMA等人报道了利用TiN制作的器件栅电极,其阈值电压可以达到2.1 V[22]。而LUKENS等人报道了一种“先栅”的自对准工艺,使用金属Mo同时作为刻蚀掩模层和栅极金属,实验结果表明,该结构在经过825℃的高温退火后,势垒没有出现退化现象[23]。

2.2.3 基于cascode结构的增强型器件

级联技术是实现增强型操作的一个重要技术路线,其将一个Si MOS管与一个耗尽型的GaN基HEMT采用共源共栅的方式连接。器件整体外接的D为HEMT的漏极,外接的S为MOS管的源极与HEMT的栅极,外接的G为MOS管的栅极,MOS管的漏极与HEMT的源极相接。当G端施加电压大于MOS管的阈值电压时,MOS管导通,其源、漏2端产生较大电流,并且2端的压降可以忽略。同时,这意味着HEMT的源、栅2端电压也近似相等,即栅压为0 V,耗尽型HEMT导通。因此任何施加在器件D端的电信号都会产生一个电流,通过由HEMT与MOS管串联的电路,器件整体导通。同理,当G端施加电压小于MOS管的阈值电压时,MOS管关断,其源、漏2端产生较大压降,HEMT的源、栅2端的电压差同样明显,HEMT中的栅压小于阈值电压,且小于0 V,耗尽型HEMT关断,HEMT与MOS管相串联的电路整体关断。

级联技术的优势在于其绕过了增强型HEMT的技术难点,采用现阶段技术极为成熟的Si基MOS管来实现增强型操作。理论上,cascode晶体管所需的栅驱动与传统Si MOS管一致,简化了驱动电路的额外设计。但级联技术的劣势也极其明显,它会增加后续封装技术的复杂性;在高温下,器件仍然受Si管性能的限制,GaN基HEMT的优势难以体现;由于2种晶体管的特殊连接方式,会形成cascode器件的内部回路,增加器件内部的寄生电感;由于Si管本身的电子迁移率较低,级联晶体管很难在高于1 MHz的高频应用场景中使用。

近年来,cascode晶体管投入商用的产品已发展得较为成熟。以目前Transphorm公司推出的cascode类型的TPH3206PSB型号为例,它的电压应用等级在650 V,采用TO-220的封装方式,其阈值电压为2.1 V,开态电阻为180 mΩ,导通电流为16 A。为了改善Si材料对器件整体性能的影响,研究者们也尝试用其他材料去代替Si。香港科技大学的研究者报道了基于SiC管与GaN基HEMT结合的级联结构,其优势在于利用SiC材料代替Si,进而可以提升器件的整体耐压等级(达到1200 V),兼容相对高频率的驱动并且具备更低的开关损耗,具有很大的发展空间[24]。总体来说,cascode技术易于实现,器件稳定性高,是目前市场上最为成熟的增强型器件方案,但其劣势同样明显,无法完全发挥GaN材料的优势。

2.2.4 其他增强型器件方案

氟化栅结构的增强型HEMT的特点在于栅区势垒层中的离子注入,一般情况下会注入氟离子。2005年,CAI等人首次提出使用氟化栅结构的方案,同时采用热退火技术改善等离子处理带来的损伤,最终将器件的阈值电压从-4 V增大到0.9 V,饱和电流为310 mA/mm[25]。2015年,ZHANG等人为了缓解氟离子注入时引起的栅极损伤,在AlGaN上使用LPCVD-SiN作为栅介质层和能量吸收层来减小栅极损伤,最终得到了阈值电压为3.3 V、饱和电流为200 mA/mm的器件[26]。

除了正常的凹栅结构外,还有根据凹栅结构演变而来的薄势垒结构的增强型HEMT器件。北京微电子所使用在外延上进行调整的GaN外延片,其AlGaN势垒层仅有4 nm,在除栅区外的沟道层上方利用LPCVD生长的Si3N4来恢复2DEG浓度,而栅区上方由于仅有很薄的势垒层,所以栅区下方的沟道中并未极化出很高浓度的2DEG。栅区暴露的AlGaN势垒层使用等离子体增强原子层沉积(PEALD)的原位RPP技术进行界面处理,然后生长Si3N4作为栅介质层。最终制备的器件提高了阈值电压的稳定性和最大输出电流[27]。除此之外,VG-HEMT结构也可以实现HEMT器件的增强型操作,它通过将器件沟道的一部分转化为纵向,由于纵向部分并无2DEG,所以器件在栅极零偏压下处于关断状态。

3 器件制备

制备凹栅结构HEMT器件的完整工艺流程如图3所示,一般包括湿法清洗、光刻、干法刻蚀(湿法腐蚀)、金属蒸镀、退火处理、薄膜沉积等工艺。

图3 制备凹栅结构HEMT器件的工艺流程

主要流程有:(1)准备具有相应纵向耐压能力的外延片;(2)通过有机、无机湿法处理去除样片表面污染;(3)通过制造有源区来隔绝器件与器件之间的漏电;(4)制备源、漏电极,使之形成良好的欧姆接触;(5)将栅区AlGaN势垒层刻蚀/腐蚀到目标深度;(6)沉积栅介质层,介质层沉积之前要保证栅槽界面质量(平整度、界面态等),介质层的目的是阻止栅极漏电、提高栅耐压;(7)选择蒸镀具有适当功函数的金属,作为栅电极;(8)器件的钝化及开口有利于器件的保存;(9)制作场板来分担器件在高压下的电场,减小高压应力下器件性能的退化。

3.1 外延

很多GaN HEMT都是异质外延生长在异质衬底上的,由于GaN和异质衬底材料差异较大,在生长GaN时会产生高密度的位错、凹坑和裂纹等。为利用MOCVD制备出高质量的GaN外延结构,引入几种改进缓冲层结构的方法,从而进一步提高GaN基HEMT的性能。

GaN HEMT在电力电子领域的应用需要具有较高的垂直击穿电压,这主要依赖于外延GaN的厚度,但在较厚的GaN表层往往会出现严重的晶圆弯曲和裂纹。为解决这一问题,对GaN外延技术进行了一系列的优化来提高外延质量。首先,在Si衬底上低温生长AlN成核层,这是一种有效的通过降低生长GaN时的应力来提升临界厚度的方式。在AlN成核层上是AlGaN应力释放层,在应力释放层中Al组分随厚度的增加而减小。再向上是GaN外延缓冲层。一方面,由于外延层总厚度仍然较小,此时应力未能完全释放,缓冲层中仍然存在许多位错和缺陷;另一方面,未经掺杂的GaN呈弱n型,具有约1016cm-3的背景电子浓度,为了提高器件的垂直耐压,一般会在缓冲层中进行补偿掺杂,常用的掺杂剂有Mg、Fe、C等能够形成受主的杂质,使得缓冲层呈现近绝缘的状态。近绝缘的缓冲层对抑制垂直漏电、提升器件耐压具有非常重要的作用。然而,一般引入的受主杂质多以深受主能级存在,受主电离能高,电离十分困难,电离率较低,因此即使GaN本身的背景电子浓度并不十分高,想要达到近绝缘的补偿效果也需要掺入较高浓度的受主杂质。缓冲层上是本征无故意掺杂的GaN沟道层、1 nm左右的AlN增强层和AlGaN势垒层。其中,AlN增强层会使界面更加平整,同时能够提升2DEG的浓度和迁移率。AlGaN势垒层中Al的质量分数一般为0.2~0.4,厚度一般为20~30 nm。AlGaN势垒层上方会有一层薄的GaN帽层,这是为了提升2DEG的迁移率,同时减小表面漏电。在它的上面可能会有一层为抑制电流崩塌而生长的钝化层。

3.2 欧姆接触

欧姆接触的制备是GaN HEMT中不可或缺的重要组成部分,除光刻外还需用到金属蒸镀、金属剥离、快速热退火等工艺。理想的欧姆接触呈现电阻特性,且电阻值越小效果越好,常常使用接触电阻来衡量器件欧姆接触的优劣。值得注意的是:(1)金属与半导体之间必然存在功函数失配;(2)AlGaN势垒层本身的禁带宽度很大;(3)非故意掺杂的AlGaN/GaN异质结掺杂浓度很低。三者共同决定了金-半接触中的半导体一侧将形成势垒,因此如何降低该势垒是欧姆接触制备技术的关键。

AlGaN/GaN异质结的欧姆接触通常由Ti/Al/Ni/Au 4层金属堆叠而成。在高温退火后,底部第一层Ti金属向下扩散,与N原子结合形成TiN,进而降低势垒高度,同时在(Al)GaN中形成高浓度的N空位,作为浅施主杂质形成欧姆接触。第二层Al金属在高温退火过程中会出现沸腾现象,加剧Ti金属的扩散行为。第三层高熔点的Ni金属用于阻止下层Al与上层Au之间的相互扩散。顶部的Au防止金属电极被氧化。考虑到与成熟硅基生产线的兼容性,发展无金工艺的欧姆接触是十分必要的。一些无金工艺的欧姆接触方案如表1所示。

表1 无金工艺的欧姆接触方案

表1中的凹槽代表欧姆接触处的凹槽,通过将AlGaN/GaN刻蚀掉使2DEG直接与金属电极接触。为了保证良好的欧姆接触性能,需要优化刻蚀工艺。表1中接触电阻使用传统的传输线模型(TLM)来计算,该方法计算单个欧姆接触电极的总阻值是准确的,但是在进一步确定各电阻成分时有一定的误差。例如电极下方半导体的方块电阻与材料本身的方块电阻,由此利用TLM模型推导出的比接触电阻也具有一定的误差。为了获取各部分准确的电阻值,大连理工大学研究团队提出了电极对模型(EPM)以更好地解决上述问题[36]。

3.3 栅区工艺

3.3.1 凹槽栅结构

基于凹栅结构的增强型HEMT中栅区工艺尤为重要,例如栅介质层的选择、栅区AlGaN势垒层的刻蚀与刻蚀后的界面处理等。基于凹栅结构HEMT器件的阈值电压和导通电阻之间的制约关系,一般情况下栅区AlGaN势垒层在刻蚀后会剩余5 nm左右。器件截面与栅区势垒层刻蚀后原子力显微镜(AFM)的扫描结果如图4所示。由MOCVD方法生长的6英寸AlGaN/GaN(25 nm/4μm)异质晶圆,其中AlGaN中Al的质量分数为0.27,且在AlGaN表面原位生长了20 nm的Si3N4作为钝化层。根据霍尔测试结果,得到异质结界面处2DEG浓度大概为9×1012cm-2,对应的迁移率为1800 cm2/(V·s)。欧姆接触使用Ti/Al组合的无金工艺,根据TLM模型测试得到其接触电阻为0.5Ω·mm。栅极到源极的距离LGS、栅长度LG、栅极到漏极的距离LGD、栅宽度WG分别为4μm、1μm、16μm、140μm。栅区AlGaN势垒层刻蚀后剩余大约5 nm。

图4 器件截面与栅区势垒层刻蚀后原子力显微镜(AFM)的扫描结果

栅凹槽结构的MIS-HEMT可以获得更高的阈值电压和更大的栅极击穿电压。但由于栅极凹槽较深,同时刻蚀损伤引起2DEG迁移率严重下降,导致器件开态电阻相对较高。此外,由于刻蚀后粗糙表面形成的栅介质质量较差,栅泄漏通常很严重。迄今为止,原子层沉积(ALD)的Al2O3和LPCVD-Si3N4是应用最广泛的栅极介质材料。中山大学的研究者使用Al2O3介质层制备的HEMT器件,阈值电压为2.5 V,栅沟道电阻为519Ω/□[37]。苏州纳米所的研究者使用Si3N4制备的HEMT器件,击穿电压为1162 V,器件品质因数(FOM)为469 MW·cm-2,使用电导法提取的界面态密度为1.4×1013~5.3×1013eV-1·cm-2,600 V高漏端应力后器件导通电阻从2.88 mΩ·cm2增加到4.89 mΩ·cm2[38]。香港科技大学的研究者使用Si3N4制备了高性能的HEMT器件,阈值电压为2.37 V,同时介质层具有较高的热稳定性、长时间的栅击穿寿命和低偏置温度不稳定性等优势[16]。然而,基于Al2O3的MOS结构具有一个相对较低的临界击穿场(5~7 MV/cm),而基于Si3N4的MIS结构需要一个高温(约780℃)沉积过程,这可能会导致工艺兼容性问题,同时在薄膜中会带来过大的应力。因此,开发更多双介质层的栅极方案和技术是必要的。

将理想的叠层介质分为界面层介质和耐压层介质进行分析。界面层介质需要考虑介质层中的电荷问题,若介质层中的固定电荷为负电荷,在栅极不施加偏压的情况下会对沟道中的2DEG有耗尽作用,从而提升器件的阈值电压,同时,界面层介质还需要与AlGaN势垒层形成较低的界面态,这会进一步提升器件的可靠性。而耐压层介质需要在电极和AlGaN势垒层间形成较高的势垒,理论上需要选用与AlGaN材料导带阶跃较大的介质,它可以减小器件栅极漏电,此外还需要介质层具有较大的临界击穿电场,这会给器件提供较大的栅驱动范围。

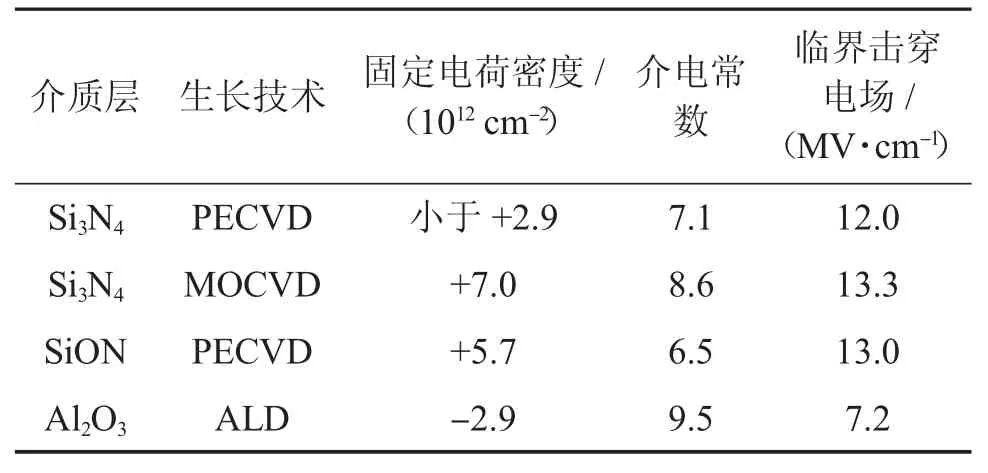

为了确定哪种材料更适用于界面层介质和耐压层介质,对不同生长方式下生长的不同材料进行了电荷以及耐压的表征,不同介质层材料性能如表2所示。为发挥栅介质层的耐压与沟道调制作用,使用Al2O3+SiON叠层介质制作HEMT器件[39]。

表2 不同介质层材料性能

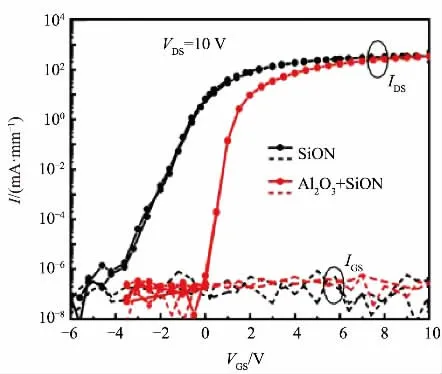

以介质层作为变量制备了2个样品,样品A为30 nm SiON,样品B为10 nm Al2O3+20 nm SiON(其中Al2O3作为界面层介质,更靠近沟道)。2个样品的转移特性曲线如图5所示(其中VDS、IDS、VGS分别为漏端电压、漏端电流、栅端电压),从图5可以观察到2个器件的电流开关比均大于108,在栅极电压从-6 V提高到10 V的过程中,栅极泄漏电流没有明显的上升趋势,证明介质没有发生击穿。经测量发现,样品B阈值电压的滞回小于10 mV,说明其界面态浓度很低。另外,样品A和B的亚阈值摆幅分别为515 mV/dec和172 mV/dec。样品B所对应的亚阈值摆幅较小,一方面是因为Al2O3的介电常数大于SiON,另一方面是因为Al2O3/AlGaN界面电荷浓度较SiON/AlGaN界面更低。可以明显观察到A、B 2个样品的阈值电压差异较大,样品B的阈值电压为0.8 V,实现了增强型操作。

图5 2个样品的转移特性曲线

虽然使用该方案的器件实现了增强型操作,但阈值电压仍较小,在实际电路应用中会出现误开启的操作,可以在栅介质层沉积之前使用界面处理方式来改善栅界面性能,进一步提升器件的阈值电压。

研究发现,栅介质层/(Al)GaN界面处通常存在1013cm-2·eV-1的高密度界面态,这会引起严重的栅漏电和阈值电压的不稳定性,因此,在栅介质层沉积之前有必要引入界面处理技术来修复由刻蚀引入的界面态。香港科技大学的研究者使用NH3-Ar-N2界面处理技术制备了HEMT器件,该技术可以有效地去除界面原生氧化物,同时在三族氮化物表面形成类单晶氮化物界面层,器件的亚阈值摆幅为64 mV/dec,阈值电压的滞回为0.09 V,同时还具有较低的Dit(1×1012~6×1012cm-2·eV-1)[19]。西安电子科技大学使用N2O进行界面处理,制备的器件阈值电压为1.5 V,亚阈值摆幅为70 mV/dec[14]。这说明栅槽界面处理是可以改善器件性能的。

基于上述Al2O3+SiON叠层栅介质,在栅槽AlGaN势垒层刻蚀后引入氧和氟混合等离子体界面处理来改善器件性能[35]。使用混合等离子体界面处理后器件的转移特性如图6(a)所示,由于势垒层表面固定了带负电荷的氟离子,阈值电压正向漂移了2.0 V左右,达到了2.5 V。根据阈值电压的差异,可以粗略推断出氟离子的浓度约为1.6×1012cm-2,2个器件的开关电流比均达到了109,并且在-4~12 V的栅极扫描范围内保持10-7mA/mm的低栅极泄漏电流。混合等离子体处理后器件的亚阈值摆幅为188 mV/dec,比对照组减小了110 mV/dec,表明该界面处理方案确实有助于降低栅极表面陷阱浓度。有无混合等离子体处理器件的栅耐压特性如图6(b)所示,与未使用界面处理的器件相比,使用混合等离子体处理方案的器件展现出更好的栅耐压(26 V)。

图6 器件的直流I-V特性

3.3.2 p-GaN栅结构

在p型栅结构中,一般选择使用p-GaN作为插入层,这也是目前最成熟的工艺。其典型特征是在栅极下方插入一层p-GaN层,其作用是抬高AlGaN/GaN界面处的导带能级,调制此类器件阈值电压的方法在于改变p-GaN的掺杂浓度,或者调整栅区下方AlGaN势垒层的厚度,p-GaN结构栅下能带如图7所示。当应用p-GaN栅极时,相当于制备了一个栅极注入晶体管(GIT),来降低随着栅极电流而增加的导通电阻。事实上,p-GaN的高受体浓度是保持该类二极管栅极特性所必需的,而这也可以通过在栅极下面引入基于NiOx的插入层来实现。这种结构利用金属与p-GaN间较高的势垒减小栅漏电并提供正向阈值电压。该技术由丰田公司在2007年首次提出,现在已发展成为主流商用技术之一,如Panasonic和EPC等已推出多款基于p型栅结构的增强型器件,但它们的阈值电压一般都小于2 V,在实际电路应用中会由于过充等现象造成器件损坏。

图7 p-GaN结构栅下能带[40]

p-GaN栅结构的器件在外延AlGaN上生长的是p型GaN,可以通过干法刻蚀或氢等离子体处理制备出所需的p-GaN插入层:(1)对器件进行氢等离子体处理,将p-GaN转化为高阻GaN(HR-GaN);(2)通过干法刻蚀将除栅下区域的p-GaN刻蚀掉(2种方法在实施时均需使用光刻胶保护栅下区域的p-GaN)。其他工艺与制备凹槽栅结构器件相差不大。

近年来,对于该类型器件的研究越来越多地集中在可靠性方面,如器件在反向续流应力下的表现、应力测试中陷阱俘获与释放电子的机制、再生长p-GaN帽层结构中栅极的退化现象等。然而,由栅极电压过大所引起的栅极电流泄漏问题并未得到有效解决,同时栅控能力减弱、寄生电容增加等问题也依然存在。

3.3.3 氟化栅结构

具有氟化栅结构的增强型器件与其他方案在栅区的工艺不同,该方案是在蒸镀栅电极前通过高能离子注入机对栅下势垒层注入氟离子。由于氟离子具有高的电负性,在势垒层中会形成带负电的固定电荷,相当于形成了一个附加势垒。从能带角度分析,它会提升栅下的势垒高度,从而得到较高的阈值电压,同时减小栅极泄漏电流。该方法可以通过控制氟离子的处理时间和剂量得到较高的阈值电压,同时结合凹栅结构中的介质层能够更好地抑制栅漏电;但由于势垒层中注入氟离子会引入缺陷,这些缺陷会降低2DEG迁移率,导致器件输出电流减小,同时会使器件阈值电压的稳定性变差。此外,在大面积晶圆上制作器件时,使用此方法很难控制器件阈值电压的均匀性。

3.4 场板和钝化的设计

对于电源开关应用,GaN HEMT通常工作在第一象限(正偏置和正电流)和第三象限(负偏置和负电流)[41]。在第一象限工作时,要求器件在关态期间阻止高漏端偏置(例如用于消费类电子设备适配器的600 V),并在开态期间具有低的导通电阻。基于GaAs HEMT的研究经验,栅靠近漏极一侧的强电场是导致关态击穿和电流崩塌的主要原因[42]。因此,需要通过器件结构设计来解决关态高压下的强电场问题,如局部氟等离子体处理和局部p型掺杂,但场板的设计仍然是主要的方法。

当HEMT器件从高压关断切换到开启状态时,场板的电场调控有助于抑制电流崩塌和增加动态电阻。在高压关断期间,强电场会加速电子向半导体表面移动。随后电子被捕获并产生额外的电场,在器件切换到导通期间耗尽2DEG。加上更好的钝化层,场板可以降低电场,避免电子加速。通常,用于增加击穿电压的场板设计也可用于抑制电流崩塌。栅极场板和源极场板的优化组合可以同时增加器件的击穿电压,并抑制电流崩塌。

场板的设计在调控电场的同时,也会引入寄生电容,这可能会损害器件的高频和开关性能。因此,业界提出了几种独特的场板结构以减少寄生电容,例如浮空场板和空气桥场板。倾斜形状的场板也可用于调控电场的分布,并提高器件的击穿电压。

4 结束语

本文介绍了GaN基HEMT器件的几种主流实现方案。具有凹栅结构、p-GaN插入层结构和cascode结构的器件是最具有应用前景的技术。在阐述了HEMT器件的工作原理后,本文阐述了GaN基HEMT器件的一系列最新研究进展,包括材料外延和器件关键制造技术等。另外,本文基于凹栅结构的E-mode HEMT技术路线,重点讨论了栅槽刻蚀后的界面处理和栅介质层工艺以及其对HEMT器件的性能影响。未来,纵向垂直结构的GaN功率器件是重要发展方向,目前高性能垂直结构的GaN基功率器件的发展方向还聚焦于降低衬底成本、提高衬底晶体和外延结构质量以及高效离子注入电隔离等方面。而横向结构GaN HEMT的研究重点在于大面积(超过8英寸)外延质量和器件工艺可靠性,业界在向更高耐压(大于1000 V)应用等级、中低压应用中更高功率密度以及与传统Si CMOS工艺的兼容等方面努力。新的制造工艺必须考虑工艺的稳定性和器件的可靠性。随着设备技术的创新、材料和器件工艺质量的提升,GaN功率器件的发展与应用将进一步加速。