异类叠层基电荷陷阱存储器件的性能研究

汤振杰,张希威,李 荣

(1.安阳师范学院物理与电气工程学院,河南 安阳 455000; 2.安阳师范学院数学与统计学院,河南 安阳 455000)

随着科学技术的进步,移动电话、智能电视、数码相机、移动硬盘和计算机等电子产品被广泛应用[1],其核心部件为非易失性存储器,即关闭外部电源,存储的信息资料仍可以长时间保存。在众多类型的非易失性存储器中,Si-SiO2-Si3N4-SiO2-Si型(SONOS)电荷陷阱存储器件以其分离的电荷陷阱、较低的操作电压、可小型化、良好的抗疲劳性能以及与传统半导体制备工艺良好的兼容性等特点,成为一种极具应用前景的候选存储结构[2-3]。但是,数据保持能力和编写速度之间的平衡问题一直是限制SONOS型器件发展的瓶颈[4],而且Si3N4存储层的深能级陷阱的利用率不高,导致器件的性能很难满足市场日益增长的需求。为了解决这一困难,从业人员进行了大量的工作,研究的焦点主要集中在寻找传统SONOS型器件中Si3N4存储层的替代物[5-6]。基于前期研究成果,本文借助脉冲激光沉积系统,利用Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层薄膜替代传统的Si3N4作为存储层制备电荷存储器件,系统研究了器件的存储性能。

1 实验过程

1.1 Hf0.5Si0.5O2和Zr0.3Si0.7O2陶瓷靶材的制备

首先,将HfO2和SiO2粉体按照摩尔比1:1的比例混合,ZrO2和SiO2粉体按照摩尔比3:7的比例混合,分别置于球磨机中湿磨24 h使之细化并混合均匀,并在烘箱中烘干;然后,在18 MPa压力下,利用压片机将粉体压制成直径为1 cm、厚度为0.5 cm的片状样品;再将压制成型的样品置于烧结炉中,在1350 ℃温度下烧制8 h,使之充分进行固相反应形成致密而均匀的陶瓷靶材。同时,利用上述方法,使用单一SiO2粉体制备了SiO2靶材。

1.2 异类叠层基电荷存储器件的制备

首先,将p-Si衬底置于丙酮中超声清洗3 min,去除衬底表面的杂质;然后将衬底置于氢氟酸稀释溶液中超声清洗1 min,去除衬底表面的氧化物;再将Hf0.5Si0.5O2、Zr0.3Si0.7O2、SiO2靶材和衬底分别置于脉冲激光沉积系统沉积腔内的靶台和衬底台上,利用机械泵抽取腔内的空气至真空度为1×10-4Pa。打开准分子激光器的脉冲激光,在衬底的表面沉积生长一层厚度为3 nm的 SiO2薄膜作为隧穿层;然后,在隧穿层表面依次沉积生长厚度均为5 nm的Hf0.5Si0.5O2和Zr0.3Si0.7O2薄膜,形成Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层电荷存储层;紧接着,再沉积一层厚度为10 nm的SiO2薄膜作为阻挡层。利用磁控溅射沉积系统,在SiO2阻挡层表面沉积生长一层金属Pt作为上电极材料,将导电银胶涂抹在硅衬底背面作为下电极。最后将制备的电荷存储器件置于快速退火炉(RTA- 400)中,在N2气氛下800 ℃快速退火10 s,制备的器件结构如图1(a)所示。由于Hf和Zr基氧化物的禁带宽度随着组分含量的变化而变化[7-8],因而可以得到异类叠层存储层和器件的能带结构,如图1(b)所示。

图1 Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层基电荷陷阱存储器件(a)结构示意图和(b)能带结构示意图Fig.1 (a)structural schematic diagram and (b)energy band schematic diagram of charge trap memory with Hf0.5Si0.5O2/Zr0.3Si0.7O2 heterogeneous laminated structure

1.3 器件的电学性能测试

通过4200半导体参数测试仪( Keithley 4200 SCS) 测量器件的电学性能。

2 实验结果与讨论

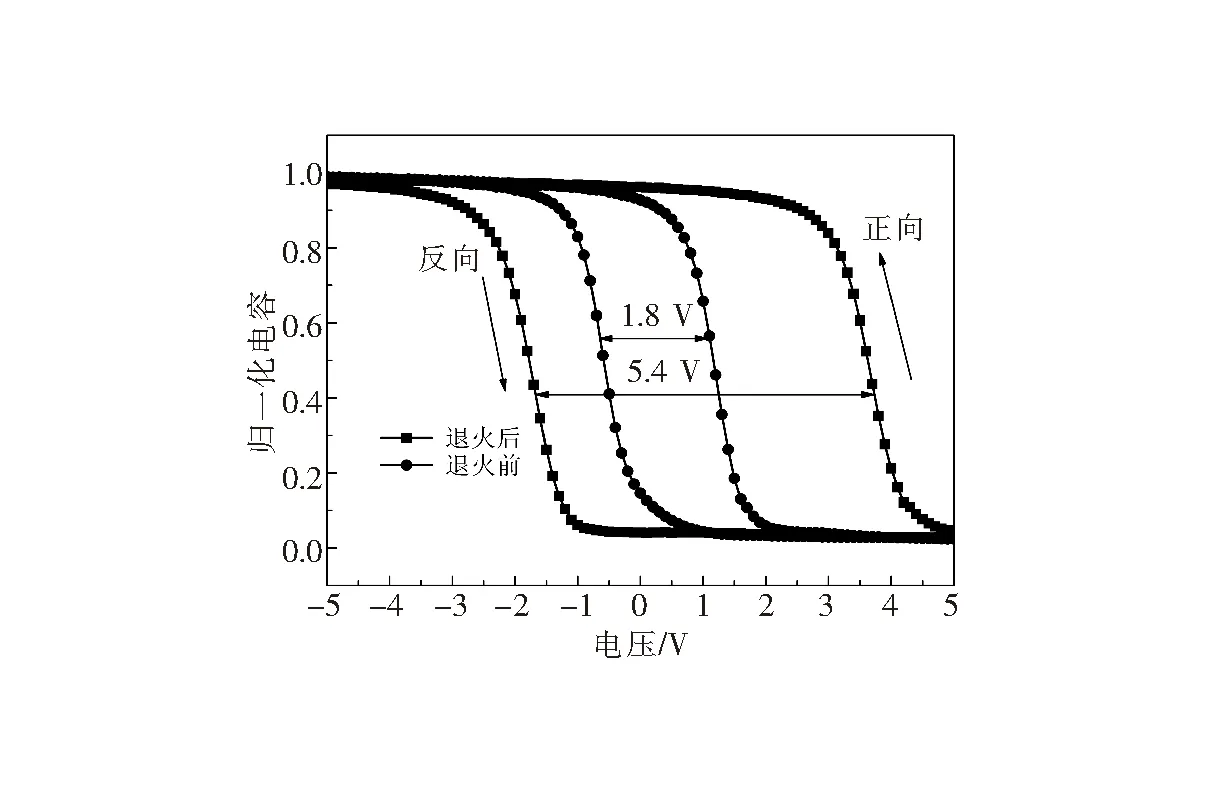

2.1 存储窗口性能研究

利用高频(1 MHz)电容-电压(C-V)曲线表征器件在扫描电压下的存储效应,如图2所示,即在Pt电极先施加+5~-5 V的电极扫描电压(正向),而后再施加-5~+5 V的扫描电压(反向),其中正向与反向扫描电压下,电容-电压曲线的平带电压偏移量之差△VFB定义为存储窗口。由图2中可知,退火前和退火后的存储窗口△VFB分别为1.8 V和5.4 V,结果表明相比未经过退火处理的器件,高温快速退火能够提高器件的存储窗口。这是因为经过高温退火,Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层结构中的浅能级陷阱的密度降低,在Hf0.5Si0.5O2和Zr0.3Si0.7O2体内以及Hf0.5Si0.5O2/Zr0.3Si0.7O2界面处产生高密度的深能级陷阱,正向和反向扫描电压作用下,电荷主要被深能级陷阱俘获。

图2 ±5 V电极扫描电压下Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层基电荷陷阱存储器件的C-V曲线Fig.2 Capacitance-voltage curves of charge trap memory with Hf0.5Si0.5O2/Zr0.3Si0.7O2 heterogeneous laminated structure under ±5 V gate sweeping voltage

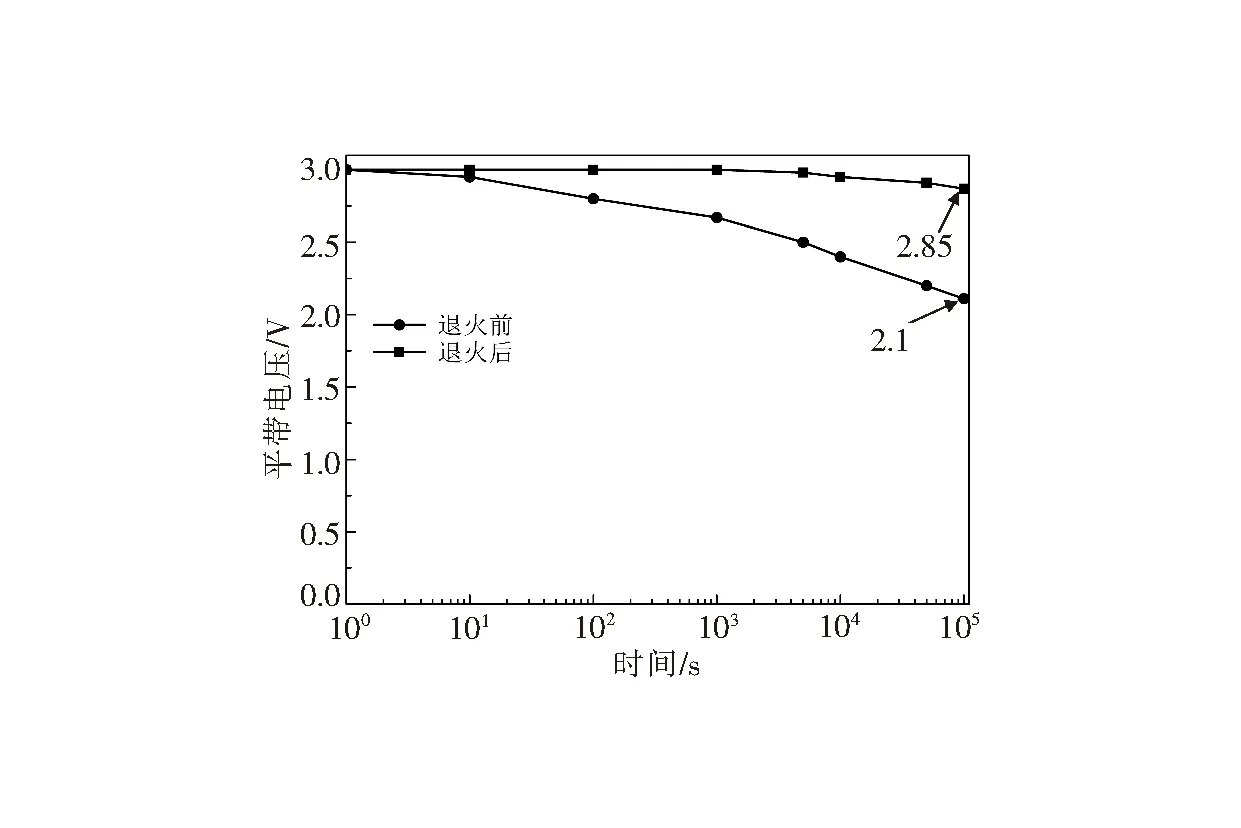

2.2 数据保持性能分析

图3为异类叠层基电荷陷阱存储器件的数据保持能力。首先,对退火前后的器件进行写入操作,使器件达到相同的平带电压偏移量+3 V;然后测试经过105s的保持时间平带电压的偏移量。从图3中可以发现,经过105s的保持时间,Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层基电荷存储器件的平带电压出现了不同程度的下降,退火前和退火后器件的平带电压分别下降到2.1 V和2.85 V,对应的电荷损失量分别为30%和5%。结果表明,退火处理可以显著地提高器件的数据保持能力。经过高温快速退火处理,Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层结构中的浅能级陷阱密度下降,深能级陷阱密度增加,进入到存储层的电子被深能级陷阱俘获,随着保持时间的延长,被深能级陷阱俘获的电子很难脱离束缚。未经过退火处理的器件,一部分电子被浅能级陷阱俘获,电子很容易进入存储层导带,进而向Si衬底和电极方向泄露。另外,Hf0.5Si0.5O2和Zr0.3Si0.7O2薄膜之间的势垒进一步阻止了被俘获电子向电极方向的泄露。

图3 Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层基电荷陷阱存储器件的数据保持能力Fig.3 Data retention of charge trap memory with Hf0.5Si0.5O2/Zr0.3Si0.7O2 heterogeneous laminated structure

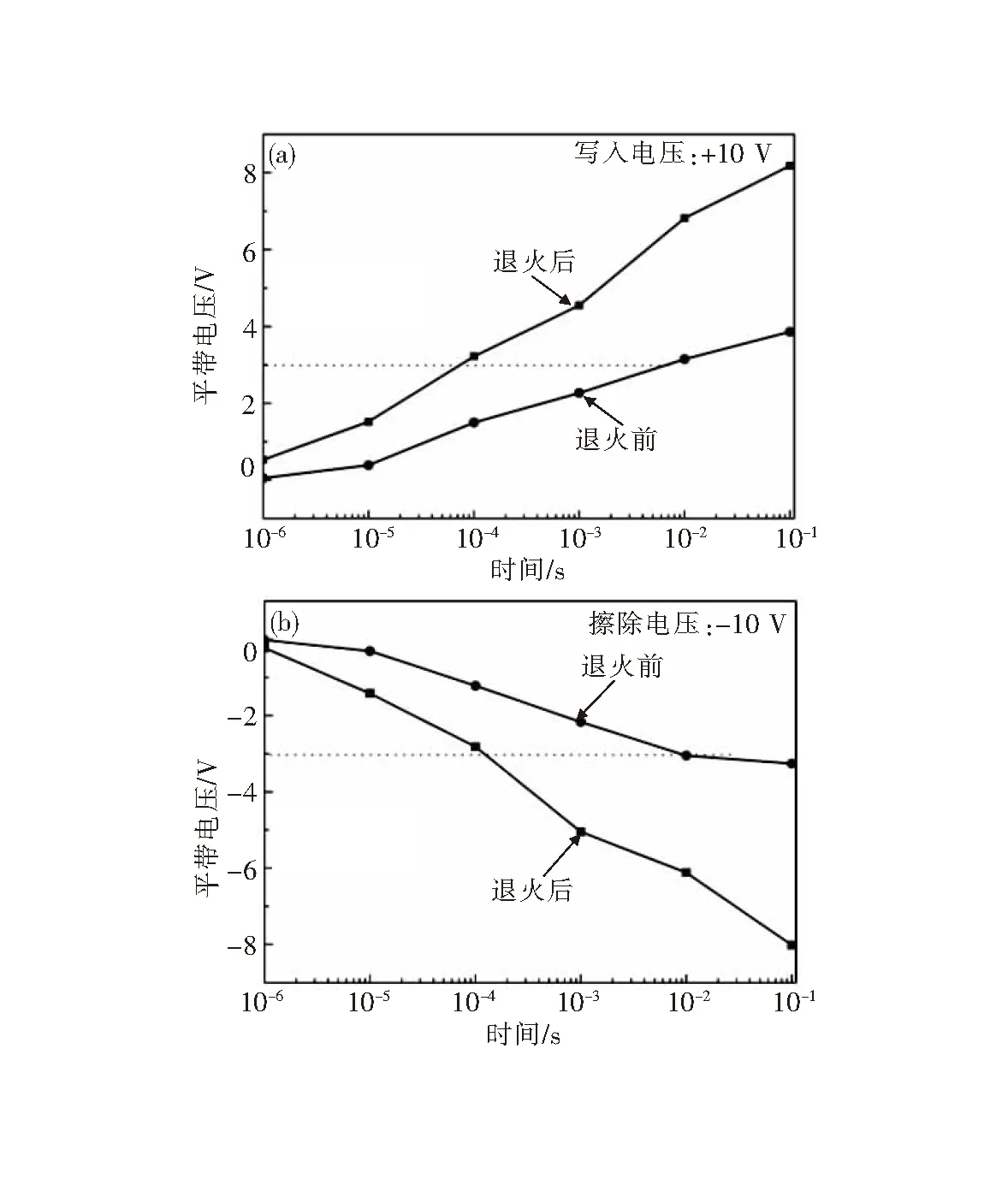

2.3 瞬时速度分析

图4为器件编程状态和初始状态之间的平带电压偏移量与瞬时写入/擦除时间的关系。从图4中可以发现,±10 V操作电压下,经过高温快速退火处理的器件表现出更大的平带电压偏移量。以达到相同的+3 V和-3 V平带电压偏移量为例,退火前器件所需时间分别为6×10-3、1×10-2s,退火后器件所需时间分别为7×10-5、1.2×10-4s。结果表明,退火处理能够提高器件的写入/擦除速度。一方面,Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层结构之间形成的势垒,有效抑制电子向Si衬底和电极方向泄露,提高了电子留在存储层的数量;另一方面,高温退火处理提高了深能级陷阱密度,被俘获的电子在写入和擦除状态下,不容易脱离陷阱束缚。

(a)写入操作;(b)擦除操作图4 Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层基电荷陷阱存储器件的瞬时速度(a) write operation; (b) erase operationFig.4 Instantaneous velocity of charge trap memory with Hf0.5Si0.5O2/Zr0.3Si0.7O2 heterogeneous laminated structure

3 结论

采用脉冲激光沉积系统制备了Hf0.5Si0.5O2/Zr0.3Si0.7O2异类叠层薄膜基电荷陷阱存储器件。经高温退火处理的异类叠层基电荷陷阱存储器件在±5 V扫描电压下,具有5.4 V的电荷存储窗口;经过105s保持时间,电荷损失量仅为5%;达到±3 V平带电压偏移量所需时间分别为7×10-5、1.2×10-4s。实验结果表明,高温快速退火处理能够显著提高器件的电荷存储性能。这主要归因于高温退火处理减小了异类叠层存储层中的浅能级缺陷密度,提高了叠层结构的界面陷阱密度,而且叠层结构形成的层间势垒,有效抑制了电子向衬底和电极方向的泄露。