基于 FPG A的多功能等精度频率计的设计

李红丽,马耀锋

(1.中州大学实验管理中心,郑州 450044;2.中州大学信息工程学院,郑州 450044)

1.引言

基于传统测频原理[1]的频率计将随被测信号频率的下降而降低,在实用中有较大的局限性,而等精度频率计不但具有较高的测频精度,不随所测信号的变化而变化,而且在整个测频区域能保持恒定的测频精度。本课题利用 EDA技术,基于 KHF-5型 CPLD/FPGA实验开发系统上的 Altera公司的 EP1K100QC208-3芯片来进行设计与实现等精度频率计的研究。这使得设计过程大大简化,缩短了开发周期,减小了电路系统的体积,同时也有利于保证频率计具有较高的精度和较好的可靠性。

2.等精度测频原理

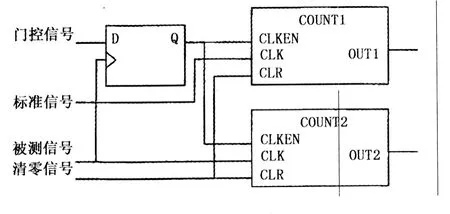

等精度测频[2]的实现方法可以用图 1来简化说明。

图 1 等精度测频原理框图

图 1的门控信号是可预置的宽度为 Tpr的一个脉冲。COUNT1和 COUNT2是两个可控计数器。标准频率信号从COUNT1的时钟输入端 CLK输入,其频率为 Fo,待测信号从COUNT2的时钟输入端 CLK输入,设其实际频率为 Fxe,测量频率为 Fx。

当门控信号为高电平时,被测信号的上沿通过D触发器的Q端同时启动计数器 COUNT1和COUNT2。对被测信号 Fx和标准频率信号 Fo同时计数。当门控信号为低电平时,随后而至的被测信号的上沿将使这两个计数器同时关闭。

3.系统设计实现

3.1 预处理部分

为了获得 1s的预置门时间宽度,需要对 50MHz标准进行 100M分频,即分得频率为 0.5Hz,脉宽为 1s的脉冲。而这可由 4个 100分频器级联获得。所以需要设计一个 100分频器 FreDiv100。为了便于自测与自校,在上面所设计的100分频模块的基础上设计了占空比可调的 100分频模块FreDiv1_99,实现 100分频,并根据 ABCDEFG等 7个按键的二进制组合来产生占空比为 1%到 99%的脉冲。为实现等精度原理中的D触发器,其在本设计中单独设计成一个 D触发器模块D_Drigger。因该触发器是由触发时钟输入信号S触发的,故其输出信号 Q的脉宽为触发时钟输入信号 S的周期的整数倍。

3.2 测量部分

因为测量频率与测量周期的原理和所需要计数的对象是一样的,在至少 1s里分别对被测信号和标准信号进行计数,所以在本设计中,频率与周期的测量共用一个计数模块Counter。而脉宽和占空比的测量都是在被测信号的 100个连续周期里对标准信号进行计数的,只是它们计数的时间段不一样,即对应脉宽的计数值仅仅需在该 100个周期里的正脉宽里对标准信号进行计数,而对占空比则不仅仅需要在那100个正脉宽里对标准信号进行,还需要在该完整的 100个周期里对标准信号进行计数,也就是说,对脉宽的测量和占空比的测量都需要在该 100个周期里的正脉宽里对标准信号进行计数,基于这一点,我们应该把脉宽和占空比的测量集成到一个脉宽和占空比同步累加计数模块 CounADD。

3.3 控制部分

控制部分在本设计里,只是进行测量功能的切换,这并不包括对自校功能的控制。因为自校功能的控制与切换并不需要单独的模块,那只需一个按键与一些逻辑门就可以的了,所以控制部分就只设计了一个功能切换控制模块 Swap,实现频率测量、周期测量、脉宽测量和占空比测量的切换。

3.4 数据处理部分

图 2 等精度频率、周期、脉宽测量仪的顶层原理图

由于需要对前面测量模块计得的数值进行运算并加以码制转换和译码才能得到最终的测量结果,在本设计中,我们设计了数据处理需要用到的 32位二进制乘法器Multiplier和 32位二进制除法器 Divider32。

3.5 显示部分

由于最终结果是由数码管以十进制数显示的,而在之前的测量部分和数据处理部分里所用的数制都是二进制数,因此我们设计了二进制码转换成 BCD码模块 B2BCD,把二进制数码转换成十进制数码。另外,在本设计中,设计了 8个7段数码管的位选择器 Position Select,数码管段码选通模块Decode,数码管 (共阴极)译码显示模块 Display来实现 8个动态数码管的“扫描式”显示。

3.6 顶层原理图

根据前面所述各模块组成等精度频率、周期、脉宽测量仪的顶层原理图如图 2所示。

在图 2的输入和输出引脚说明如下:

LY为自校功能的切换开关,当其为 0时,用频率为 0.5MHz的标准脉冲进行自校;当其为 1时,用频率为 5KHz的标准脉冲进行自校。

CLK为标准时钟 50MHz的输入端,SIG为被测信号的测量输入端,START为测量开始控制开关,当其为 1时,真正的测量开始。

1、2、3 、4、5、6和 7是配合 LY开关使用的 ,即用它们对不同脉宽范围和占空比范围在实际上的测试与自校,主要是通过它们来改变自校信号的占空比以检测本设计能否完成指标中 1%到 99%的占空比的测试功能。

ALARM为计数溢出警报,计数超过或等于 4 294 967 295时,即计数的开放时间大于或等于 85 899 345 900ns警报响起表示所测量的频率超出量程,以此来计算,本设计的频率测量范围应为 0.0012Hz-85 899 345 900Hz(85GHz),可实际上,由于数码管的显示位数不够,所以那是看不到的。

H、W则是测量功能的切换控制开关,当 H、W都没有按下时进行的是频率测量;当 H按下、W没有按下时进行的是周期测量;当 H没有按下、W按下时进行的是脉宽测量;当H、W都按下时进行的则是占空比测量。

SEL[2..0]是输出到芯片上 38译码器的,Q1[6..0]是输出到静态数码管 1的,Q2[6..0]是输出到静态数码管 2的,Q3[6..0]则是输出到动态数码管的。

4.软件仿真与硬件测试

这里给出两个主要测量模块频率和周期同步计数模块Counter及脉宽和占空比同步累加计数模块 CounADD在 QUARTUSII6.0上时序仿真波形图分别如图 3、图 4所示。

图 3 频率和周期同步计数模块 Counter时序波形

图 3中 CLK的周期为 6ns,SIG的周期为 10ns。从上面的波形仿真图可以看出,对标准信号 CLK进行计数的计数值QA和对待测信号 SIG进行计数的计数值 QB的起始和终止都受 EN的控制,且呈现出一致性。

图 4 脉宽和占空比同步累加计数模块 CounADD时序波形

在图 4中,SIG的周期为 72ns(脉宽为 36ns),CLK的周期为 14ns(脉宽为 7ns),QA、QB分别为在 100个 SIG的正脉宽和周期里对 CLK的计数值。从图 4中可得出,36×100÷14=257≈256,511×14+49=7203,其中 49为开始对 CLK进行计数前的时间,即第 4个 CLK上升沿前的时间,3×14+7=7×7=49。另外,值得注意的是,QA、QB的计数起始和终止在本模块中是同步的,这保证了测量的一致性和精度。

最后,在最终的硬件测试中记录的几组数据:

在 LY=0,START=0时,测得频率为 0.5MHz(显示 5 000 000),周期为 2us(显示 200),脉宽为 0.99us(显示 99),占空比为 50%(显示 50)。另外,在 1234567的组合改变时,测得脉宽和占空比都随之变化,但脉宽总比理论值少 1,占空比测量正确。

在 LY=1,START=0时,测得频率为 5KHz(显示 50 000),周期为 200us(显示 20000),脉宽为 99.99us(显示9999),占空比为 50%(显示 50)。另外,在 1234567的组合改变时,测得脉宽和占空比都随之变化,但脉宽总比理论值少 1;占空比则能正确测量,1%和 99%也可以测量得出。

针对上述两种情况,可分析得出,就以上两组数据而言,本设计的误差是稳定的,脉宽的测量只有 0.01us的误差,而频率和周期则实现 0误差。

在 START=1时,测得的几组数据如表 1所示。

表 1 硬件测试结果

5.结束语

本设计根据等精度测频原理(高精度恒误差测频原理),以浙江天煌科技实业有限公司的“KHF-5型 CPLD/FPGA实验开发系统”为硬件基础,采用 VHDL语言进行设计,所选用的设计器件为 Altera公司的 EP1K100QC208-3。从仿真和实测结果可以看出该系统不但具有较高的测量精度,而且在整个频率区域保持恒定的测量精度。

[1]谢自美.电子线路设计·实验·测试 [M].武汉:华中科技大学出版社,2003.

[2]潘松.EDA技术与 VHDL[M].2版.北京:清华大学出版社,2007.