高速可变速率QPSK模拟源设计与实现

田之俊,段旭

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

高速可变速率QPSK模拟源设计与实现

田之俊,段旭

(中国电子科技集团公司第五十四研究所,河北 石家庄 050081)

通信系统带宽与速率逐步提高,要求与之匹配的模拟源速率相应提高。介绍一种高速且可变速率的QPSK调制模拟源的实现方案,数据速率为20~600 Mbps且每bit可变。详细描述了核心并行数控振荡器(NCO)及成型滤波模块的设计与实现,对工程应用以及测试结果进行了分析。结果表明模拟源各项功能指标达到了设计要求,设计灵活,可扩展性强,满足多速率通信系统的测试要求。

可变速率;QPSK;模拟源;数字控制振荡器

0 引言

四相相移键控(QPSK)是一种多进制调制方式,其基本思想就是利用4种不同相位来表征需要传输的数字信息特性。QPSK抗干扰能力强,具有较高的频谱利用率和较好的误码性能,且实现复杂度较小,解调理论成熟,在卫星通信、移动通信等领域得到广泛的应用[1]。

随着数字通信技术的飞速发展,数据传输业务不断增加,相应数据传输速率也越来越高。目前国内高达600 Mbps的数据传输系统正在研制,与之相对应的模拟源测试系统的需求也越来越迫切。现有的QPSK模拟源大多数据速率较低,且功能单一,不能满足高速数传系统多速率的测试要求[2]。针对这一问题,提出了基于FPGA的数字式高速可变速率模拟源的方案。

1 模拟源方案

针对高速数传系统的测试要求,模拟源的指标要求如下:

①载波:720 MHz/1 200 MHz;

②多普勒:范围±1 MHz,变化率45 kHz/s;

③扫描方式:正弦、线性;

④符号速率:20~600 Mbps每bit可变。

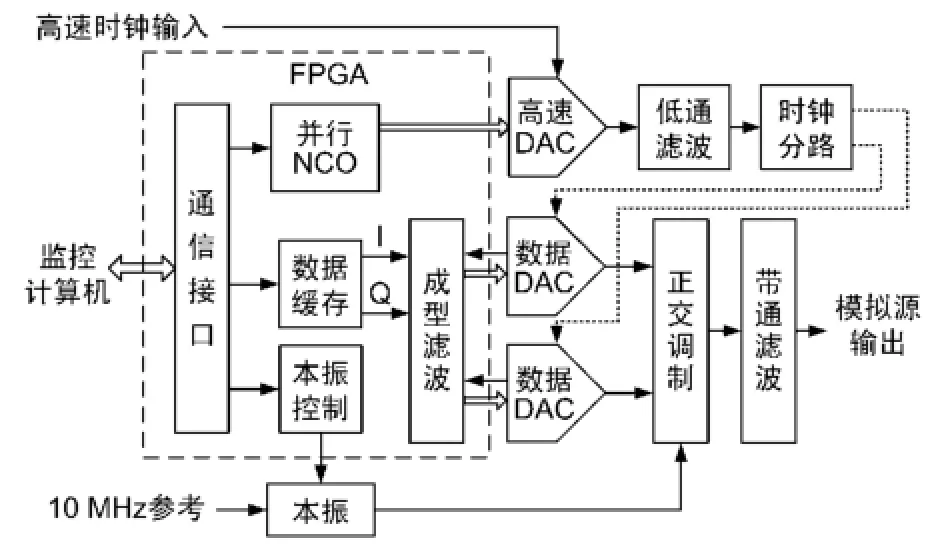

模拟源方案框图如图1所示。

图1 模拟源方案

要求数据速率为20~600 Mbps,且每bit连续可变,对于QPSK调制,相当于数据时钟在10~300 MHz范围内连续可变,精度小于1 Hz。这在FPGA内部无法实现,考虑采用高速DAC实现。通过并行NCO算法,控制高速DAC产生40~1 200 MHz的时钟信号,四分频后给FPGA作为可变的数据时钟。同时将时钟信号分路后作为2个数据DAC的工作时钟,将4倍内插、成型滤波后的I路和Q路数据转换成模拟信号输出,经过模拟正交调制及带通滤波后输出QPSK调制模拟源信号。

模拟源通过通信接口接收监控计算机下发的基带数据以及控制指令。基带数据存储到缓存模块,然后经过成型滤波器发送给数据DAC。控制指令包括数据速率和载波动态2种。数据速率指令通过下发频率控制字的方式控制并行NCO产生相应频率的数据时钟;载波动态指令控制本振模块产生相应动态特性的载波,包括线性扫描和正弦扫描2种模式,扫描范围和扫描速率等可设置。

2 核心模块设计

2.1 并行NCO设计实现

由方案分析可知,需产生最高频率为1 200 MHz的时钟信号,要求高速DAC的转换速率大于2.5 Gsps。根据FPGA内部工作频率要求,采用16倍降速处理,即16路NCO模块并行实现[3,4]。

设需要产生的时钟信号表达式为:

式中,fs为采样频率;f0为输出信号频率;n为采样点。16倍降速处理,对于每一路相当于对原始信号进行16倍抽取,并且每一路都有一个初始相位。设每路信号表达式为:

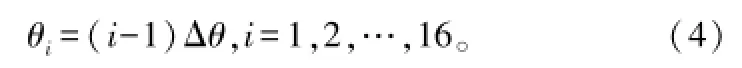

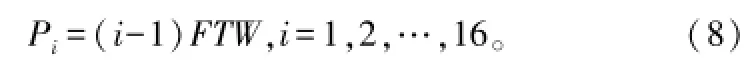

式中,fs′为各通道等效采样率;θi为各通道初始相位。根据数据抽取理论[2],有fs′=fs/16,且相邻通道之间的相位差一个采样点,即

故各通道初始相位为:

由于原始频率控制字为:

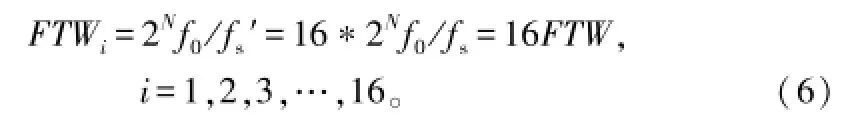

式中,N为频率控制字位宽。则并行NCO各通道的频率控制字为:

各通道初始相位控制字为:

将式(3)、式(4)和式(5)带入可得:

因此根据需要产生的时钟频率控制字,可计算出并行16个NCO的频率控制字与相位控制字,从而同时得到16个采样数据,发送给高速DAC,完成时钟信号的产生。

2.2 成型滤波器设计实现

2.2.1 成型滤波器设计

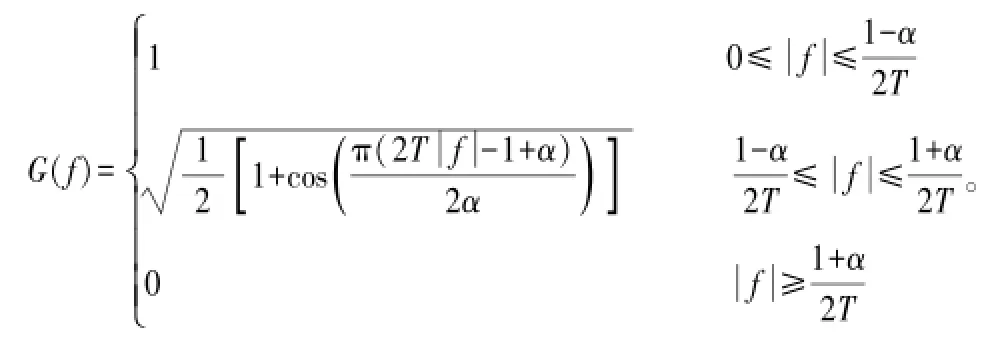

为了节约频谱资源,减小码间串扰,降低误码率,需要对发射信号进行带限,即成型滤波。根据奈奎斯特准则要求以及信号频谱特性,通常采用平方根升余弦滤波器,其传输特性[5,6]为:

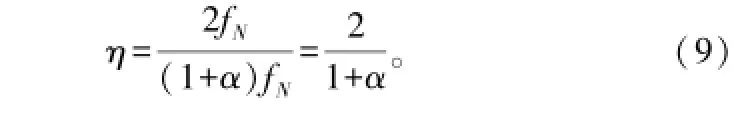

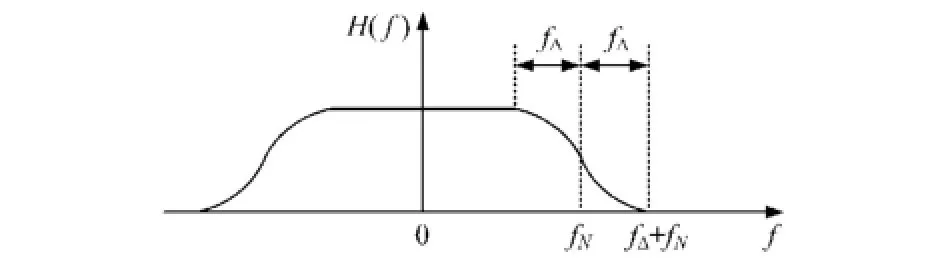

式中,T为码元周期;α为滚降系数,定义为α=fΔ/fN,如图2所示,fN为无码间串扰的理想低通特性带宽,即奈奎斯特带宽,fΔ为超出奈奎斯特带宽的扩展量。滤波器带宽B=fΔ+fN=(1+α)fN,而频带利用率定义为:

可见α越大,频谱在截止频率处越光滑,但是频谱利用率越低,需要根据实际情况综合考虑[7,8]。

图2 滚降定义

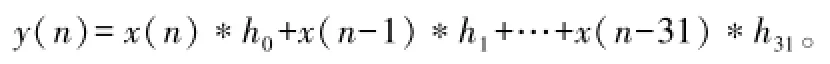

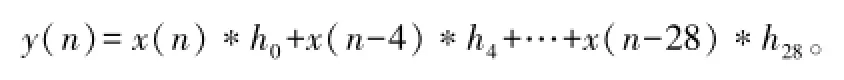

由开始分析知,本方案成型滤波为4倍内插滤波器,通过MATLAB工具FDATOOL进行仿真,综合考虑各指标以及实现难易程度,确定采用α=0.6、阶数32的平方根升余弦滤波器。假设其系数h0,…,h31,则滤波器可表示为:

式中,x(n)为基带数据映射值,数据1映射成1,0映射成-1。采用4倍内插多相结构,如果x(n)≠0,则有[9,10]

故有

同理可得

最高工作频率1 200 MHz的32阶内插滤波器,通过多相结构,可采用4个300 MHz的8阶滤波器实现,每个滤波器系数为原始滤波器系数的4倍抽取,大大降低实现难度。

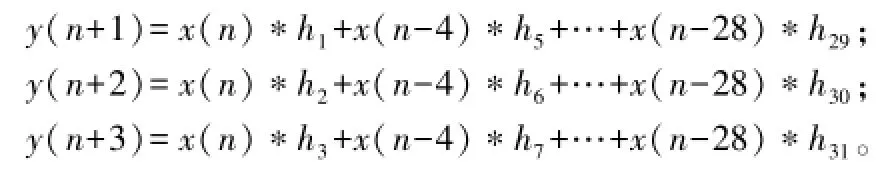

2.2.2 成型滤波DA算法实现

FPGA内部的高速滤波器通常采用分布式(DA)算法实现,即将乘加运算通过查找表、移位和累加等操作实现,提高运算速度,其实现结构如图3所示[11,12]。

图3 DA算法实现结构

系数表预先存储到查找表中,数据x(n)相应的位拼接组合作为查找表的地址,输出的数据乘以相应的2的幂次方后经过流水线加法器进行累加,最终得到滤波结果y(n)。其中N为滤波器阶数,B为x(n)的位宽。

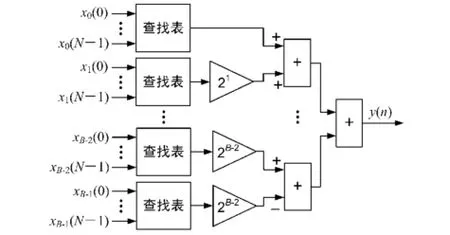

鉴于系统的特殊性,基带数据为单比特1/0数据,映射后为1/-1,将求和运算整合到查找表中,通过查表就可完成整个滤波运算。实现框图如图4所示。

图4 成型滤波实现

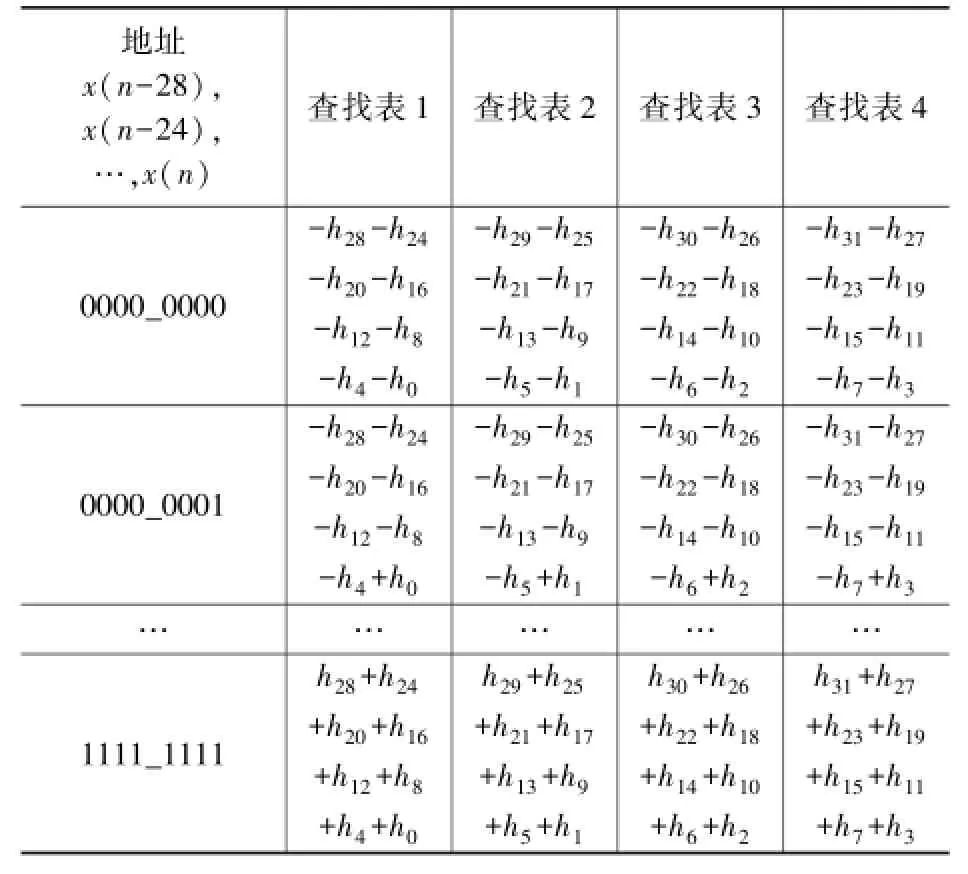

将4组系数分别整合成4个查找表,使用ROM实现,其深度为28=256,8为各滤波器阶数。位宽根据数据DAC的分辨率确定,为12位。滤波后并行数据由LVDS发送模块提速后输出给数据DAC。其中查找表内容如表1所示。

表1 查找表

3 工程实现与应用

3.1 平台实现

基于核心算法模块,处理器选用Altera公司FPGA-EP3SL340,其充足的内部资源及良好性能保证高速采集、存储和处理的顺利完成。

高速DAC选用e2v公司的12位高速DAC芯片EV12DS130,最高转换速率可达3 Gsps。综合考虑,取采样速率为2.7 Gbps,为了FPGA能稳定工作,采用16倍降速处理,FPGA内部工作时钟为168.75 MHz。为了保证数据速率精度,取32位的频率控制字以及相位控制字,输出时钟信号精度为2.7 GHz/232=0.629 Hz,数据时钟精度为0.629/4=0.157 Hz,远小于1 Hz,满足要求。

数据DAC选用ADI的12位DAC芯片AD9735,最高转换速率1 200 Msps,对应FPGA内部最高工作频率300 MHz,满足实现要求。由于数据速率覆盖范围大,AD9735转换速率从40~1 200 Msps,在不同频段对数据时延要求不同,需要通过其SPI控制端口调整LVDS控制寄存器的数据建立、保持时间,保证时序稳定,输出频谱纯净。

3.2 应用与分析

目前模拟源已在某高速数传系统中得到应用,各模块工作正常,各项功能及技术指标均达到了设计要求。通过监控指令可灵活控制调制数据速率,满足系统多种情况的测试要求。

针对大范围数据速率下的时序问题,模拟源自动根据数据速率估算数据DAC的延时要求,通过内部LVDS控制寄存器微调数据总线的时延,包括数据建立时间和保持时间,保证时序稳定。

4 结束语

采用高性能FPGA为算法核心,转换速率高达3 Gsps的超高速DAC为基础,辅助2个高速DAC开发的硬件平台,为高速模拟源的实现提供了硬件基础;并行NCO、多相滤波器等高速并行数字信号处理算法的研究、推导与分析,为数字式模拟源实现提供了理论依据;通过高速时序设计、时序约束等设计调试方法,保证了模拟源各项功能指标的稳定可靠。测试和实际使用证明,该模拟源系统操作简单、使用方便、功能强大、工作稳定可靠,达到了预期的设计目标。

[1]郝英川,吴海燕.采用FPGA实现突发QPSK调制器[J].无线电工程,2007,37(1):59-60.

[2]邓建华.高速数传系统中的直接数字射频调制解调技术[D].成都:电子科技大学,2003.

[3]费义伟.基于FPGA的调制解调器的设计[D].哈尔滨:哈尔滨工业大学,2007.

[4]窦宇洋.卫星通信中的高速数传调制技术研究[D].长沙:国防科学技术大学,2003.

[5]皇甫堪,陈建文,楼生强.现代数字信号处理[M].北京:电子工业出版社,2003:401-475.

[6]张松轶.基于FPGA的平方根升余弦滤波器设计[J].无线电通信技术,2012,38(3):43-46.

[7]李爱红,肖山竹,张 琛,等.高速成形滤波器的设计与实现[J].电路与系统学报,2006,11(5):90-92.

[8]张 琛,朱 江,张尔扬.高速数传系统中成形滤波器的研究[J].通信技术,2002(10):18-19.

[9]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001:8-57.

[10]陈东华.升余弦滚降基带成形内插滤波器的FPGA实现[J].华侨大学学报,2006,27(3):310-312.

[11]张维良,郭兴波,潘长勇.平方根升余弦滚降FIR数字滤波器的设计[J].电讯技术,2002(6):51-55.

[12]张建伟,展雪梅.FIR数字滤波器的设计与实现[J].无线电工程,2010,40(6):54-56.

Design and Implementation of High and Variable Rate QPSK Signal Simulator

TIAN Zhi-jun,DUAN Xu

(The 54th Research Institute of CETC,Shijiazhuang Hebei 050081,China)

The bandwidth and data rate of communication systems are gradually increasing,which requires a corresponding increase in the rate of the simulating source.The implementation scheme of a high and variable data rate QPSK simulating source is introduced,in which the data rate changes from 20 to 600 Mbps with an accuracy of one bit.The design and implementation of the core module including the parallel numerical controlled oscillator and the shaping filter are described in detail.The system engineering appli-cations and test results are analyzed.The results show that the function specifications of the simulating source meet the design require-ments.The system is flexible and easily expanded,which meets the test requirements of multi-rate communication system.

variable data rate;QPSK;signal simulator;NCO

TTN911

A

1003-3106(2015)11-0077-04

10.3969/j.issn.1003-3106.2015.11.20

田之俊,段 旭.高速可变速率QPSK模拟源设计与实现[J].无线电工程,2015,45(11):77-80.

田之俊男,(1986—),硕士,工程师。主要研究方向:航天测控、阵列信号处理。

2015-08-21

国家部委基金资助项目。

段 旭男,(1981—),高级工程师。主要研究方向:航天测控、通信与信号处理。