生长界面对掺钒SiC电阻率的影响

戴 鑫,王英民,毛开礼,王利忠,徐 伟,李 斌

(中国电子科技集团公司第二研究所山西太原030024)

生长界面对掺钒SiC电阻率的影响

戴 鑫,王英民,毛开礼,王利忠,徐 伟,李 斌

(中国电子科技集团公司第二研究所山西太原030024)

碳化硅(SiC)单晶多采用物理气相传输(PVT)法及籽晶顶置工艺生长,典型的生长界面包括略凹、近平微凸、略凸三种生长界面,在100 mm(4英寸)掺钒(V)半绝缘4H-SiC单晶生长过程中,需要研究不同生长界面对SiC单晶电阻率的影响,得到合适的生长界面。在近似的生长条件下,采用略凹、近平微凸、略凸三种生长界面生长出100 mm掺V半绝缘4H-SiC单晶,加工后进行了电阻率测试、应力等测试,结果表明近平微凸生长界面易于调整掺杂浓度,晶体缺陷少,适合生长电阻率均匀的掺V半绝缘4H-SiC单晶,且晶体出片率高。

掺钒半绝缘;4H-SiC;电阻率;应力

SiC由于其优良的物理性质和电学特性,是极佳的宽带隙半导体材料,作为衬底材料适用于制作高频器件及大功率和抗辐射器件,尤其在某些特定环境下,以SiC为衬底制成的器件显示了其它材料无法替代的优越性[1]。半绝缘SiC衬底电阻率的分布对固态微波器件的制作和性能有非常重要的意义,目前多采用在SiC材料中掺入V,在其禁带中引入深补偿能级,束缚过剩的载流子完成补偿作用,从而形成半绝缘[2,3]。随着SiC器件的技术进步,要求更大直径的SiC衬底以降低成本,提高产率。而我国正在投入的主要为100 mm SiC器件生产线,这就要求高质量的100 mm半绝缘SiC衬底以满足当前的需求。

掺V半绝缘4H-SiC单晶的电阻率受多方面影响,包括设备真空度,粉料氮(N)含量,掺V浓度,热场分布等。我们通过生长试验发现热场分布表现为晶体生长界面,其对晶体电阻率分布具有重要的影响。本文通过生长不同生长界面的100 mm 掺V半绝缘SiC单晶,利用多种测试设备进行表征分析,研究了不同生长界面对100 mm掺V半绝缘4H-SiC单晶的影响。

1实 验

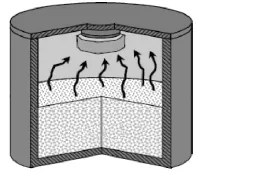

本实验使用中国电子科技集团公司第二研究所自行研制的TDS-100C碳化硅单晶炉,采用PVT法生长100 mm掺V半绝缘4H-SiC单晶。该设备采用中频感应加热方式,利用光学高温计测量温度。使用双面抛光的4H-SiC晶片作为籽晶,置于高纯石墨坩埚上部,生长面为碳面。自主合成的高纯SiC粉料以及掺杂的料源V则置于坩埚底部。高纯石墨坩埚和高纯SiC粉料有利于减少生长过程中背景N的掺入,降低对掺V半绝缘的影响[2]。生长基本结构原理如图1所示。

通过调整温场生长出了三种不同生长界面的100mm掺V半绝缘4H-SiC单晶。各晶体采用相同的掺V生长工艺,生长后的晶体经过滚圆、定向、切割、研磨、打标、抛光工序,完成100 mm掺V半绝缘4H-SiC晶片的加工,其中晶片均为正<0001>方向,按晶体表面至籽晶方向由小到大排序。抛光晶片按序号使用非接触式电阻率测试仪(COREMA)在室温条件下测量其电阻率。使用莱卡体式显微镜观察晶片应力及微管。

图1 PVT法坩埚内部结构

2 结果与讨论

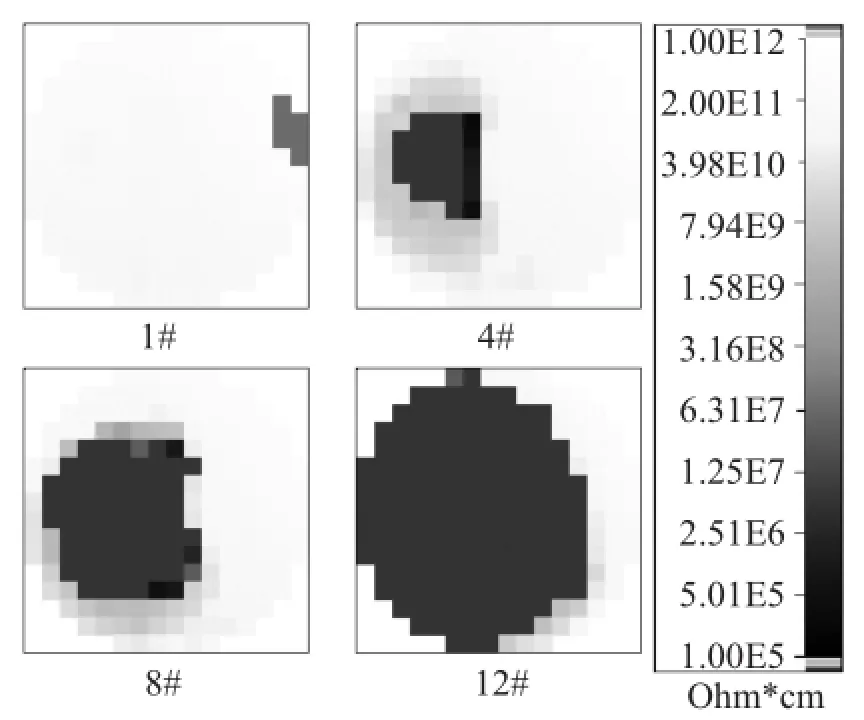

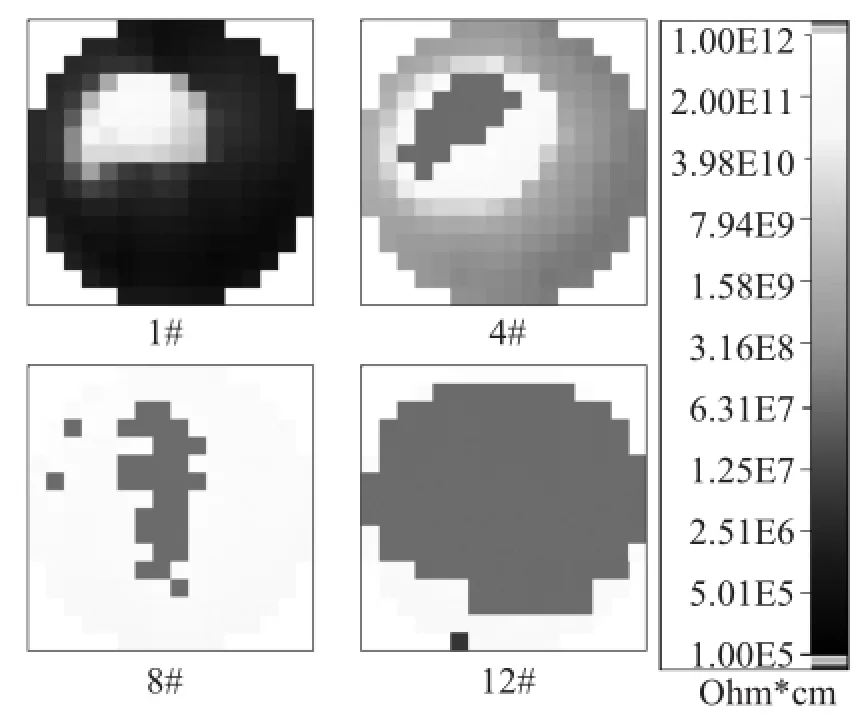

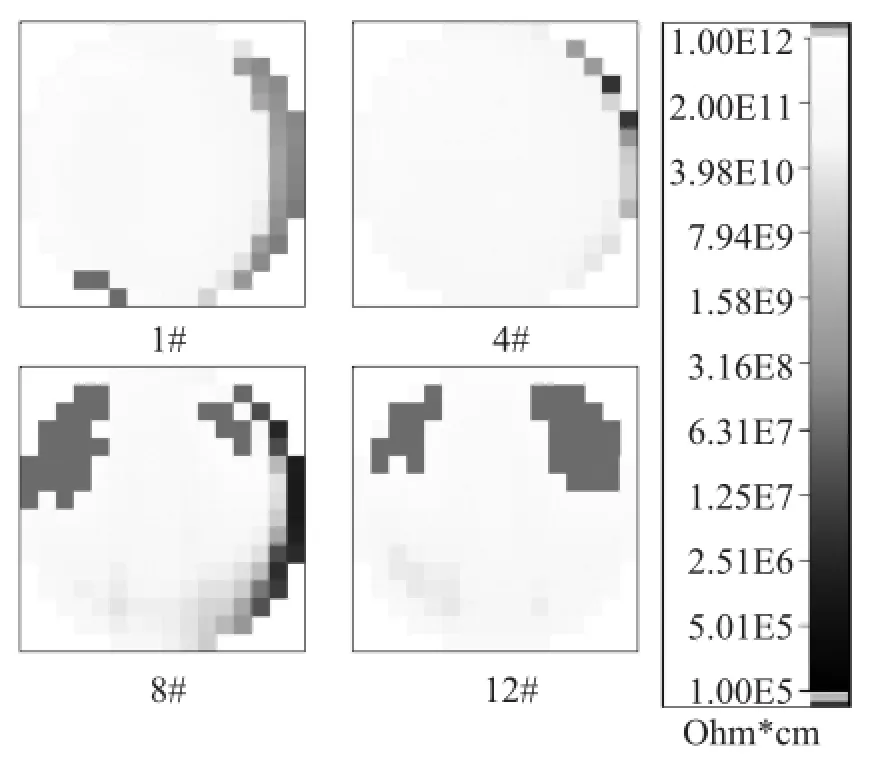

2.1电阻率测量

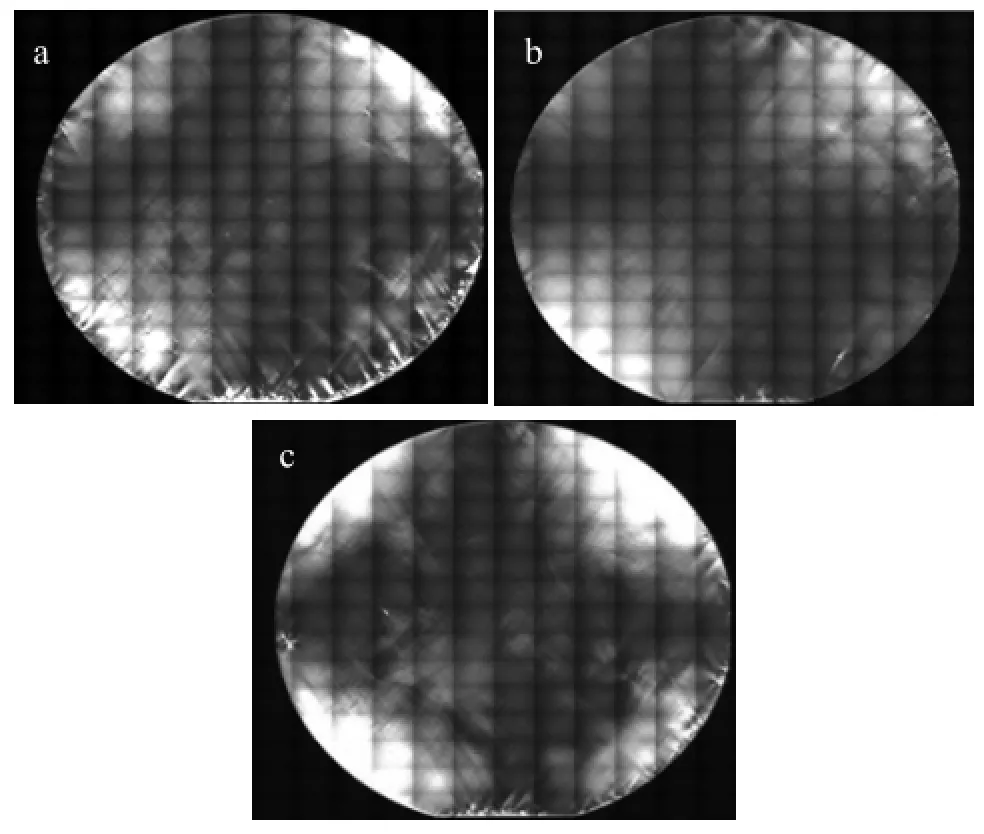

三种不同生长界面的100 mm掺V半绝缘4H-SiC晶片各选择了4片测试电阻率,序号均为1#、4#、8#、12#。抛光晶片按序号使用非接触式电阻率测试仪(COREMA)在室温条件下进行测量,图2~4为三种不同生长界面生长晶体所加工晶片的电阻率分布情况,其中略凸晶体晶片电阻率分布图的结果可观察到随着晶体生长晶片的电阻率由边缘逐步向中心增多,且边缘电阻率大;略凹晶体晶片电阻率分布图的结果可观察到随着晶体生长,晶片全片均有较高的电阻率,随着生长逐步降低,且边缘下降较快;近平微凸晶体晶片电阻率分布图的结果可观察到晶片全片均有较高的电阻率,且4片晶片电阻率较均匀。

图2略凸晶体晶片电阻率分布图

从电阻率测试结果分析,发现晶片电阻率和生长界面有直接关系,其中略凸晶体的中心生长速度快,边缘至中心的径向温度梯度大,晶体中心相对边缘较冷,有利于N的聚集,而为了补偿浅施主N掺杂会导致电阻率低[4]。对于实验所使用的坩埚而言,较凸的晶体意味着高温区位置偏上,粉料中的轴向温梯较小,粉料中残留的N消耗速度较慢,掺杂的V掺入晶体的速度也较慢,晶片在生长后期随着N浓度的降低和V浓度的升高电阻率才有明显的提高,电阻率合格率低;略凹的晶体则在生长前期就出现很高的电阻率,而随着生长逐步降低,其正径向温度梯度为中心附近至边缘,边缘的电阻率相对较低,较凹的晶体意味着高温区位置偏下,粉料中的轴向温梯较大,粉料中残留的N消耗速度较快,前期掺杂的V较多;近平微凸的晶体在生长前期也出现较高的电阻率,且较稳定,直到生长后期电阻率开始下降,说明此生长界面下温场条件较合适,晶体径向温梯和轴向温梯合适,V掺杂浓度能够很好地补偿晶体中的浅施主N,后期由于V浓度的降低使得电阻率开始下降。

图3略凹晶体晶片电阻率分布图

图4近平微凸晶体晶片电阻率分布图

图5 a、b、c晶片正交偏振透视图

2.2光学测试

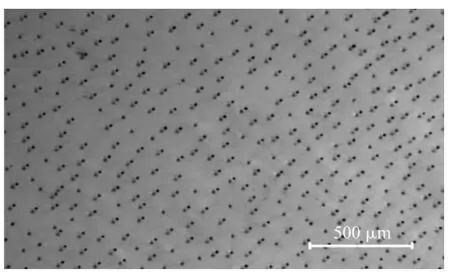

图6略凹晶体晶片局部缺陷图

中的溶解度(5×1017个/cm3)从而析出[5],导致大量缺陷。

3结 论

通过对略凹、近平微凸、略凸三种生长界面生长的100 mm掺V半绝缘4H-SiC单晶晶片的电阻率和光学显微测试,结果表明略凹生长界面易导致前期V析出产生大量缺陷及边缘应力差,略凸生长界面生长单晶半绝缘晶片电阻率合格率低,且应力大,晶体易开裂,近平微凸生长界面生长单晶易于调整掺杂浓度,适合生长电阻率均匀的掺V半绝缘4H-SiC单晶,且应力好、晶体缺陷少,晶体出片率高。

[1] M.E.Zvanut,Wonwoo Lee,W.C.Mitchel,etal.The acceptor level for vanadium in 4H and 6H SiC[J].Physica B:Condensed Matter,2006,376-377:346-349.

[2] Zvanut M E,Konovalov V V,Wang H,et al.Defect Levels And Types Of Point Defects In High-Purity And Vanadium-Doped Semi-Insulating 4H-SiC[J].Journal of Applied Physics,2004,96(10):5484-5489.

[3] M.Bickermann,R.Weingartner,A.Winnacker.On the Preparation of Vanadium Doped PVT Growth SiC Boules with High Semi-insulating Yield[J].Journal of Crystal Growth,2003,254:390-399.

[4] Janzén E,Son N T,Magnusson B,et al.Deep Levels Responsible for Semi-Insulating Behavior in Vanadium-Doped 4H-SiC Substrates[J].Silicon Carbide&Related Materials,2008,600-603.

[5] M.F.MacMillan,W.Mitchel,J.Blevins,et al.Evaluation of Test Methods Employed for Characterizing Semi-Insulating Nature of Monocrystaline SiC Semiconductor Materials[C]//Proc of CS MANTECH Conf.Chicago,Illinois,USA,2008:14-17.

Effect of the Growth Interface Shape on the Resistivity in V-doped SiC Crystal

DAI Xin,WANG Yingmin,MAO Kaili,WANG Lizhong,XU Wei,LI Bin

(The 2ndResearch Institute of CETC,Taiyuan 030024,China)

There are three typical growth interface shapes in top-seeded growth of Silicon Carbide(SiC)crystal by Physical Vapor Transport(PVT)method.They are concave interface,slightly convex near horizontal interface and convex interface.We growed V-doped 4 inch SiC crystals by three different growth interface shapes under similar growth conditions.These crystals has been machininged to wafers.We tested wafes'resistivity and stresses.The test results show that using slightly convex near the horizontal growth interface during the process can easily adjust doping concentration and reduce defects in SiC crystal.And the 4H-SiC crystal will have uniform resistivity with high output of high quality SiC wafers.

V-doped semi-insulating;4H-SiC;Resistivity;Stresses

O613.7,N33,N34

A

1004-4507(2016)06-0037-04

戴鑫(1983-),男,山西运城人,工程师,硕士,研究方向为宽禁带半导体材料制备。

2016-05-09

国家自然科学基金(项目号61404117);国家高技术研究发展计划(项目号2014AA041401)。