3G-ALE 短波信号信道化接收机高效设计*

周群群姚亚峰许思耀何坐伟

(中国地质大学机械与电子信息学院,湖北 武汉 430074)

短波通信主要通过电离层反射进行远距离传输或通过地波进行近距离传输,具有投资小、建台快、易维护、无中继和抗毁性强等特点,成为军事通信和应急通信等领域一种不可替代的重要通信方式[1]。电离层的反射传播存在多径效应和多普勒效应,严重影响短波链路的质量,而且传播的环境复杂多变,短波链路的时效性差,因此提高接通率、改善通信质量最为有效的一种途径是实时地选出质量较好的信道并快速建立链路[2]。早期短波通信系统依靠人工选频、切换信道等操作来建立链路,建链耗时较长,而且对操作人员的专业能力要求很高,因此,从上个世纪八十年代开始自动链路建立技术便得到快速发展[3]。

第三代自动链路建立(The Third Generation of Automatic Link Establishment,3G-ALE)技术[4]在建链握手过程和链路质量分析等方面提出了明确的规定,因此可以有效缩短建链时间。美国军方于1999年颁布军用短波通信标准MIL-STD-188-141B[5],并于2011 年修订为MIL-STD-188-141C[6],我国于2007 年颁布的军用短波通信标准GJB 2077A-2007[7],均采用了3G-ALE 技术。但是3G-ALE 短波电台通过依次扫描存放于扫描列表中的呼叫信道来检测呼叫或进行链路质量分析,并不利于快速有效地选频建链,尤其在异步模式下主叫电台一般需要花费很长时间在多个信道上进行呼叫才可能到达被叫电台当前的监听信道。

基于多相DFT 滤波器组的信道化接收机[8-9]通过多路信号的宽带并行接收,能够直接加快全频段上的信道扫描速度,其在FPGA 等高速处理芯片中的实现达到了实用化水平[10],在电子侦察和联合作战[11]等领域均有广泛应用。在短波通信领域,由于这种并行接收的信道化技术能够极大地缩短建链的时间,近年来成为了研究热点,文献[12]采用了基于加权叠接相加(WOLA)滤波器组的实现结构,然而只对理想单频信号进行了测试,文献[13]采用了基于多相DFT滤波器组的实现结构,然而只对3G-ALE 的同步前导序列进行了单路测试,均没有搭建多路3G-ALE 短波信号的测试环境,不利于实际性能分析,而且信道组及其组内信道的划分均存在较多的无效信道。论文将结合3G-ALE 短波信号频率较低、信道带宽窄、信道个数多的特点,设计一种基于WOLA 滤波器组的射频直采信道化接收机,将信道化的输出采样频率直接匹配为后续处理模块需要的采样频率,同时在信道划分时使组内有效信道全覆盖,最后进行3G-ALE 短波信号的完整性能测试,对缩短军用短波电台的建链时间具有重要意义。

1 3G-ALE 短波信号突发波形的特点

军用短波通信标准指出不同类型的信息在载荷、时长、同步和解调性能等方面有特定的要求,MIL-STD-188-141B 标准针对性地定义了5 种不同类型的突发波形,简称为BW0~BW4[5],其中BW0负责通信链路自动建立,BW1 负责业务管理以及高速数据链路应答消息传输,BW2 负责高速业务传输,BW3 负责低速业务传输,BW4 负责低速数据链路应答消息传输。下面以MIL-STD-188-141B 标准定义的BW0 为例来说明3G-ALE 短波信号突发波形的特点。

BW0 的有效载荷为一个26 bits 的协议数据单元,首先经过码率为1/2、约束度为7 的卷积码编码器输出52 bits 的编码数据。接着采用一个4 行13 列的交织矩阵以按行写入、按列读出的方式进行交织。然后将每4 bits 映射为长度为64 的八进制的正交扩频码,52 bits 的编码数据被映射为832 个扩频符号。接着将长度为832 的八进制的固定PN 序列与扩频符号序列进行模八相加,得到信道符号序列。最后将长度为256 的八进制的固定保护序列、长度为384 的八进制的固定前导序列与上述长度为832 的信道符号序列拼接,得到一个由1472 个八进制符号组成的BW0波形帧。BW0 波形帧属于基带信号,需要经过8PSK符号映射和数字上变频将频谱从基带搬移到射频,然后经过DAC 转换为模拟射频信号。

BW0~BW4 只是产生相应波形帧的方式不同,但是基带信号的符号速率均为2 400 symbol/s,调制方式均采用8PSK 调制,因此,3G-ALE 短波信号的信道化接收机能够适用于所有类型的突发波形,在进行信道化接收机设计时不需要考虑BW0~BW4 之间的差异,不同类型突发波形的同步检测、解调和解码等基带处理则由信道化之后的模块来完成。显然,在发射端,8PSK 映射之后的符号速率仍然为2 400 symbol/s,可以采用滚降系数为0.25 的平方根升余弦滤波器进行4 倍插值滤波,此时信号的频率范围被限制在-1.5 kHz~1.5 kHz 之间,采样频率为9.6 kHz,需要通过级联插值滤波将采样频率转换为至少是短波信号最高频率的两倍即60 MHz,可以设计为73.728 MHz,混频之后的射频信道带宽为3 kHz。在第i个信道上发射的数字射频信号可表示为:

式中:fi为第i个信道的载波频率,ft为射频采样频率,Ii(n)和Qi(n)分别是经过成形滤波和级联插值滤波之后的同相和正交基带脉冲序列。由于射频的频率范围为1.5 MHz~30 MHz,可以进行均匀的信道划分,因此fi=1.5×106+1.5×103×i,单位为Hz。由于单个信道带宽为3 kHz,总的信道个数将多达9 500 个。可见,3G-ALE 短波信号具有频率较低、信道带宽窄、信道个数多的特点,在进行信道化接收机设计时需要予以考虑。

2 WOLA 滤波器组信道化接收机的设计

2.1 总体方案设计

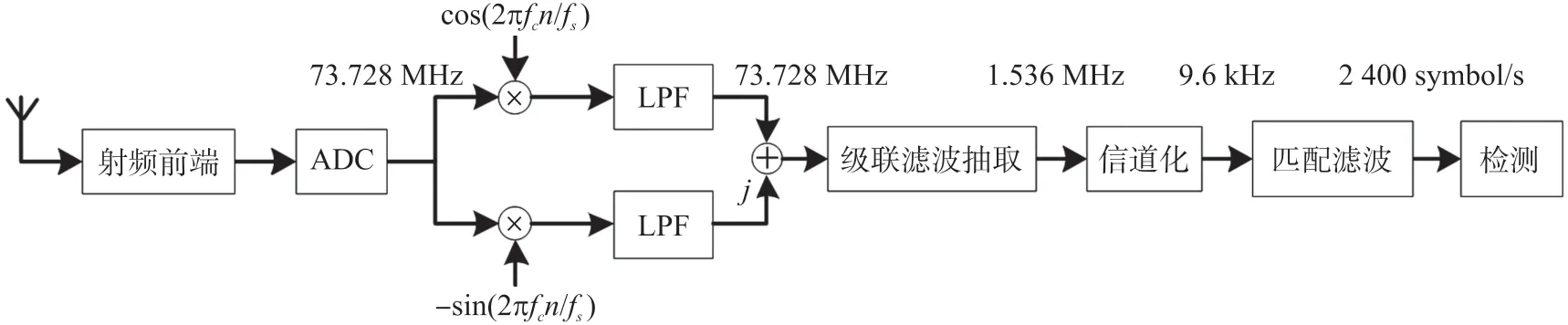

由于短波射频信号的频率较低,采用射频数字化方案[13]可以进行射频直采的正交下变频处理,将扫描频段的射频信号直接搬移到基带,得到接收实信号的基带复信号表示,然后进行信道化的处理得到多路信号的并行输出,这种射频直采的信道化方案不但可以减少硬件实现的体积、重量和成本,而且可以有效加快信道扫描速度,从而极大缩短建链时间。3G-ALE 短波信号的射频数字化方案的总体结构如图1 所示。

图1 射频数字化方案的总体结构

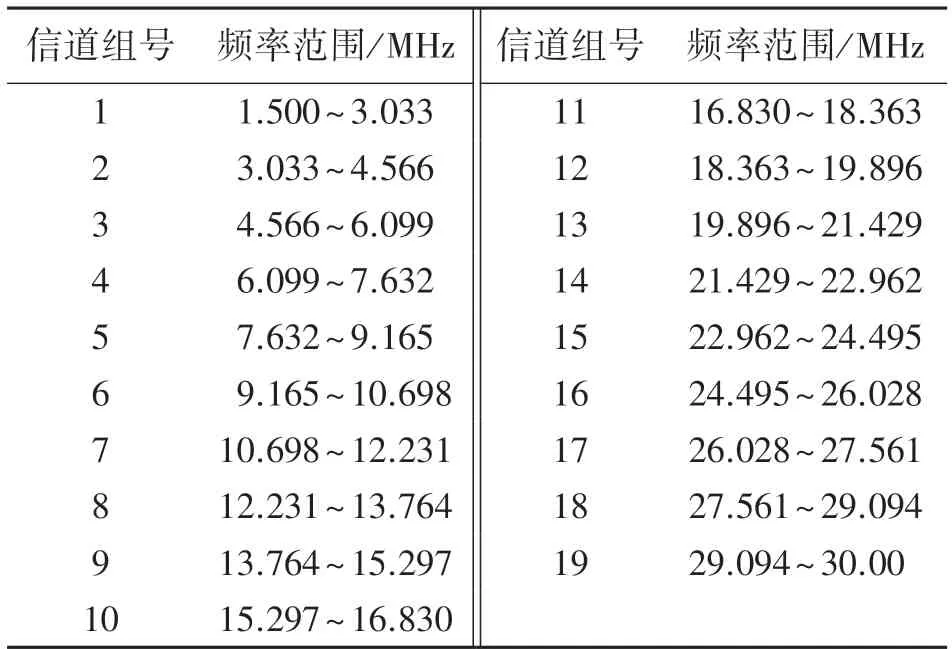

射频前端只对接收的模拟信号进行滤波和低噪声放大,对于1.5 MHz~30 MHz 的短波信号,ADC 的采样频率设计为73.728 MHz,满足奈奎斯特采样定理。正交下变频中的fs为采样频率即73.728 MHz,fc为混频频率,等于扫描信道组的中心频率,为了提高扫描效率,使运算量被有效利用,首先给出信道组的划分如表1 所示。

表1 信道组的划分

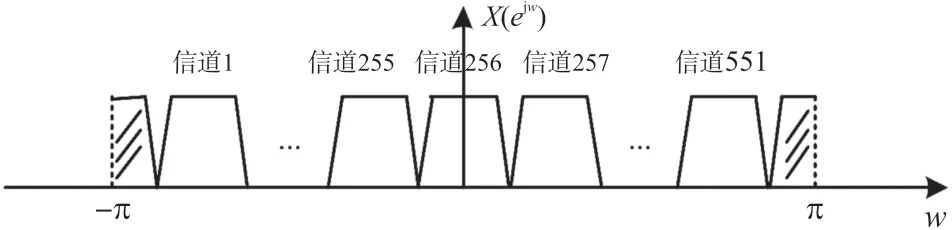

由于信道个数有9 500 个,直接进行9 500 路信道化的并行接收对高速处理芯片的要求极高,现有的方案通常将全频段划分为多个信道组,然后在信道组上进行信道化的并行接收,这样可以有效降低系统的运算复杂度,有利于硬件实现。如表1 所示,设计每个信道组包含511 个信道,带宽为1.533 MHz,9 500 个信道被划分为19 个信道组,当然,最后一个信道组的有效信道只有302 个。正交下变频之后,扫描信道组的基带复信号的频率范围为-0.766 5 MHz~0.766 5 MHz,此时设计采样频率为1.536 MHz,满足奈奎斯特采样定理。可见,级联滤波抽取的倍数一共为73.728 MHz/1.536 MHz=48 倍,在进行各级滤波器的设计时需要考虑通带截止频率、阻带截止频率和阻带衰减等指标,保证通带的带外衰减至少达到80 dB。显然,经过正交下变频的频谱搬移,给出扫描信道组的组内信道排列如图2 所示。

图2 信道组的组内信道排列

如图2 所示,理论上,1.536 MHz 的带宽范围内可以容纳的信道个数为1.536 MHz/3 kHz=512 个,可以作为信道化模型的信道个数,这样就可以进行FFT 快速运算。实际上,考虑到奇型排列下的信道化实现结构在硬件实现时的运算量较小[14]以及实际过渡带的影响,因此设计有效信道个数为511 个是合理的,此时有效信道率为511/512,运算量被有效利用,建链时间可缩短为单路接收时的1/511。当然,对于最后一个信道组,只有第1~302 个信道是有效的。

如图1 所示,正交下变频的输出采样频率为1.536 MHz,信道化的输出包含512 个支路,如果采用常用的基于多相DFT 滤波器组的信道化接收机[13],那么信道化的输出采样频率将固定为信道带宽即3 kHz,然而,后续匹配滤波器要求输入采样频率为9.6 kHz,这样就要求进行额外的频率转换,即完成采样频率由3 kHz 到9.6 kHz 的转换,对于511个有效支路来说,其运算量是很大的。因此,将采用一种基于WOLA 滤波器组的实现结构[12],其信道化的输出采样频率可变,能够避免额外的频率转换,有利于硬件实现。

2.2 WOLA 滤波器组结构

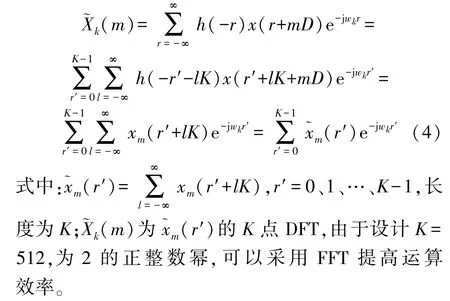

WOLA 滤波器组结构可以将信道化的输出采样频率直接匹配为后续处理模块需要的采样频率[15]。假设信道化的输入为x(n);原型低通滤波器的时域冲击响应为h(n),理想截止频率为K为支路个数,设计K=512,则第k个支路的输出可表示为:

令r=n-mD,式(2)可进一步表示为:

式中:令xm(r)=h(-r)x(r+mD),则为xm(r)的K点频率取样DFT,但是当K取值较大时,为了达到较好的低通滤波性能,h(n)的长度通常很长,xm(r)的长度等于h(n)的长度,因此的运算量会非常大。为了降低DFT 的离散时间序列长度并采用FFT 快速运算,将长的序列xm(r)折叠为K点序列,即分组之后叠加,有:

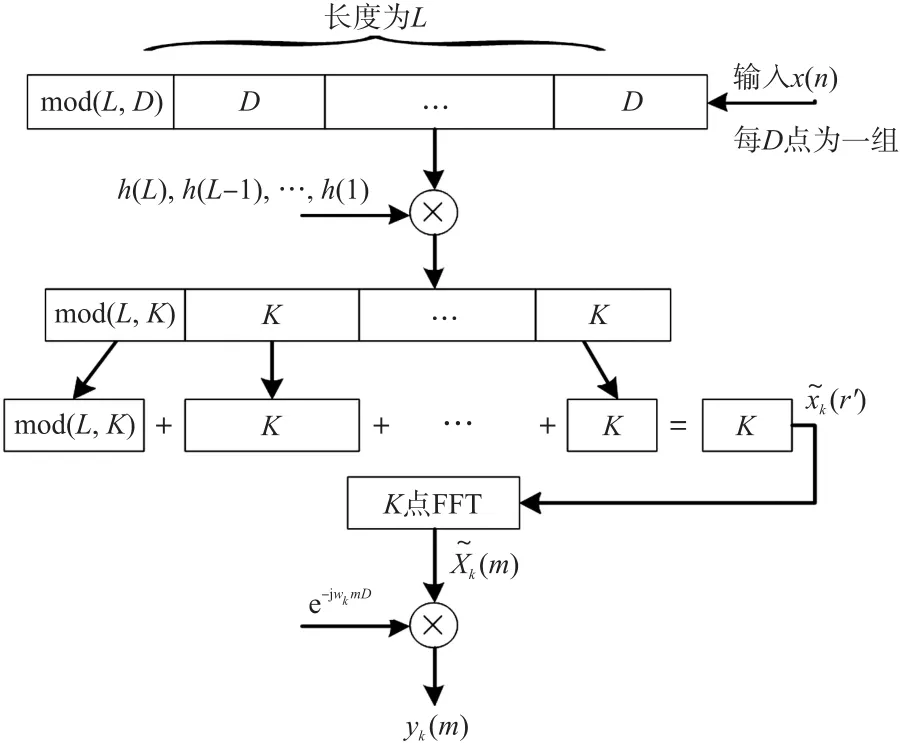

根据式(3)和式(4),得到WOLA 滤波器组的实现结构如图3 所示。

图3 中,L表示h(n)的长度,由于h(n)的理想截止频率为需要设计一个高阶的原型低通滤波器才能较好地分离出各个信道上的信号,因此,设计L=5 120。WOLA 滤波器组的实现步骤为:

图3 WOLA 滤波器组的实现结构

(1)输入,每次输入D个样本点;

(2)加权,将h(L)、h(L-1)、…、h(1)与长度为L的移位寄存器中序列的对应位置元素相乘;

(3)叠接相加,首先将加权之后的序列分为若干段,每段长度为K,由于设计中的L能够被K整除,因此一共有L/K=5 120/512=10 段,然后将各段相加;

3 仿真及其结果分析

为了准确分析由信道化的多路并行接收导致的接收信号质量变化,引入同步捕获概率和误码率作为性能指标,并在MIL-STD-188-141B 标准定义的BW0 上进行测试。在发射端,分别在第1 个信道组的511 个信道上随机产生1 个26 bits 的协议数据单元,上变频过程中从9.6 kHz 到73.728 MHz 的频率转换需要进行7 680 倍插值滤波,通过9 级半带插值滤波、1 级3 倍插值滤波、1 级5 倍插值滤波来完成。采用AWGN 信道来模拟短波通信环境,设置3 kHz 带内SNR 以3dB 为间隔从-9 dB 到30 dB 变化。在接收端,从73.728 MHz 到1.536 MHz 的频率转换需要进行48 倍滤波抽取,通过2 级4 倍滤波抽取、1 级3 倍滤波抽取来完成。使用MATLAB 中的fir1 函数得到各级滤波器的系数。用于同步捕获的门限值设置为200,只在同步捕获成功的信道上统计误码率,因此需要对信道化的各路输出分别进行匹配滤波、前导序列同步检测、8PSK 反映射、解扰、解扩、解交织和维特比译码。

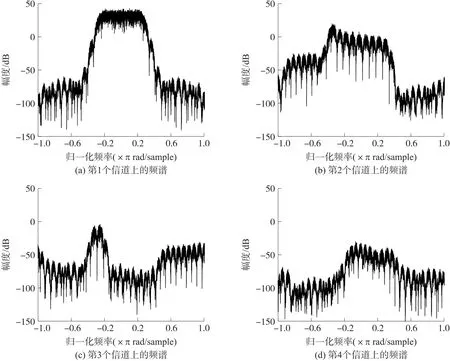

为了直观分析该信道化接收机的并行接收效果,在无噪声的环境下,在第1 个信道组的第1 个信道上发射一个随机产生的协议数据单元,给出在第1 个信道组第1、2、3、4 个信道上WOLA 信道化输出的频谱,如图4 所示。

图4 WOLA 信道化输出的频谱

图4 中,并行输出的采样频率为9.6 kHz,第1个信道上信号带宽为3 kHz,为有用信号,第2、3、4个信道上均为无用信号,主要由各级滤波过程中产生的镜像信号混叠而成。可见,该信道化接收机可以分离扫描频段上的接收信号,得到并行输出的多路信号。

下面给出同步捕获概率和误码率的测试结果,如图5 所示,同时给出单路接收时的测试结果,对于信道化的多路并行接收,进行了10 次511 个并行支路上的测试,对于单路接收,进行了100 次单个信道上的测试,结果均取平均值。

图5 性能测试结果

如图5 所示,当SNR 低至-9 dB 时,同步捕获概率甚至可以达到100%。随着SNR 增加,误码率逐渐降低,对于单路接收,当SNR 高于18 dB 时,误码率降低为0,对于多路并行接收,当SNR 高于18 dB时,误码率达到10-4量级,当SNR 高于24 dB 时,误码率降低为0。整体上,与单路接收相比,多路并行接收时的误码率变化很微小,表明该信道化接收机不会因为并行接收而降低信号接收质量。

5 结论

结合3G-ALE 短波信号频率较低、信道带宽窄、信道个数多的特点,设计了一种基于WOLA 滤波器组的射频直采信道化接收机,同时提出了信道组内有效信道全覆盖的方式,使建链时间缩短为单路接收时的1/511。比较分析了WOLA 滤波器组的运算复杂度,表明该信道化接收机的运算效率较高,有利于硬件实现。进行了3G-ALE 短波信号的完整性能测试,当SNR 低至-9 dB 时同步捕获概率甚至可以达到100%,当SNR 高于24 dB 时误码率为0,与单路接收相比,该信道化接收机不会因为并行接收而降低信号接收质量。