一种改进的动态可重构信号处理平台设计

李声飞

(中国电子科技集团公司第十研究所, 成都 610000)

1 引言

综合传感器系统是飞机航电系统的重要组成部分,采用综合一体化的设计思想,对通信、导航、识别、雷达等功能进行一体化设计,完成特定的作战任务是保障飞机安全、遂行作战任务的重要组成部分。信号处理平台是综合传感器系统的数据处理中心,承担了大量传感器数据的实时处理和传输,平台的技术水平对飞机作战效能至关重要。传统的信号处理平台采用多个FPGA+DSP的设计架构,每个通道上独立运行不同的功能,功能跨通道重构流程复杂,无法满足系统对多功能动态、实时不间断的重构需求,且在体积、重量和功耗方面比较大,不能满足综合传感器系统高度综合、任务可靠性、实时性的要求。

针对综合传感器系统高度综合化,功能重构不可间断的需求,提出了一种基于FPGA动态可重构技术的信号处理平台,利用FPGA局部可重配置特点,对有限的片内资源进行时分复用,功能波形在可重构区域中进行动态局部重配置,实现了多个功能波形在同一片FPGA芯片上分时重构,某个功能重构时不影响系统其他功能的使用,提高了综合传感器系统任务的可靠性和鲁棒性,同时降低了系统的功耗和体积,满足现代歼击机作战快速响应的需求。

2 架构设计

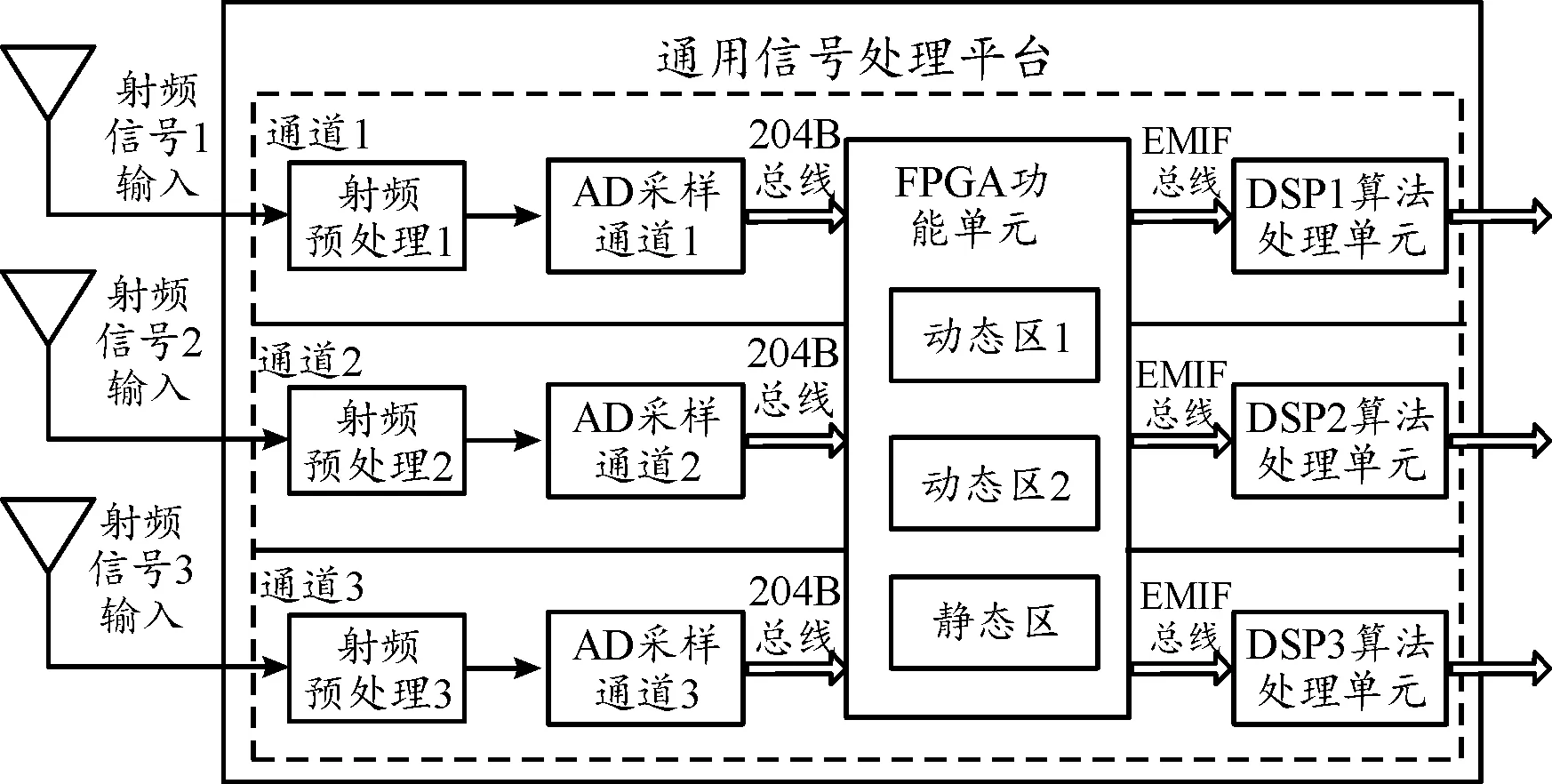

通用信号处理平台架构由3个独立的信号处理通道组成,如图1所示。每个信号处理通道包括:射频预处理单元、ADC采样单元、FPGA功能单元和DSP算法处理单元组成。射频信号(频率范围30 MHz~3 GHz)从天线端输入后,进过馈线传输进入射频预处理通道,通道内采用巴伦电路对射频信号进行预处理、放大和滤波,提取有用模拟信号送入ADC采样单元;ADC采集单元将该模拟信号转换为数字信号,并通过JESD204B总线传输给FPGA功能单元,利用JESD204B总线延迟固定、相位一致性的特点,保证了三路AD信号到后端FPGA功能单元的相位一致和数据同步。

图1 通用信号处理平台架构框图Fig.1 Architecture of general signal processing platform

数据处理部分主要包含FPGA功能单元和DSP算法处理单元。FPGA功能单元由3个动态区和1个静态区组成,主要实现AD数据解码、高速数据交换、外部射频组件控制,同时也负责功能波形的重构和加载。DSP算法处理单元实现功能波形的调制、解调、功能算法的实现等。

3 算法原理

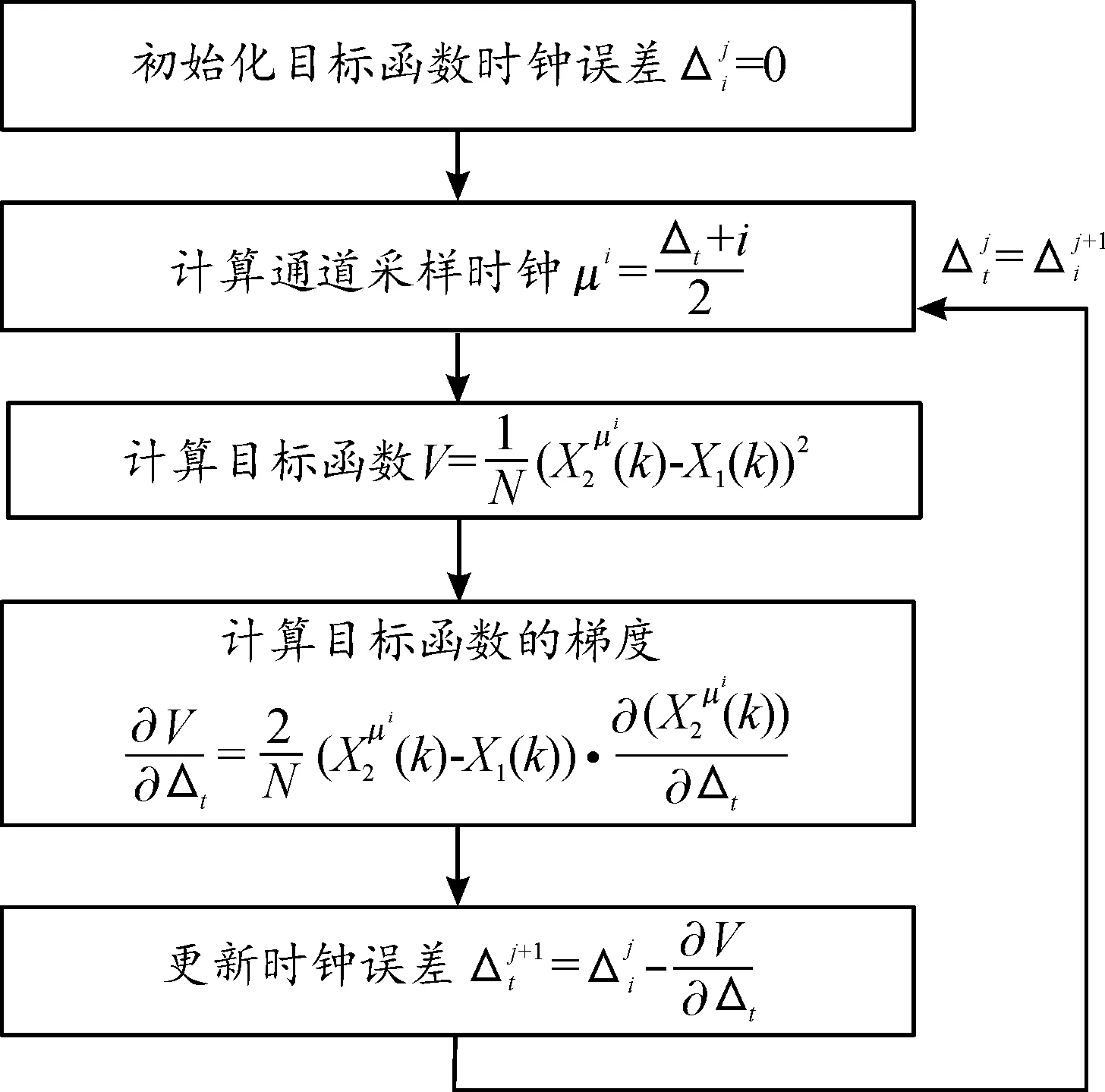

为了提高AD采样精度,信号处理平台采用时分交替AD构建,对多通道AD采样后数据进行误差校准,利用多片低速、高精度的ADC并行处理模拟输入信号,采用最小均方算法,在保证采样精度的前提下,不降低系统级采样速率,并行结构不需要增加单片设计的难度,就可以达到高速、高精度的系统采样,算法实现流程如图2所示。

图2 LMS算法流程框图Fig.2 LMS algorithm flow chart

LMS算法实现分为3个步骤,具体方法如下:

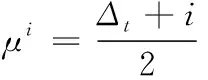

(1)

式(1)中:为当前时钟误差;为算法迭代次数。

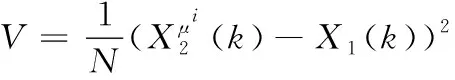

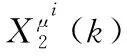

第2步,计算目标函数的梯度。根据式(2)计算出目标函数。

(2)

(3)

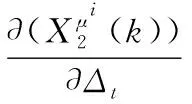

第3步,计算时钟误差。依据式(4)计算时钟误差。

(4)

重构滤波器H的频率响应为:

()=ej

(5)

式(5)中:为角频率;为时钟误差;为采样周期(1/100 M)。

4 硬件设计

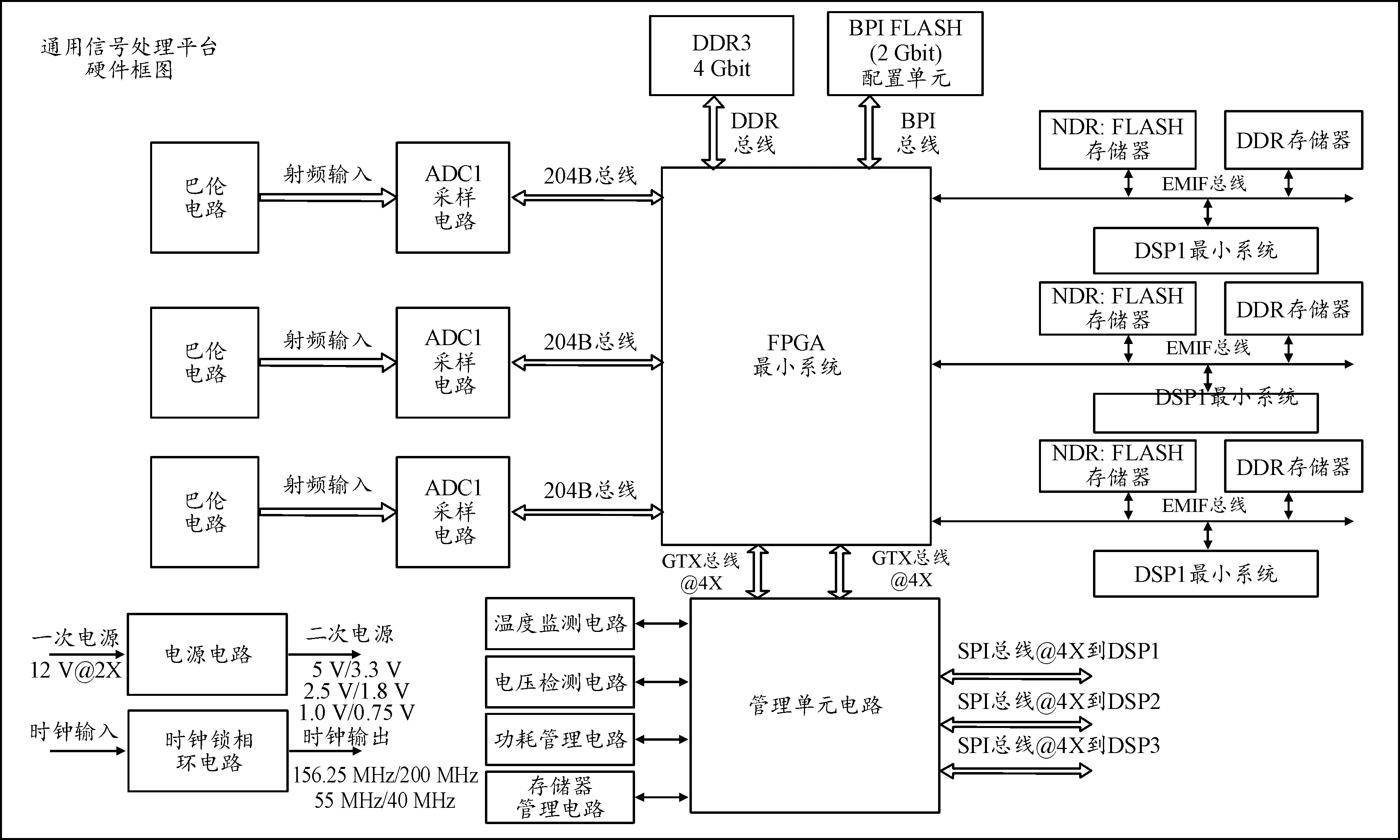

通用信号处理平台硬件架构如图3所示,射频信号经过巴伦电路处理后,进入ADC采样电路进行AD转换,转换后的数字信号经过JESD204B总线传输给FPGA最小系统。FPGA最小系统外挂4 Gbit的DDR3存储器、1 Gbit的BPI FLASH单元,实现FPGA程序加载和数据存储。FPGA最小系统通过EMIF总线与DSP最小系统进行数据交互,DSP最小系统外挂DDR3存储器和NOR FLASH存储器,实现功能算法的处理和数据缓存。管理单元电路实现板卡健康状态管理、电压监测、温度监测,功耗管理单元实现低功耗模式的控制,存储器管理电路实现板卡存储器资源的控制和分配管理,管理单元电路通过SPI总线与DSP最小系统进行数据交互。电源管理电路实现1级电源(电压为+12 VDC)到2级电源(电压为+5 V/3.3 V/2.5 V/1.8 V/1.0 V/0.75 VDC)的转换,控制各2级电源的上电顺序,时钟分/倍频电路实现输入时钟的分频、倍频,将输入的100 MHz时钟分/倍频至系统需要的频率。

图3 通用信号处理平台硬件架构框图Fig.3 Hardware architecture of general signal processing platform

由于AD输入频率范围要求宽(30 MHz~3 GHz),在硬件上设计了超低插损的巴伦电路,对输入单端射频信号进行预处理、匹配和滤波,选用Mini-Circuits公司的TC1-33-75G2+宽带巴伦芯片,频率范围从5 MHz到3 000 MHz满足设计要求。

经巴伦电路处理后的射频信号,送入ADC采样电路进行AD转换。ADC芯片采用TI公司的ADS54J60 进行设计。ADS54J60 是一款双通道、16位、1Gsps模数转换器,该器件内置缓存器和采样保存电路,是一款低功耗,小尺寸和易设计高速ADC。ADS54J60 采样数据通过JESD204B总线接口输出,JESD204B高速串行总线输出参数与接收通道的速率相匹配,并且通过SYSREF和SYNCB输入管理控制,提供多AD器件的同步设计。ADS54J60的采样时钟及同步采样时钟由JESD204B专用时钟芯片提供,本设计选用TI公司提供的HMC7044,该芯片为JESD204B总线提供专用时钟。

数据处理部分由FPGA最小系统和DSP最小系统组成,其中FPGA选择xilinx公司 Kintex UltraScale系列的XCKU085-2FLVA1517芯片,FPGA通过JESD204B总线接口接收ADC采样数据,并通过EMIF总线与DSP进行数据交互。DSP最小系统主要实现与FPGA通信、功能算法处理、数据缓存等功能,DSP采用TI公司的TMS320C6455BCTZA芯片,主频1 GHz、16 bit定点运算模式;管理单元电路选用复旦微公司的JFM7K325T8-AS芯片,通过SPI接口与DSP进行通信,完成板卡的健康状态管理、多版本程序切换控制等功能。

5 软件设计

5.1 软件架构设计

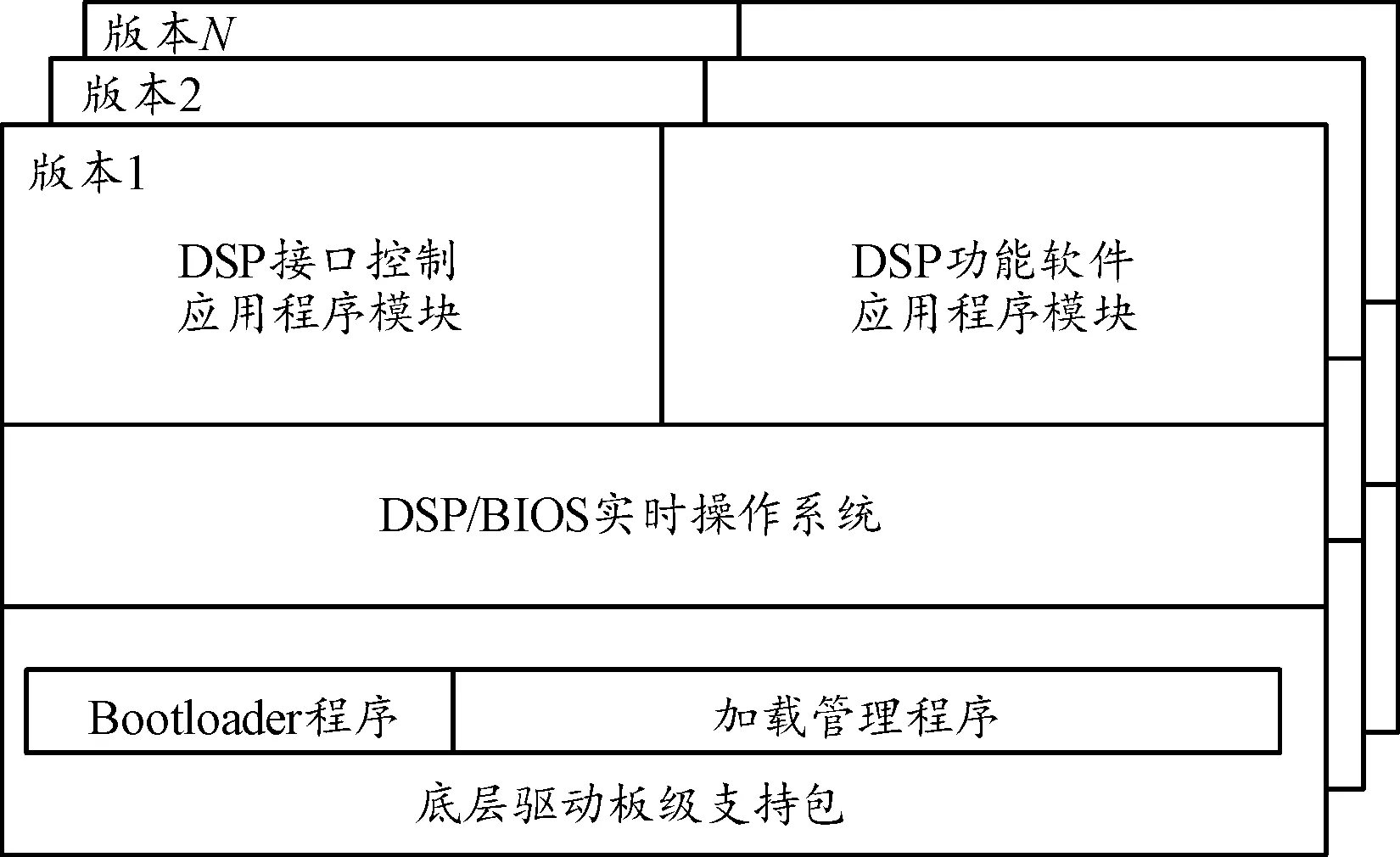

信号处理平台软件架构如图4所示。DSP采用多核AMP模式运行多个功能波形版本,每个功能版本由底层驱动板级支持包(包括Bootloader、加载管理程序)、DSP/BIOS实时操作系统、功能软件应用程序和接口控制应用程序组成。其中底层驱动板级支持包完成硬件平台初始化,注册底层硬件通信接口,在系统上电后底层驱动程序首先运行,并驻留在DSP片内ROM中,引导2个部分代码:Bootloader和加载管理程序。Bootloader主要完成系统上电后的管理程序加载,将管理程序载入DSP片内RAM上并执行。底层加载管理程序的任务是完成默认DSP和FPGA应用程序载入、信号处理功能模式切换、应用程序代码版本更新等工作,并提供控制程序跳转入口。DSP功能软件应用程序和接口控制应用程序,在DSP/BIOS实时操作系统的统一调度下运行,实现功能波形算法处理、数据处理、接口控制等工作。

图4 平台软件架构框图Fig.4 Platform software architecture

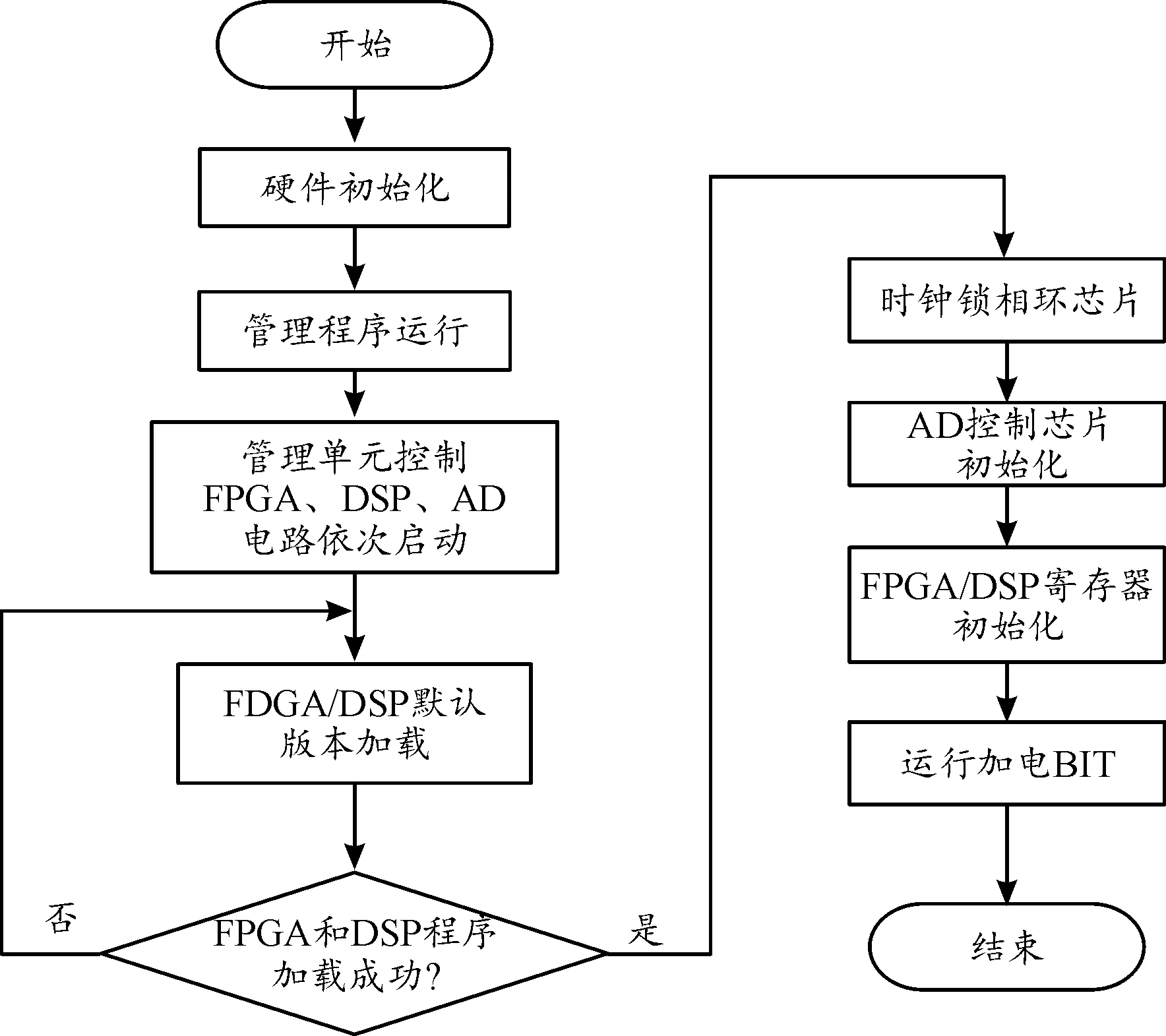

5.2 平台初始化流程

通用信号处理平台软件初始化流程如图5所示。模块加电后运行硬件初始化程序,完成底层硬件初始化。初始化完成后运行管理单元程序,管理单元程序控制各组电源按照预设的上电顺序进行启动,为保证平台正常运行,首先启动FPGA最小系统电路,等待FPGA启动完成后再启动DSP最小系统电路和AD电路,完成初始默认AD采样率、DSP工作模式的配置。模块启动完成后,管理单元控制FPGA和DSP加载默认版本加载,待程序加载成功后,管理单元控制完成时钟锁相环芯片的初始化,输出需要的采样率时钟;AD芯片的初始化,配置默认采样速率和精度;FPGA寄存器和DSP寄存器初始化,包括对外部接口、DDR控制器、GTH接口、SRIO接口、JESE204B接口初始化操作。待所有芯片初始化完毕后,自动执行加电BIT自检,自检结果上报,至此,模块初始化启动完成。

图5 通用信号处理平台软件初始化流程框图Fig.5 Software initialization process of general signal processing platform

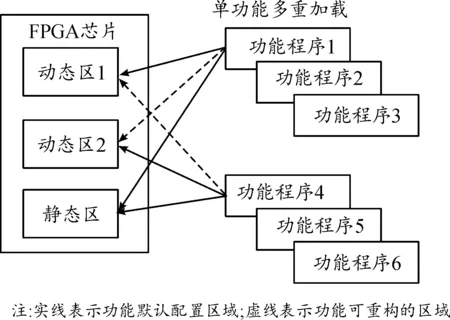

5.3 分区动态加载技术

FPGA分区动态加载技术,是一种分时复用有限的片内资源,对重构区域中的逻辑进行动态局部的重配置,以满足多功能、大规模应用的需求。如图6所示,通用信号处理平台将FPGA芯片分为动态区1、动态区2和静态区,其中静态区为固定的基础资源,包括IO接口、时钟配置、复位逻辑等资源,重构时静态区程序保持不变,功能程序在动态区1和动态区2上完成动态加载和重构,根据飞机作战任务需求加载不同的功能程序,且某个动态区进行功能版本切换时,不影响其他的动态区功能的正常运行,这样保证了系统在重构时功能的连续性和实时性。分区动态加载技术,一方面允许对FPGA指定区域使用新的程序进行重新配置,另一方面允许在器件的剩余空间继续运行当前的功能,这样做的好处是动态区1的功能重配置时,不影响动态区2的功能正常运行,保证了系统关键功能的连续性,也进一步扩展了FPGA固有的灵活性。

图6 FPGA动态区功能分布框图Fig.6 FPGA dynamic area function distribution

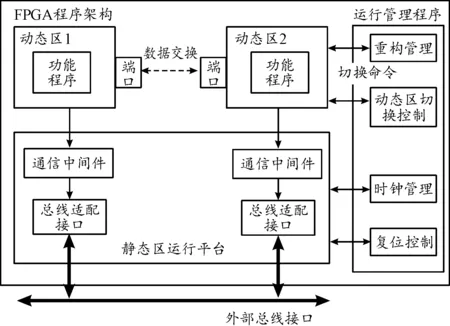

信号处理FPGA动态加载架构如图7所示,包括动态区程序、静态区程序和运行管理程序组成。依据系统应用需求,功能波形分别部署在动态区1、动态区2上,2个动态区间有通信进口,实现功能波形运行数据交换和处理。每个动态区通过通信中间件与静态区运行平台进行数据交换和控制,通信中间件实现了标准的通信协议,为功能与静态区平台通信提供了统一的平台,总线适配接口封装了底层通信的通用接口,包括SRIO接口组件、GTX组件、AD/DA组件、SPI控制组件等,为信号处理平台对外通信提供标准化的互联接口,实现平台通信方式与具体硬件的解耦,提高了平台的可移植性和通用性。

运行管理程序为基础的应用管理,包括重构管理组件和动态区切换控制组件,完成系统重构配置,动态区动态切换和管理。时钟管理组件为系统提供统一的时钟源,复位组件完成上电初始化复位操作,运行管理程序实现对动态区的实时监控和调度,实现平台动态化运行和管理。

图7 FPGA动态加载架构框图Fig.7 FPGA dynamic loading architecture

5.4 动态重构策略

动态重构是指在飞机不同作战任务或条件发生时,在系统控制调度下资源被不同的功能波形时分复用。重构能力是通用信号处理平台能力重要的指标,也是提高飞机系统任务可靠性的重要手段。作为系统的核心能力需求,动态重构技术是通用信号处理平台设计过程中必须突破的关键技术。重构设计分为任务重构和故障重构等2种。任务重构是指不同的飞行阶段,如起飞、巡航、作战和进场着陆等阶段,系统对通用信号处理功能波形需求不同,功能共享通用资源所进行的功能重构;故障重构是指当某一高优先级功能故障时,系统利用通用资源重建故障的高优先级功能波形,保证飞行任务中最关键任务的执行。

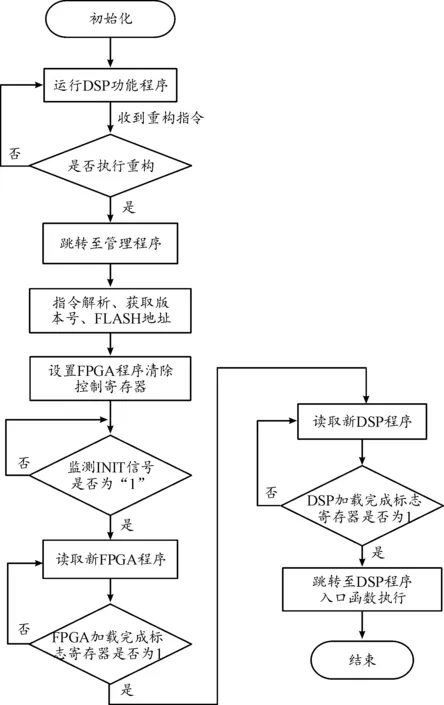

通用信号处理模块重构流程如图8所示,上电后首先完成初始化操作,运行DSP程序处理用户功能线程,当系统主机在需要对某个处理通道进行功能重构时,需要向DSP发送功能重构指令。DSP接收到该指令后,立即停止当前运行的用户程序,跳转到底层管理程序并开始执行。底层管理程序解析用户程序传递来的重构指令,获取重构的版本号、需要跳转的Flash地址,并从FLASH中查找对应的FPGA和DSP程序分别进行加载,完成FPGA功能波形加载,检测INIT信号是否为1,如果为1表示FPGA程序可以被加载,从BPI-Flash中读取FPGA程序并进行在线更新,更新完成后检测FPGA加载成功标识位,如果标识位为“0”加载失败,继续等待加载;如果标识位为“1”表示FPGA加载完成,即进入DSP程序加载流程,从DSP外置NOR-Flash中读取需加载的程序进行在线更新,更新完成后判断DSP程序加载成功标识位,如果标识位为“0”表示加载失败继续等待;如果标识位为“1”表示DSP程序加载完成,DSP重新跳转到功能波形入口地址处开始执行新加载的波形程序,信号处理通道完成了功能波形重构。

图8 功能重构策略流程框图Fig.8 Functional waveform reconstruction process

6 工程应用

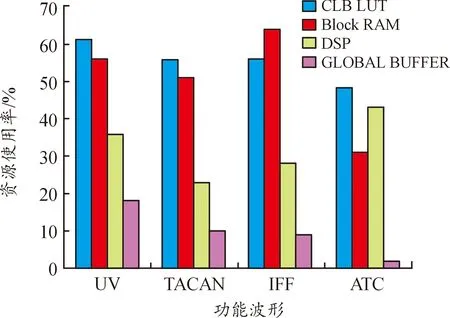

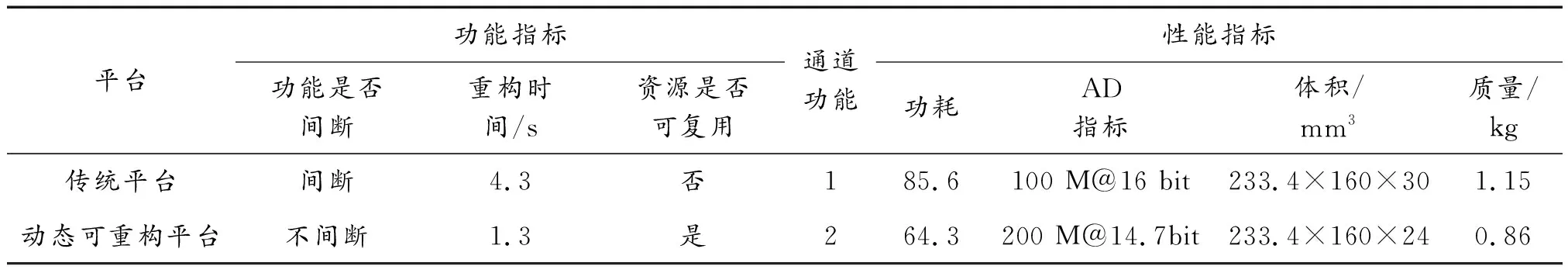

功能波形资源使用情况如图9所示。图9中列举了UV、TACAN、IFF、ATC等功能的资源使用情况,每个功能的资源使用量远小于FPGA片内资源总量,CLB LUT资源余度在30%以上。与文献[10]、文献[11]对FPGA整片资源进行刷新加载方式对比,本文中提出的波形重构方案,实现了FPGA片上资源分时复用,功能波形动态重构。动态可重构平台与传统平台指标如表1所示。

图9 波形资源使用情况直方图Fig.9 Statistics of waveform resource usage

从表1可看出,相对于传统的平台,本文提出的可重构信号处理平台,在重构时间、功能连续、资源复用、通道功能、功耗、体积、重量等方面有明显优势。改进的平台采用LMS算法,对2通道采样精度为16 bit,采样速率为100 MHz的AD数据进行校准,校准后有效精度提高到14.7 bit,系统级采样速率为200 M,大大提高了ADC的动态范围和信噪比。经外场飞行验证,在飞机的不同任务阶段,综合传感器系统内任意功能,如UV、TACAN、IFF、ATC等波形发生重构刷新时,不影响其他动态区功能。本平台实现了综合传感器系统功能波形在FPGA芯片级的重构和切换,能够满足综合传感器系统低功耗、小型化、综合化的需求,为系统功能集成提供了良好的运行平台。

表1 传统平台与动态可重构平台指标Table 1 Comparison of platform indicators

7 结论

提出了一种改进的机载综合传感器系统功能动态可重构技术信号处理平台。利用FPGA局部可重配置技术,对有限的片内资源进行分时复用,实现了功能波形在芯片级的重构和实时刷新,使综合传感器系统资源共享与功能重构灵活性与有效性统一。该平台可推广应用于航空、船舶、兵器等领域。